Навигация

Формализация АЛМ ремонта памяти

2.7 Формализация АЛМ ремонта памяти

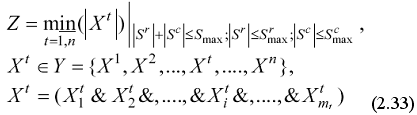

Функция цели определяется как минимизация резервных компонентов матрицы памяти (S – spare), необходимых для восстановления ее работоспособности в процессе функционирования цифровой системы на кристалле путем синтеза ДНФ покрытия дефектных элементов с последующим выбором минимального конъюнктивного терма ![]() , удовлетворяющего ограничениям по числу резервных строк и столбцов

, удовлетворяющего ограничениям по числу резервных строк и столбцов ![]() , входящих в состав логического произведения:

, входящих в состав логического произведения:

где каждый результирующий конъюнктивный терм функции Y составлен из идентификаторов строк и столбцов ![]() , покрывающих все дефекты в матрице памяти. Лучшее решение есть терм минимальной длины по Квайну, в котором содержатся как строки, так и столбцы, покрывающие все дефекты. В частности, решение может не содержать строк (столбцов), когда для ремонта памяти достаточно только существующих столбцов (строк) из резерва матрицы памяти. Модель процесса определения минимального числа резервных компонентов, покрывающих все обнаруженные дефекты в матрице памяти, сводится к следующим пунктам:

, покрывающих все дефекты в матрице памяти. Лучшее решение есть терм минимальной длины по Квайну, в котором содержатся как строки, так и столбцы, покрывающие все дефекты. В частности, решение может не содержать строк (столбцов), когда для ремонта памяти достаточно только существующих столбцов (строк) из резерва матрицы памяти. Модель процесса определения минимального числа резервных компонентов, покрывающих все обнаруженные дефекты в матрице памяти, сводится к следующим пунктам:

1. Преобразование двумерной модели дефектов матрицы памяти в таблицу покрытия дефектов резервными строками и столбцами матрицы.

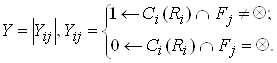

Для достижения поставленной цели рассматривается топологическая модель памяти в виде матрицы, идентифицирующей обнаруженные дефекты:

![]() (2.34)

(2.34)

Здесь координата матрицы отмечается 1, если функция исправного поведения ячейки на тесте дает единичное значение, то координата идентифицируется дефектной. После фиксации всех дефектов выполняется построение таблицы покрытия дефектов, ![]() где столбцы соответствуют множеству установленных дефектов m, а строки есть номера столбцов и строк матрицы памяти, которые имеют дефекты:

где столбцы соответствуют множеству установленных дефектов m, а строки есть номера столбцов и строк матрицы памяти, которые имеют дефекты:

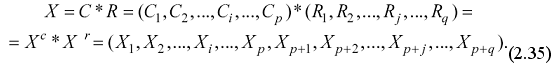

(2.35)

(2.35)

Вместо компонентов двумерной метрики C и R используется одномерный вектор, сконкатенированный из двух последовательностей C и R, мощность которого равна n = p + q:

При этом между элементами исходных наборов (C, R) и результирующим вектором Х существует взаимно однозначное соответствие, установленное в первом столбце матрицы Y. Следует заметить, что преобразование X = C * R выполняется лишь для удобства рассмотрения и последующего построения ДНФ в рамках единообразия переменных, формирующих булеву функцию. Если данную процедуру не выполнять, то функция будет определена на двух типах переменных, содержащих столбцы и строки матрицы памяти.

2. Построение КНФ для аналитического, полного и точного решения задачи покрытия.

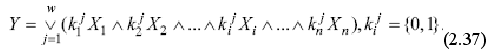

После формирования матрицы покрытия, содержащей нулевые и единичные координаты, выполняется синтез аналитической формы покрытия путем записи КНФ по столбцам. Здесь число конъюнктивных термов, равно количеству столбцов таблицы, а каждая дизъюнкция записывается по единичным значениям рассматриваемого столбца:

Из последнего выражения видно, что каждый столбец имеет только две координаты, имеющие единичное значение, а число логических произведений равно общему числу дефектов m, обнаруженных в матрице памяти.

3. Преобразование КНФ к ДНФ.

Данное преобразование даёт возможность увидеть все решения задачи покрытия. Для этого к КНФ необходимо применить операцию логического умножения и правила минимизации (поглощения) для получения ДНФ:

Здесь представлена обобщенная запись ДНФ, где в пределе число термов равно ![]() , n – число строк в обобщенном множестве (C, R) или количество переменных Х в матрице Y, на множестве которых формируются все решения – покрытия дефектов резервными компонентами; если

, n – число строк в обобщенном множестве (C, R) или количество переменных Х в матрице Y, на множестве которых формируются все решения – покрытия дефектов резервными компонентами; если ![]() при

при ![]() принимает значение нуля, то переменная

принимает значение нуля, то переменная ![]() превращается в несущественную.

превращается в несущественную.

4. Выбор минимальных и точных решений задачи покрытия.

Данный выбор связан с определением конъюнкций минимальной длины в полученной ДНФ. Последующее преобразование к строкам и столбцам матрицы памяти, на основе использования ранее введенного соответствия, даёт возможность записать минимальное покрытие или их совокупность в двумерной метрике строк и столбцов, отвечающие условиям (ограничениям) функции цели на количество резервных компонентов.

Далее предлагается иллюстрация модели процесса восстановления работоспособности матрицы памяти в части определения минимального числа резервных компонентов, покрывающих все дефекты. Матрица памяти с дефектами и резервом [11] представлена на рис. 2.3.

Матрица имеет ограничения на возможность диагностирования и восстановление работоспособности десяти дефектных ячеек, которые определяются двумя строками и пятью столбцами. В соответствии с пунктом 1 модели процесса определения минимального числа резервных компонентов, покрывающих все обнаруженные дефекты в матрице памяти, строится таблица покрытия десяти дефектов ![]() одиннадцатью строками, представленными в виде конкатенации подмножеств С и R, находящихся во взаимно-однозначном соответствии с вектором переменных Х:

одиннадцатью строками, представленными в виде конкатенации подмножеств С и R, находящихся во взаимно-однозначном соответствии с вектором переменных Х:

Далее, в соответствии с таблицей покрытия выполняется построение КНФ, термы которой записаны по единичным значениям столбцов.

Последующие преобразования, связанные с получением ДНФ основываются на применении законов и тождеств булевой алгебры, которые позволяют выполнить логическое перемножение всех десяти сомножителей, последующую минимизацию термов ДНФ путем применения оператора сограней, аксиом поглощения, исключения одинаковых термов. Опустив промежуточные вычисления, окончательный результат представим в следующем виде:

Выбор термов минимальной длины, содержащих 5 переменных, формирует множество оптимальных (минимальных) решений, имеющих вид:

![]() (2.41)

(2.41)

Трансформирование полученной функции к покрытию, содержащему обозначения переменных в виде строк и столбцов матрицы памяти, позволяет представить решения в следующей форме:

![]() (2.41)

(2.41)

Все полученные минимальные решения удовлетворяют требованиям по ограничениям на число резервных компонентов, определенных числами:

![]() (2.42)

(2.42)

Другие решения, определенные в ДНФ, не представляют интереса, поскольку они имеют неоптимальное покрытие дефектных ячеек, определяемое числом переменных (строки + столбцы) в термах более пяти. Последующая технология встроенного ремонта дефектных ячеек заключается в электрическом перепрограммировании дешифратора адреса столбца или строки матрицы памяти. Применительно к памяти, изображенной на рис. 2.3, процедура записи или считывания информации при обращении к любой ячейке столбца 2 будет переадресована к резервному столбцу 11. Соответственно последнему полученному решению в виде первого терма ДНФ функции Y, будут заменены и другие дефектные столбцы на исправные из резерва памяти: 3 – на 12; 5 – на 13; 7 – на 14, 8 – на 15.

Вычислительная сложность АЛМ восстановления работоспособности в части решения задачи покрытия определяется следующим выражением:

![]() (2.43)

(2.43)

где ![]() – затраты, связанные с синтезом ДНФ путем логического перемножения исключительно двухкомпонентных дизъюнкций (координата дефекта определяется номером строки и столбца), число которых равно количеству дефектных ячеек;

– затраты, связанные с синтезом ДНФ путем логического перемножения исключительно двухкомпонентных дизъюнкций (координата дефекта определяется номером строки и столбца), число которых равно количеству дефектных ячеек; ![]() – верхняя граница вычислительных затрат, необходимых для минимизации полученной ДНФ на предельном множестве переменных, равном суммарному числу строк и столбцов

– верхняя граница вычислительных затрат, необходимых для минимизации полученной ДНФ на предельном множестве переменных, равном суммарному числу строк и столбцов ![]()

В худшем случае, когда координаты всех дефектных ячеек по строкам и столбцам не коррелированы, – уникальны, например, диагональные дефекты, вычислительная сложность матричного метода становится зависимой только от числа дефектных ячеек, а ее аналитическая запись трансформируется к следующему виду:

![]() (2.44)

(2.44)

Если вместо мощности множества дефектов записать их число, равное m, тогда предыдущее выражение представляется в более простой форме:

![]() (2.45)

(2.45)

Согласно технологии встроенного сервисного обслуживания функциональных модулей цифровых систем на кристаллах, матричный метод восстановления работоспособности на основе решения задачи покрытия имплементируется в кристалл в качестве одного из компонентов I-IP (Infrastructure Intellectual Property), нацеленного на поддержание работоспособности матричной памяти SoC.

Выводы

SoC-микросхемы, в ближайшем будущем, будут составлять более 90% объема кристалла, ориентированного на использование гибких программных средств в ГАС.

Актуальной представляется разработка не только средств быстрого и точного диагностирования, но и создание технологий для осуществления ремонта дефектных ячеек, встроенными средствами сервисного обслуживания в реальном времени и на всех стадиях жизненного цикла изделия. Это позволит существенно уменьшить число выводов чипа, повысить выход годной продукции, уменьшить время выхода изделия на рынок, сократить затраты на сервисное обслуживание, а также исключить внешние средства диагностирования и ремонта.

В процессе написании квалификационной работы бакалавра, была достигнута поставленная цель работы, посредством выполнения следующих этапов:

рассмотрен АЛМ и, соответствующий ему, алгоритм встроенного диагностирования дефектов в функциональных блоках SoC, использующий предварительный анализ ТН в целях уменьшения её объема и последующих вычислений, связанных с построением ДНФ, формирующей все решения по установлению диагноза функциональностей SoC;

выполнена сокращенная инфраструктура сервисного обслуживания функциональностей SoC, отличающаяся минимальным набором процессов встроенного диагностирования в реальном масштабе времени и дает возможность осуществлять сервисы:

тестирование штатных функций на основе генерируемых входных последовательностей ATPG и анализ выходных реакций;

диагностирование с заданной глубиной поиска дефектов путем использования мультизонда стандарта IEEE 1500;

моделирование (Fault Simulation) неисправностей в целях обеспечения выполнения первых двух процедур на основе ТН FDT;

описана мэппинг-модель процесса синтеза дедуктивной структуры, отличающаяся использованием библиотеки дедуктивных компонентов, покрывающих все стандартизованные конструктивы функциональностей, которыми оперирует разработчик, что дает возможность создавать в автоматизированном режиме дедуктивную модель функциональностей цифровой системы на кристалле;

описана мэппинг-модель процесса синтеза тестов, отличающаяся использованием библиотеки встроенных тестовых генераторов для функциональностей DSP SoC, что дает возможность существенно уменьшить время построения тестов, предназначенных для верификации функциональностей и проверки дефектов.

АЛМ восстановления работоспособности памяти основывается на решении задачи покрытия дефектных ячеек резервными элементами путем использования аппарата булевой алгебры. Метод имеет квадратичную вычислительную сложность и может быть аппаратурно реализован как в программном исполнении за пределами кристалла, так и внутри него в виде дополнительного сервисного модуля коррекции дефектов, позволяющего автоматически выполнять восстановление работоспособности элементов памяти в процессе функционирования.

Также в работе рассмотрено априорное задание таблицы неисправностей в виде булевой функции, с точки зрения компактности, которая на конкретном ВЭП трансформируется в компактную запись, определяющую термы ДНФ, как все возможные решения неисправных компонентов, подлежащих ремонту.

Перечень ссылок

1. Хаханов В.И., Хаханова А.В., Литвинова Е.И. Алгебро-логический метод ремонта встроенной памяти SoC // Відмовостійкі системи. – №1. – 2008. – С. 99 – 109.

2. Хаханов В.И., Хаханова И.В. VHDL + Verilog = Синтез за минуты. Харьков: СМИТ, 2007. – 264 с.

3. Zorian Y. What is Infrustructure IP // IEEE Design & Test of Computers. – May – June 2002. P. 5 – 7.

4. Zorian Y., Gizopoulos D. Gest editors’ introduction: Design for Yield and reliability // IEEE Design & Test of Computers. – May – June 2004. – P. 177 – 182.

5. Rashinkar P., Paterson P., Singh L. System-on-chip Verification: Methodology and Techniques, – Kluwer Academic Publishers, 2002. – 393 р.

6. Хаханов В.И. Инфраструктура диагностического обслуживания SoC // Вестник Томского государственного университета. – №4(5). – 2008. – С. 74 – 101.

7. IEEE 1500 Web Site. [Электрон. ресурс]. – Режим доступа: – http: // grouper.ieee.org/groups/1500/.

8. Автоматизация диагностирования электронных устройств / Ю.В. Малышенко и др. / Под ред. В.П. Чипулиса. – М.: Энергоатомиздат, 1986. – 304 с.

9. Shoukourian S., Vardanian V., Zorian Y. SoC Yield Optimization via an Embedded-Memory Test and Repair Infrastructure // IEEE Design and Test of Computers. – 2004. – P. 200 – 207.

10. Zorian Y., Shoukourian S. Embedded-Memory Test and Repair: Infrastructure IP for SoC Yield // IEEE Design and Test of Computers. – 2003. – P. 58 – 66.

11. Парфентий А.Н., Хаханов В.И., Литвинова Е.И. Модели инфраструктуры сервисного обслуживания цифровых систем на кристаллах // АСУ и приборы автоматики. – Вып. 138. – 2007. – С. 83 – 99.

12. Hahanov V., Kteaman H., Ghribi W., Fomina E. HEDEFS – Hardware embedded deductive fault simulation // Proc. volume from the 3-rd IFAC Workshop, Rydzyna, Poland. – 2006. – P. 25 – 29.

13. Youngs L., Paramanandam S. Mapping and Repairing Embedded-Memory Defects // IEEE Design and Test of Computers. – 1997. – P. 18 – 24.

14. Bergeron J. Writing testbenches: functional verification of HDL models. –Springer, 2003. – 512 р.

15. DaSilva F., Zorian Y., Whetsel L. Overview of the IEEE P1500 Standard // ITC International Test Conference. – 2003. – P. 988 – 997.

16. Rossen K. Discrete Mathematics and its Applications. – McGraw Hill, 2003. – 824 p.

17. Бондаренко М.Ф., Кривуля Г.Ф., Рябцев В.Г., Фрадков С.А., Хаханов В.И. Проектирование и диагностика компьютерных систем и сетей. – К.: НМЦ ВО, 2000. – 306 c.

18. Zhong Y., Dropsho S.G., Shen X., Studer A., Ding C. Miss Rate Prediction Across Program Inputs and Cache Configurations // IEEE Trans. on Computers. – 2007. – P. 328 – 343.

19. Hamdioui S., Gaydadjiev G.N., Van de Goor A.J. The State-of-the-art and Future Trends in Testing Embedded Memories // Records IEEE Intern. Workshop on Memory Technology, Design, and Testing, San Jose, CA. – August 2004. – P. 54 – 59.

20. IEEE-1800. IEEE Standard for System Verilog Language. – 2005. – 586 p.

21. Densmore D., Passerone R., Sangiovanni-Vincentelli A. A Platform-Based taxonomy for ESL design // Design & Test of computers. – September – October 2006. – P. 359 – 373.

22. Методические указания к дипломному проекту для студентов специальности 8.091402 «Гибкие компъютерные системы и робототехника» Упоряд. В.В. Токарев, О.М. Цимбал. – Харьков: ХНУРЭ, 2003. – 40 с.

23. Державний стандарт України. ДСТУ 3008-95. Документація. Звіти у сфері науки і техніки. Структура і правила оформлення. Чинний від 01.01.96. – К.:Держстантдарт, 1995. – 60 с.

24. ГОСТ 2.105 – 2001. Единая система конструкторской документации. Общие требования к текстовым документам. – М.: Из-во стантдартов, 2001. – 76 с.

25. Единая система конструкторской документации: Справ. пособ. / С.С. Борушек А.А. Волков, М.М. Ефимова и др. - 2-е изд., перераб. и доп. – М.: Изд-во стандартов, 1989. – 352 с.

Похожие работы

... современным компьютерам, должна стать мощным усилителем мыслительных процессов в образовании. И здесь особая роль отводится преподавателям, которые являются носителями технологии образования и которые должны творчески переосмыслить накопленный интеллектуальный багаж в соответствии с новыми технологическими возможностями. До настоящего времени в российском обществе отсутствует четкое понимание ...

0 комментариев