Навигация

ПРОВЕРКА РАСЧЕТНЫХ ПАРАМЕТРОВ НА СООТВЕТСТВИЕ КОНСТРУКТИВНЫМ ТРЕБОВАНИЯМ

4. ПРОВЕРКА РАСЧЕТНЫХ ПАРАМЕТРОВ НА СООТВЕТСТВИЕ КОНСТРУКТИВНЫМ ТРЕБОВАНИЯМ

4.1 РАСЧЕТ ТАКТОВОГО СИГНАЛА

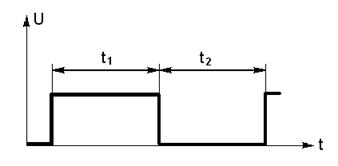

Временная диаграмма тактового сигнала представлена на рисунке 4.1.

Рисунок 4.1 Временная диаграмма тактового сигнала.

Устройство управления (триггеры регистра состояния) тактируются по фронту, а операционная часть – по спаду (тактовый сигнал на входы триггеров операционной части подаются через элементы 2И-НЕ). Таким образом, длительность активной фазы сигнала ![]() будет определяться быстродействием устройства управления, а фазы

будет определяться быстродействием устройства управления, а фазы ![]() – быстродействием операционной части и комбинационной схемы КС1.

– быстродействием операционной части и комбинационной схемы КС1.

Определяющим фактором длительности вычислений устройства управления является готовность управляющих сигналов. Поэтому интервал времени ![]() будет определяться временем задержки срабатывания схемы КС2, временем предустановки регистра и временем задержки регистра:

будет определяться временем задержки срабатывания схемы КС2, временем предустановки регистра и временем задержки регистра:

![]() .

(4.1)

.

(4.1)

Подставим в формулу (4.1) численные значения входящих величин, определенные выше:

![]() .

.

Наибольшее время для вычисления в операционной части потребуется в состоянии ![]() , так как в этом состоянии производится суммирование, требующее значительно больших затрат времени по сравнению с другими операциями. Интервал времени

, так как в этом состоянии производится суммирование, требующее значительно больших затрат времени по сравнению с другими операциями. Интервал времени ![]() будет определяться временем задержки логического элемента, инвертирующего тактовый сигнал, временем установки регистра RgY и временем формирования бита переноса в сумматоре:

будет определяться временем задержки логического элемента, инвертирующего тактовый сигнал, временем установки регистра RgY и временем формирования бита переноса в сумматоре:

![]() . (4.2)

. (4.2)

Подставив численные значения, получим:

![]() .

.

Теперь нетрудно определить период тактового сигнала:

![]() .

.

4.2 ОПРЕДЕЛЕНИЕ МАКСИМАЛЬНОГО ВРЕМЕНИ ВЫЧИСЛЕНИЯ

Максимальное время вычисления определим по формуле

![]() ,

(4.3)

,

(4.3)

где ![]() – максимальное количество тактов.

– максимальное количество тактов.

При умножении целых чисел методом последовательного суммирования максимальное количество тактов будет определяться величиной множителя Y. Для восьмиразрядного множителя при совмещении операций сложения и сдвига в один такт максимальным значением является восемь. Помимо этих 8 тактов понадобится один такт для начальной установки регистров и счетчика (состояние ![]() ) и еще один такт для установки сигнала READY по окончании счета. Следовательно, общее число тактов

) и еще один такт для установки сигнала READY по окончании счета. Следовательно, общее число тактов![]() , а максимальное время вычисления

, а максимальное время вычисления

![]() или

или ![]() .

.

Полученное значение меньше заданного ограничения 2 мкс.

4.3 ОПРЕДЕЛЕНИЕ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ

Потребляемая устройством мощность будет равна сумме мощностей, потребляемых всеми ее составными частями (регистры X и Z, счетчик, сумматор, схема сравнения, три логических элемента 2И-НЕ и устройство управления):

![]() . (4.4)

. (4.4)

Подставляя численные значения, получим потребляемую устройством мощность:

![]() .

.

Реальная потребляемая мощность оказалась меньше заданного ограничения 1000 мВт.

ЗАКЛЮЧЕНИЕ

В результате выполнения данного курсового проекта был разработан блок АЛУ для умножения двух положительных двоичных чисел. Все требования, оговоренные в техническом задании, были выполнены.

Разработанное устройство имеет по 8 входов для множителя Y0 – Y7 и множителя X0 – X7, вход разрешения начала счета START с активным уровнем "1", вход принудительного сброса с активным уровнем "1" и вход синхронизации с тактированием по фронту импульса; 16 выходов результата Z0 – Z15 и выход готовности результата READY с активным уровнем "1".

Максимальное время счета ![]() .

.

Потребляемая мощность ![]() .

.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

1. Курс лекций по дисциплине "Техническое обеспечение и внешние устройства ЭВС". / Под ред. А.В. Тютякина – ОрелГТУ, 2000.

2. Курс лекций по дисциплине "Расчет и конструирование элементов ЭВС". / Под ред. И.И. Неврова – ОрелГТУ, 2000.

3. Курс лекций по дисциплине "Аналоговая и цифровая электроника". / Под ред. А.А. Рабочего – ОрелГТУ, 1999.

Похожие работы

... nразъем = 135 резист = 0,05*10-6 час-1 nрезист = 3 общ = 344,1*10-6 час-1 Т = 2906,14 час Р = 0,6 ЗАКЛЮЧЕНИЕВ данном курсовом проекте был разработан процессор для ограниченного набора команд. Исходя из критерия проектирования, то есть максимального быстродействия блоки процессора построены на основе ТТЛШ технологии, на перспективных быстродействующих сериях, эти серии имеют ...

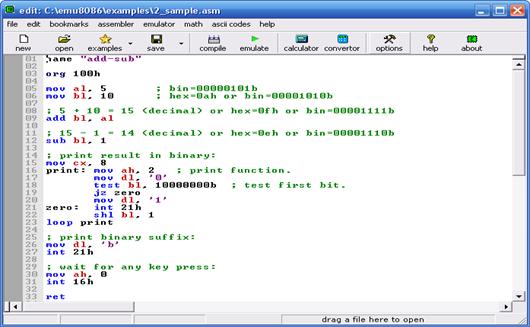

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

... . В случае выбора пункта «выход», необходимо реализовать завершение работы программы и передачу управления операционной системе DOS. 1.3. Требования техническим и программным средствам Программа выполнена на языке ассемблера 8086 процессора, соответственно ей необходим IBM PC – совместимый компьютер с процессором не ниже 8086, также программа может выполняться на компьютерах с ...

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

0 комментариев