Навигация

Перевірка розрахунку резисторів

6. Перевірка розрахунку резисторів

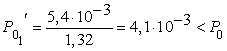

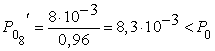

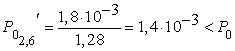

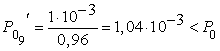

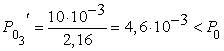

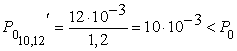

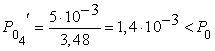

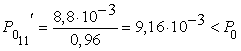

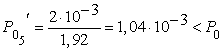

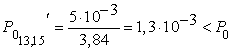

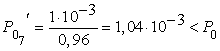

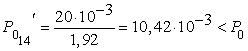

Для перевірки знаходять дійсну питому потужність і площу резистора. Резистор спроектований задовільно, якщо питома потужність розсіювання ![]() не перевищує припустимого значення Р0:

не перевищує припустимого значення Р0:

![]() (12)

(12)

Всі резистори спроектовані задовільно, так як питома потужність розсіювання ![]() не перевищує припустимого значення Р0.

не перевищує припустимого значення Р0.

6. Визначення розмірів плати

Площу плати, необхідну для розміщення топологічної тури ІС, визначають, виходячи з того, що корисна площа плати, що займається елементами, компонентами і контактними площадками, дещо менше її загальної площі, що обумовлено технологічними вимогами й обмеженнями. З цією метою приймають коефіцієнт використання плати КS, значення якого в залежності від складності схеми і засобу її виготовлення становить 2...3.

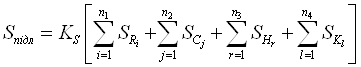

Загальна площа плати:

(13)

(13)

де n1 - кількість плівкових резисторів;

![]() - площа i-го резистора;

- площа i-го резистора;

n2 - кількість плівкових конденсаторів;

![]() -площа j-го конденсатора;

-площа j-го конденсатора;

n3 - кількість компонентів (навісних транзисторів, ІС, конденсаторів, діодів, резисторів, трансформаторів тощо);

![]() -площа r-го компонента;

-площа r-го компонента;

n4 - кількість контактних площадок;

![]() -площа l-ої контактної площадки.

-площа l-ої контактної площадки.

Площу, що займають компоненти, визначають за їхніми габаритними кресленнями і довідковими даними. Площа, що займається елементом, залежить також і від засобу його монтажу. Оскільки транзистори виконуються навісним монтажем, тобто S-транзистора не буде включена в загальну формулу підкладки, вони будуть розташовані на стрічці, яку приклеюють до підкладки:

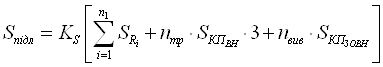

(14)

(14)

де ![]() площа резисторів;

площа резисторів;

![]() кількість транзисторів;

кількість транзисторів;

![]() площа внутрішніх контактних площадок;

площа внутрішніх контактних площадок;

3 – кількість виводів транзистора;

![]() кількість виводів мікросхеми;

кількість виводів мікросхеми;

![]() площа зовнішніх контактних площадок.

площа зовнішніх контактних площадок.

![]()

Розраховану площу плати заокруглюють до площі, найближчої з рекомендованого ряду (додаток А), що дозволяє орієнтовно визначити конструктивні ознаки корпуса ІС, за якими вибирають типорозмір придатного корпуса з числа нормалізованих.

Типорозмір №8.

Довжина l=16мм Ширина b=12 мм 16х12 мм

Остаточні розміри плати встановлюють після проектування топологічної схеми на етапі розробки конструкції ІС.

7. Розробка топології мікросхеми

Bибip форми i розміщення плівкових елементів i навісних компонентів проводить на основі комутаційної схеми, даних про форму, розміри підкладки, плівкових елементів i компонентів з урахуванням конструктивних, електричних i технологічних даних, вимог i обмежень. Послідовність дій при виконанні цього етапу повинна чітко визначатись i як правило, носити індивідуальний характер, заснований на досвіді розроблювача. Розробку топології - схеми розташування елементів на платі з урахуванням ycix вимог виконують у два прийоми: спочатку розробляють ескізний варіант топології, а потім - оригінал, елементи в пpoцeci їхнього розміщення на площі заданих poзмірів креслять на міліметрівці в масштабі 10:1 або 20:1. При цьому плівкові елементи повинні мати, як правило, прямокутну форму.

Елементи i компоненти розміщують у відповідності зi схемою комутаційних з'єднань, рекомендується послідовно-паралельний метод креслення, починаючи з групи елементів, розташованих в одному з кутів плати. Грані елементів і компонентів розташовують уздовж координатної сітки. Надання елементам форм, що складаються з відрізків прямих непаралельних осям координат, припустимо в тих випадках, коли це призводить до значного спрощення форми елемента.

При розміщенні необхідно ощадливо використовувати площу плати, дотримуючись при цьому обмеження у мінімально допустимих розмірах між елементами, компонентами і краєм плати.

Всі елементи і компоненти забезпечують контактними площадками, положення і розміри яких повинні відповідати конструктивно-технологічним вимогам і обмеженням. Розташування периферійних контактних площадок повинно відповідати виводам корпуса. Після остаточного розміщення елементів і компонентів зафарбовують кожний прошарок у різноманітні кольори або виконують різноманітне штрихування.

Якщо після розміщення всіх елементів залишилася значна незайнята площа плати, рекомендується перейти на менший розмір плати. Якщо розмір плати не змінюється і дозволяє її площа, то в останній варіант топології вносять зміни, щоб додати накресленим елементам більш простої форми, забезпечити зручність при проведенні складальних операцій, збільшити розміри контактних площадок і ширину провідників, розширити допуски на суміщення прошарків і збільшити відстані між елементами і т. ін.

Комутаційну схему розробляють на основі принципової електричної схеми, переліку елементів, загальних конструктивних вимог, спеціальних електричних i конструктивних вимог. До останніх частіше відносять вимоги по розташуванню контактних площадок (рознесення входу i виходу, порядок i місце розташування периферійних контактних площадок, а також вимоги по мінімізації проходження електричних сигналів i паразитних зв'язків між конкретними елементами i провідниками).

Звичайно застосовують такий порядок розробки комутаційної схеми:

1) із принципової схеми виключають уci навісні компоненти, а їхні виводи замінюють контактними площадками;

2) розташовують yci контактні площадки з максимальним урахуванням ycix схемотехнічних i конструкторських вимог (розташування виводів, розміщення транзисторів i т.д.);

3) розташовують інші елементи (зберігаючи їхнє схемне позначення), приєднуючи, їх до контактних площадок відповідно до принципової схеми;

4) аналізують отриману комутаційну схему з метою її спрощення i зменшення числа перетинань

Для зменшення числа перетинань плівкових провідників, що є потенційно слабкими місцями плівкової мікросхеми, використовують такі прийоми:

• переміщення перетинання в те місце схеми, де воно реалізується не у вигляді перетинання двох плівкових, а у вигляді перетинання плівкового i навісного провідників (периферійні контактні площадки розміщують на деякій відстані від краю, а між краєм підкладки i площадками прокладають плівкові провідники; пропускають плів корни провідник між контактними площадками, до яких приєднують виводи транзистора. Плівковий провідник у місці його перетинання з навісним провідником повинен бути покритий прошарком ізоляції;

• варіювання розташування навісних компонентів;

• деяке переміщення контактних площадок; у пpoцeci розробки комутаційної схеми контакті площадки можна нумерувати довільно. Контактні площадки нумерують остаточно після розробки топологиї; в при реалізації мікросхем на декількох платах раціональний розподіливши елементів між платами за принципом зменшення зв'язків між платами, але з урахуванням вимоги технологічності конструкції.

Спроектована топологія повинна:

1) відповідати принциповій електричній схемі;

2) задовольняти всі запропоновані конструктивні вимоги;

3) задовольняти всі технологічні вимоги і обмеження, обумовлений методом виготовлення;

4) забезпечувати можливість експериментальної перевірки електричних параметрів елементів схеми;

5) задовольняти усі висунуті електричні вимоги;

6) розташувати елементи на платі так, щоб забезпечити нормальну роботу схеми при заданому конструктивному виконанні і при заданих зовнішніх кліматичних впливах;

7)складатися таким чином, щоб для виготовлення мікросхеми застосовувалась найбільш проста і дешева технологія;

8) забезпечувати, по можливості, максимальне використання площі.

У тому випадку, якщо розрахунки показують значний вплив паразитних зв'язків або нагрівання мікросхеми вище допустимого рівня, у топологію вносять відповідні зміни.

Спроектована топологія відповідає принциповій електричній схемі підсилювача К2УС372. У ході проектування топології були дотримані всі технічні обмеження обумовлені товстоплівковою технологією виготовлення; поетапно були усунуті недоліки топології, що проектується, а саме перетини провідників, їх невиправдані перегини, не раціональне розміщення елементів. Топологія задовольняє всім конструктивним та електричним вимогам. Елементи розміщені на платі рівномірно і забезпечують роботу схеми.

У результаті коригування й уточнень ескізів топології був розроблений остаточний варіант топології - оригінал, що задовольняє вимогам. Топологічне креслення зображене у додатку Б.

Висновок

В результаті виконання курсової роботи було розроблено топологію підсилювача низької частоти К2УС372.

Для цього були розраховані геометричні розміри пасивних елементів (резисторів) з урахуванням їх опору та потужності; обрані матеріали резистивних плівок та перевірено правильність цього вибору.

Маючи значення розмірів резисторів та навісних компонентів (транзисторів) була підрахована площа підкладки ІМС з урахуванням зовнішніх та внутрішніх КП, яка становить

![]()

За розрахованим значення обрано 8-ий типорозмір підкладки згідно стандартам

(![]() )

)

Список літератури

1. Методичні вказівки до курсового проектування з дисциплін “Основи мікроелектроніки”, “Основи нано- та мікроелектроніки” для студентів спеціальностей 8.091001, 8.091003, 8.080402 денної форми навчання / Укл.: О.В.Андріянов, В.А.Мокрицький, - Одеса: „Наука і техніка”, 2004. – 64 с.

2. Аналоговые интегральные микросхемы: Справочник / Б.П.Кудряшов, Ю.В.Назаров, Б.В.Тарабрин, В.А.Убышев. – М.: Радио и связь, 1981. – 160с.

0 комментариев