Навигация

Выводы по аналитическому обзору

1.5 Выводы по аналитическому обзору

После проведения аналитического обзора и сравнительного анализа было решено, что :

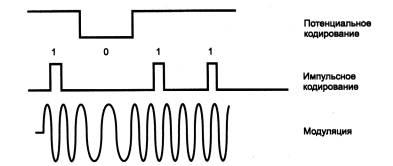

устройство кодирования-декодирования информации будем выполнять с использованием цифрового сигнального процессора;

весь алгоритм модуляции-демодуляции, передачи в порт ЭВМ, приёма из порта и т.п. выполняется программно под соответствующий DSP;

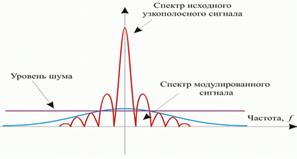

в качестве способа модуляции выбран метод частотной модуляции.

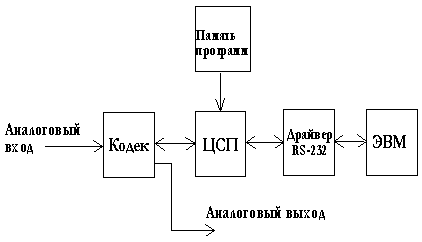

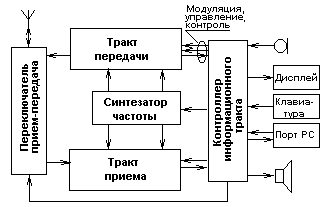

2. Разработка структурной схемы устройства

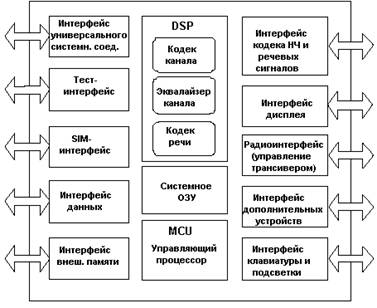

Составлять структурную схему устройства будем из основных функциональных блоков входящих в устройство.

Рисунок 2.1 - Структурная схема устройства

Описание структурной схемы:

Аналоговый вход

На вход устройства подается принятый по радиоканалу сигнал. Приемник сигнала из радиоканала нами рассматриваться не будет, но о наличие такового мы будем помнить. После попадания на вход устройства сигнал направляется в аналогово-цифровой кодер-декодер (кодек).

Кодек:

После фильтра низких частот сигнал поступает на кодер-декодер.

Кодек - это высокоскоростной чип, со встроенными аналого-цифровым и цифро-аналоговым преобразователями, последовательным портом, программируемым интервальным таймером, регистрами и т.п.

Кодек имеет определенную разрядность цифровых данных передаваемых по его последовательному порту. Разрядность должна совпадать с разрядностью DSP , а также частота дискретизации по теореме Котельникова, должна быть в два раза больше частоты сигнала.

Т.к. используется частотная модуляция и частота "1" = 1615 Hz и "0" = 1785 Hz. то, вполне достаточно выбрать 16-ти разрядный кодек, с частатой дискретизации 8 kHz.

Рассмотрим принципы АЦП и ЦАП преоразования, которые также используются в кодеке.

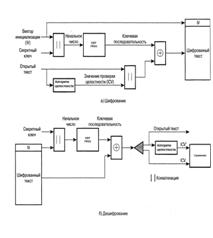

Физические сигналы являются непрерывными функциями времени. Чтобы преобразовать непрерывный, в частности, аналоговый сигнал в цифровую форму используются аналого-цифровые пребразователи (АЦП). Процедуру аналого-цифрового преобразования сигнала обычно представляют в виде последовательности трех операций: дискретизации, квантования и кодирования. Однако, если придерживаться терминологии принятой в литературе по системам цифровой связи, то первая операция, дискретизация, соответствует модуляции сигнала, а вторая операция, квантование, есть ни что иное, как один из cпособов кодирования. Поэтому процедуру аналого-цифрового преобразования сигнала можно также представить в виде последовательности двух операций - модуляции и кодирования.

Операция дискретизации заключается в определении выборки моментов времени измерения сигнала. Операция квантования состоит в считывании значений координаты сигнала в выбранные моменты измерения с заданным уровнем точности, а операция кодирования - в преобразовании полученных измерений сигнала в соответствующие значения некоторого цифрового кода или кодовой комбинации, которые затем передаются по каналам связи.

Процедуру восстановления непрерывного сигнала из цифрового представления также можно представить в виде двух операций: декодирования и демодуляции. Операция декодирования выполняет операцию обратную операции кодирования, т.е. преобразует последовательность заданных значений кодовой комбинации (кодовых слов) в последовательность измерений, следующих друг за другом через заданные интервалы времени дискретизации. Операция демодуляции выполняет интерполяцию или восстановление непрерывного сигнала по его измерениям. Преобразование сигнала из цифровой формы в непрерывный сигнал осуществляется цифро-аналоговыми пребразователями (ЦАП).

Итак, после поступления аналогового сигнала , кодек преобразует его в цифровой код, который по последовательному порту передается в цифровой сигнальный процессор (DSP), где по определенному алгоритму преобразуется и передается в ЭВМ.

При приеме цифрового кода от DSP, по своему последовательному порту, кодек преобразует его в аналоговый сигнал и передает на выход, где сигнал поступает на передатчик по радиоканалу (который не входит в наше устройство) и передается на другое такое же устройство.

Инициализация и настройка работы кодека, также как в DSP, осуществляется программно, что намного упрощает его точную настройку.

Цифровой сигнальный процессор (ЦСП или DSP):

Главной частью нашего устройства кодирования - декодирования информации является цифровой сигнальный процессор ( digital signal processor , DSP).

Цифровые сигнальные процессоры обладают огромными возможностями по цифровой обработке сигналов : спектральный анализ, цифровая фильтрация, преобразование частоты дискретизации, подстройка в реальном времени скорости воспроизведения и т.п.

3. Разработка схемы электрической принципиальной

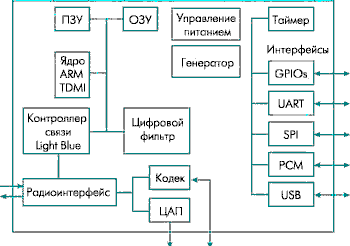

3.1 Выбор цифрового сигнального процессора

Цифровой сигнальный процессор (DSP) - является основой нашего устройства. Алгоритм кодирования - декодирования информации, прием и передача сигнала из ЭВМ и обратно, выполняются с помощью DSP.

Существует много различных фирм - производителей DSP: Texas Instruments, Analog Devices, Motorola , Philips и т.п. Реализацию нашего устройства можно выполнить практически с помощью DSP любой из перечисленных фирм. Рассмотрим цифровые сигнальные процессоры фирмы Analog Devices, и в частности сигнальный процессор ADSP - 2181.

Процессор ADSP-2181, является развитием семейства ADSP-21xx, 16-разрядных сигнальных процессоров DSP фирмы Analog Devices с фикси-рованной точкой. В ADSP-2181 используется базовая архитектура ядра этого семейства. ADSP-2181 обладает полным объемом внутренней памяти адресуемой на кристалле, расширенным набором внутренних периферийных устройств, высокой производительностью.

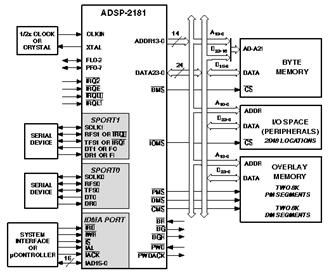

Краткая характеристика ADSP - 2181:

• 16 К x 24 бит внутренней памяти программ PM (Program Memory)

• 16 К x 16 бит внутренней памяти данных DM (Data Memory)

• 2 программируемых скоростных последовательных порта

• интервальный таймер

• 16-битный порт прямого доступа к внутренней памяти IDMA (Internal Direct Memory Access)

• 8-битный порт прямого доступа к внешней байтовой памяти BDMA (Byte Direct Memory Access) объемом до 4 Мбайт

• адресное пространство устройств ввода/вывода (2048 адресов)

• 4 сегмента по 8 К слов внешней оверлейной памяти

• внешние прерывания и программируемые выводы флагов

• режим пониженного энергопотребления (Pпот.< 1 мВт)

• расширенный набор инструкций

• производительность - 33.33 MIPS

• отдельный порт внутрисхемной эмуляции

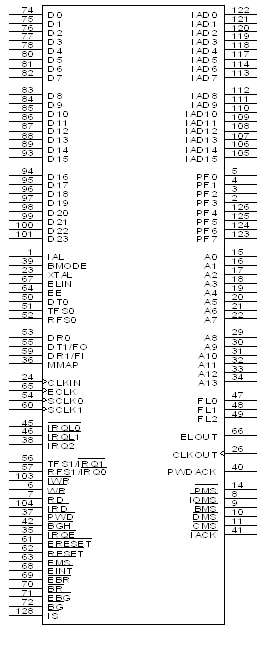

Рис. 3.1.1. Графическое изображение цифрового сигнального процессора ADSP - 2181

Дополнительные сведения о процессоре ADSP - 2181.

Тип обратываемых данных - с фиксированной точкой.

Тактовая частота - 16,67 MHz.

Время одного командного цикла - 30 nS.

Последовательный порт - 2

Параллельный порт - 2 ( 1(IDMA) - 8-битный или 16-битный, 1 - 24-битный)

Напряжение питания - 3V, 5V.

Рассмотрим назначение выводов и принцип работы процессора:

D0 ... D23 - 24-разрядная шина данных. Используется совместно с

шиной адреса для загрузки программы из внешней памяти в DSP.

A0 ... A13 - 14-разрядная шина адреса.

Память программ : ADSP-2181 содержит 16Kx24 ОЗУ программ на кристалле. Память программ позволяет выполнять до двух обращений в каждом цикле, тогда все операции могут завершаться за один цикл.

Память данных : ADSP-2181 имеет 16,352 16-разрядных слова внутренней памяти данных.

Пространство байтовой памяти - двунаправленное, 8-разрядное, внешнее пространство памяти, используемое для хранения программ и данных. Доступ к байтовой памяти осуществляется через BDMA. Пространство байтовой памяти состоит из 256 страниц, каждая из которых имеет размер 16К x 8.Это позволяет использовать до 4М x 8 (32 мегабит) ПЗУ или ОЗУ без дополнительной логики. Все обращения к байтовой памяти имеют временные параметры, определяемые регистром BMWAIT.

Контроллер прямого доступа в байтовую память (BDMA) позволяет осуществлять загрузку и сохранение команд программы и данных, используя пространство байтовой памяти. Схема BDMA способна обращаться к пространству байтовой памяти в то время, как процессор работает и захватывает только один цикл DSP для перемещения 8-, 16- или 24-разрядного слова.

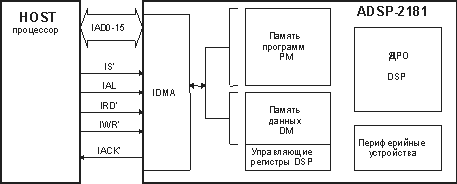

IAD0 ... IAD15 - 16-ти разрядная мультиплексированная шина данных/адреса порта IDMA.

Порт прямого доступа к внутренней памяти (IDMA) процессора ADSP-2181 является одним из новых устройств, существенно упрощающих построение интерфейса с HOST-процессором.

Рис. 3.1.2. Интерфейс работы порта IDMA с HOST-процессором.

Четыре входа управления IDMA предназначены для:

IS - выбор порта;

IAL - запись адреса ячейки памяти;

IRD - чтения данных через порт;

IWR - запись данных ;

IACK - Сигнал подтверждения доступа. Определяет завершение операций чтения/записи и готовность IDMA к следующей операции.

BMODE и MMAP

Выводы процессора BMODE и MMAP определяют режим загрузки и распределение (карту) памяти DSP. Для загрузки через внешнюю память BMODE=0 и MMAP=0. Загрузка состоит из следующих операций:

• Сброс процессора сигналом RESET

• Загрузка в Programm Memory и Data Memory кодов программы и данных, исключая ячейку PM(0x0000).

• Запись слова в ячейку PM(0x0000) для запуска загруженной программы.

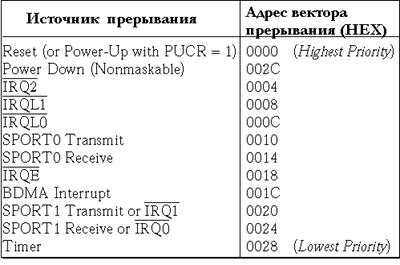

IRQ2, IRQL1, IRQL0 и IRQE. TFS1/IRQ1, RFS1/IRQ0.

Аппаратные входы прерываний. При подаче на них низкого уровня сигнала управление передается соответствующей подпрограмме

Таблица 3.1 - Таблица прерываний.

RESET - при получении низкого уровня сигнала передается управление подпрограмме инициализации DSP. При этом происходит повторная загрузка программы из внешней памяти в DSP.

PWD - (power down) отключение питания.

XTAL, CLKIN - на них подается тактовая частота от кварца. В нашем случае 16,67 MHz.

PMS, IOMS,

BMS, DMS , CMS - Данные выводы служат для подключения и управления оверлейной памятью.

Конфигурация оверлейной памяти задается установкой управляющего сигнала CMS в регистре программируемых флагов и составного сигнала управления (Programmable Flag and Composite Select Control). Также можно использовать оверлейную память, как память данных.

Так как шина адреса ADSP-2181 имеет только четырнадцать разрядов, то для расширения адресного пространства оверлейной памяти используются флаги FL0, FL1, а также FL2 или PMS в зависимости от требуемой конфигурации.

Рисунок 3.3 Системный интерфейс ADSP 2181

Выбранный нами цифровой сигнальный процессор ADSP - 2181 способен выполнять следующие действия:

| За один цикл процессор ADSP-2181 может: | Это происходит в то время как процессор продолжает: |

| - генерировать следующий адрес программы | - получать и передавать данные через два последовательных порта |

| - Выбирать следующую команду | - получать и/или передавать данные через внутренний порт прямого доступа в память |

| - выполнить одно или два перемещения данных | - получать и/или передавать данные через порт прямого доступа в байтовую память |

| - модифицировать один или два указателя адреса данных | - Декрементировать таймер |

| - выполнить вычислительную операцию |

Это полностью удовлетворяет нашим требованиям, для обеспечения требуемой модуляции и реализации метода кодирования NBDP. А также фирма Analog Devices поставляет со своими процессорами мощные программные продукты для отладки и записи программ в DSP, что делает данный цифровой сигнальный процессор еще более приемлемым для нас.

Похожие работы

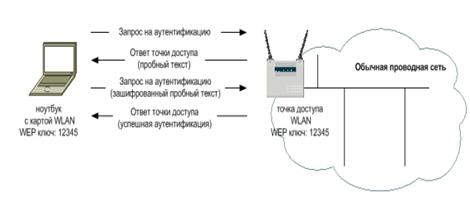

... части локальной сети не позволяют останавливаться на известных достигнутых результатах и побуждают на дальнейшее исследование в дипломной работе в направлении разработки локальной сети с беспроводным доступом к ее информационным ресурсам, используя перспективные технологии защиты информации. 2. Выбор оборудования, для перспективных технологий СПД 2.1 Выбор передающей среды Зачастую перед ...

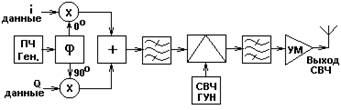

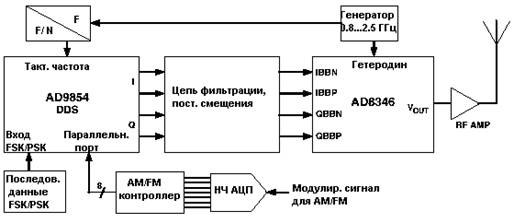

... телекоммуникаций может потребоваться не одна смена стандарта связи без смены комплекта приемо-передающей аппаратуры. Все это возможно в более сложных цифровых радиопередающих устройствах, построенных на основе специализированных цифровых процессоров передатчиков (TSP), которые будут рассмотрены в следующей главе. 2. Цифровые синтезаторы частоты с косвенным синтезом (ФАПЧ) Современные ...

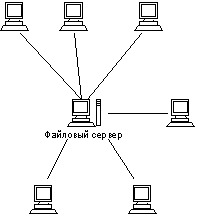

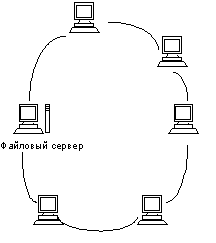

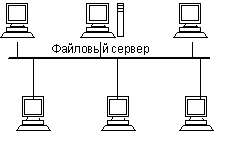

... сети также входит в физический уровень. Независимо от того, является ли сеть кольцевой сетью с маркерным доступом, звездоподобной сетью, или имеет гибридную конфигурацию, решение о топологии сети принимается с учетом физического уровня. В физический уровень также входит конфигурация кластеров высокой готовности. По большому счету нужно помнить о том, что если физические устройства не знают о ...

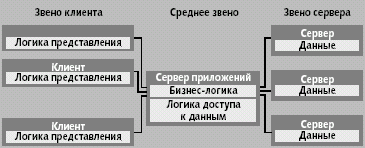

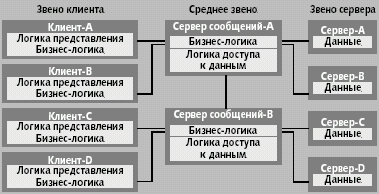

... на будущее. DAO и RDO известны уже достаточно давно, и появление двух разных механизмов было связано с необходимостью оптимизации решения двух отдельных задач: доступа к локальным и удаленным базам данных соответственно. Однако естественное развитие вычислительных систем привело к необходимости создания единого механизма, который обеспечил бы единый подход при работе с БД различных классов. В ...

0 комментариев