Навигация

Разработка арифметико-логического устройства

Содержание

Введение

1. Теоретическая часть

1.1 Описание основных параметров используемой серии логических элементов

1.2 Особенности использования выбранной серии логических элементов

2.Расчётная часть

2.1 Составление минимизированного логического выражения для формирования выходного сигнала А

2.2 Разработка функциональной схемы для формирования выходного сигнала А

2.3 Разработка принципиальной схемы для формирования выходного сигнала А

2.4 Разработка логического выражения и функциональной схемы для формирования выходного сигнала В

2.5 Разработка принципиальной схемы для формирования выходного сигнала В

2.6 Разработка принципиальной схемы для формирования выходного сигнала С

2.7 Расчёт и выбор элементов входных и выходных УСО

2.7.1 Расчёт и выбор элементов входных УСО

2.7.2 Расчёт и выбор элементов выходного УСО

2.8 Описание работы устройства

3. Конструкторская часть

3.1 Разработка чертежа принципиальной схемы. Выбор элементов схемы

3.2 Разработка сборочного чертежа. Выбор вариантов установки элементов схемы

Заключение

Введение

В настоящее время для повышения производительности труда и других параметров технологических процессов, а также для облегчения труда людей и количества занятых рабочих в процессе производства автоматизация этих процессов. С развитием техники, в частности с появлением интегральных микросхем значительно увеличились возможности реализации автоматизированных систем, уменьшились их габариты, стоимость, увеличилась надежность.

В современной технике наиболее широко используются интегральные микросхемы на основе логик ТТЛ, ТТЛШ, КМОП, ЭСЛ. Логические элементы и цифровые электронные устройства выпускаются в составе серий микросхем, которые характеризуются общими технологическими и схемотехническими решениями, уровнями электрических сигналов и напряжением питания. Каждая серия микросхем содержит самые разнообразные цифровые устройства, характеризующих набором параметров, дающих подробное представление об этой серии. При определении параметров ориентируются на логические элементы - простейшие устройства серии микросхем. Выбор производится не по параметрам серии логических элементов, а по параметрам логических элементов данной серии. К наиболее важным параметрам относятся: быстродействие - время распространения сигнала, напряжение питания, входные и выходные напряжения высокого и низкого уровня.

Цель курсового проекта - разработать функциональную и принципиальную схемы для арифметико-логического устройства, выполненного в виде печатной платы, при минимальном количестве логических элементов КМОП и простоте конструкции.

1. Теоретическая часть 1.1 Описание основных параметров используемой серии логических элементов

Основные параметры микросхем на основе КМОП - логики представлены в таблице 1.

Таблица 1 - Основные параметры микросхем на основе КМОП - логики

| Наименование | Параметры КМОП серий К561 и 564 |

| 1. Напряжение питания, UПИТ, В 2. Напряжение уровня логической единицы, U1, В 3. Напряжение уровня логического нуля, U0, В 4. Выходной ток нуля и единицы, I0,1, мА 5. Нагрузочная способность N 6. Потребляемый ток IПОТР, А 7. Время срабатывания tСРАБ, нс 8. Рассеиваемая мощность на элемент РРАС, мкВт | 3 … 15 ≥ 0,7 UПИТ ≤ 0,3 UПИТ 1 ≥ 100 IПОТР = IВЫХ 200 … 20 0,4 |

Быстродействие микросхем КМОП растет пропорционально увеличению напряжения питания. Входы КМОП не должны оставаться не присоединенными. Статическая рассеиваемая мощность составляет - 0,4 мкВт на элемент. Помехоустойчивость для элементов КМОП достаточно велика, так как допустимо снижение напряжения уровня логической единицы U1 до 30% от напряжения питания. Микросхемы КМОП могут работать от сигналов ТТЛ при подключении резисторов утечки от хода КМОП на питание ТТЛ 5В. Импульсная помехоустойчивость растет, если длительность входных импульсов помехи меньше, чем среднее время задержки распространения сигнала в микросхеме. Высокое быстродействие логических элементов КМДП-типа обеспечивается тем, что паразитные емкости перезаряжаются через открытые транзисторы.

Необходимые меры защиты элементов КМОП:

1. Все входные сигналы не должны выходить за пределы напряжения питания UПИТ.

2. Нельзя соединять выходы элементов непосредственно, так как произойдет замыкание одного из каналов на источник питания.

3. Недопустимо применение емкости нагрузки СН > 5000 пФ, поскольку незаряженный конденсатор равнозначен перемычке.

4. Не допускается замыкание выходов элементов КМОП с повышенным выходным током на проводе питания.

Достоинства КМОП микросхем по сравнению с ТТЛ микросхемами:

1. Малая потребляемая мощность в статическом режиме;

2. Очень высокое входное сопротивление;

3. Большая нагрузочная способность (> 100);

4. Большой диапазон напряжения питания (3 - 15В);

5. Малая зависимость характеристик от температуры.

Недостатки КМОП микросхем:

1. Повышенное выходное сопротивление;

2. Большие времена задержки (200 нс);

3 Большой разброс всех параметров.

2. Расчётная часть 2.1 Составление минимизированного логического выражения для формирования выходного сигнала А

Состояние выходного сигнала А в зависимости от входных сигналов a,b,c,d определяется по таблице истинности представленной в таблице 2.

Таблица 2 - Таблица истинности выходного сигнала

| a | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| b | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| c | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| d | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| A | 1 | 1 | 0 | 1 | Х | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

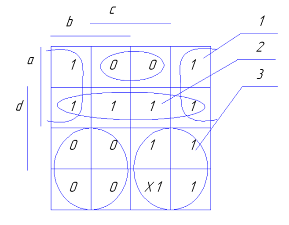

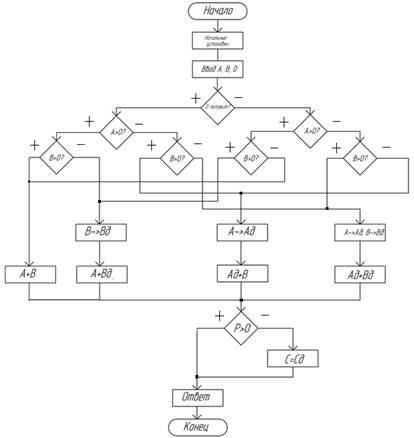

Более компактно таблицу истинности можно представить с помощью карты Карно. Контуры составляются по единицам. Карта представлена на рисунке 1. (X - принимаем 1.)

Рисунок 1 - Карта Карно

По полученным контурам составляется минимизированное логическое выражение для сигнала А.

Полученные логические выражения приводится к одной элементной базе на элементах И-НЕ при помощи правил Де Моргана.

![]() . (1)

. (1)

![]() . (2)

. (2)

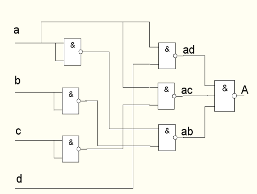

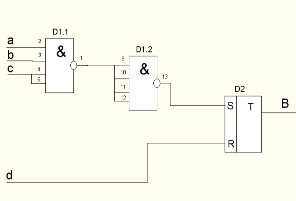

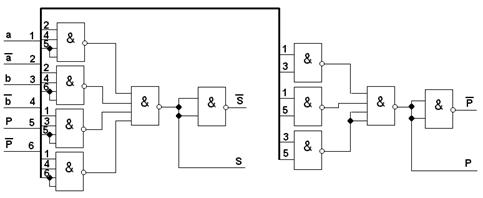

По выражению (2) составляется функциональная схема для формирования выходного сигнала А, которая представлена на рисунке 2.

Рисунок 2 - Функциональная схема для формирования выходного сигнала А

В полученной функциональной схеме на рисунке 2 используются одинаковые логические элементы. Функциональная схема, реализованная на элементах И-НЕ.

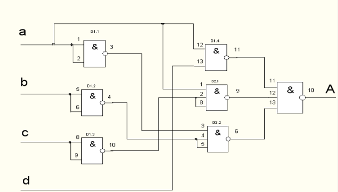

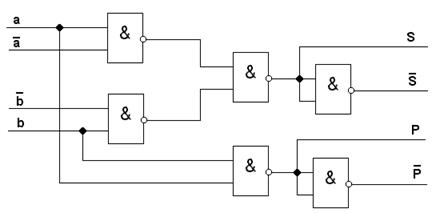

2.3 Разработка принципиальной схемы для формирования выходного сигнала А

Для реализации принципиальной схемы для формирования выходного сигнала А используются один корпуса микросхем К561ЛА7 и один корпус К561ЛА9. Для создания сигналов d, b и c используются соответственно нормально замкнутый контакт, нормально разомкнутый и перекидной контакт. С учётом их особенностей составляется принципиальная схема.

Рисунок 3 - Принципиальная схема для формирования выходного сигнала А

2.4 Разработка логического выражения и функциональной схемы для формирования выходного сигнала ВСостояние выходного сигнала В задано циклограммой, которая приведена на рисунке 4.

| a b c d B | |||||||||||||||||||||||||||||

Рисунок 4 - Циклограмма работы выходного сигнала В

Во включающем такте появляется входной сигнал "с" и присутствуют сигналы "а" и "b". Тогда условие срабатывания запишется: ![]() =abc. В отключающем такте исчезает входной сигнал "d". Условие несрабатывания будет:

=abc. В отключающем такте исчезает входной сигнал "d". Условие несрабатывания будет: ![]() =d.

=d.

Для получения окончательного выражения проведем проверки реализуемости:

1) Анализируем, существует ли записанное ранее условие срабатывания в течение всего периода включения.1-я проверка не пройдена, поскольку сигналы "а" и "b" изменяют свои значения в течение периода включения. Необходимо ввести промежуточный сигнал р`, чтобы он не изменял своё состояние до изменения состояния сигнала ![]() и в дальнейшем оставался неизменным (по крайней мере, до конца периода включения). Для исключения ложного срабатывания вводим сигнал p`=B. Для исключения ложного включения после исчезновения сигнала В примем комбинацию сигналов которая не повторится после исчезновения сигнала В. Итак конечное условие включения f`=abc+В.

и в дальнейшем оставался неизменным (по крайней мере, до конца периода включения). Для исключения ложного срабатывания вводим сигнал p`=B. Для исключения ложного включения после исчезновения сигнала В примем комбинацию сигналов которая не повторится после исчезновения сигнала В. Итак конечное условие включения f`=abc+В.

2) Анализируем, существует ли записанное ранее условие несрабатывания во время периода включения.2-я проверка пройдена, поскольку сигнал "d" не появляется в периоде включение, а это означает, что не произойдет ложное отключение сигнала. Вторая проверка пройдена.

3) Для того чтобы после отключения “B” не создалось условия для его повторного включения (ложные срабатывания) полученное логическое выражение для “B” преобразуют, раскрывая все скобки, в сумму произведений и проверяют, не встречается ли хотя бы одна комбинация сигналов в отключенном периоде.

![]()

Поскольку ни одна из этих комбинаций не встречается в отключенном периоде, то проверка пройдена.

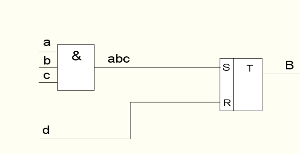

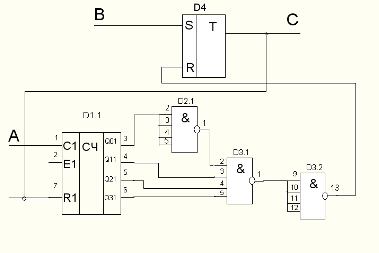

Описанному алгоритму работы выходного сигнала В соответствует функциональная схема, представленная на рисунке 5.

Рисунок 5 - Функциональная схема для формирования выходного сигнала В

2.5 Разработка принципиальной схемы для формирования выходного сигнала ВПри реализации принципиальной схемы на однотипных элементах И-НЕ используются один корпус микросхемы К561ЛА8 и один элемент корпуса К561ТР2. Принципиальная схема представлена на рисунке 6.

Рисунок 6 - Принципиальная схема для формирования выходного сигнала В

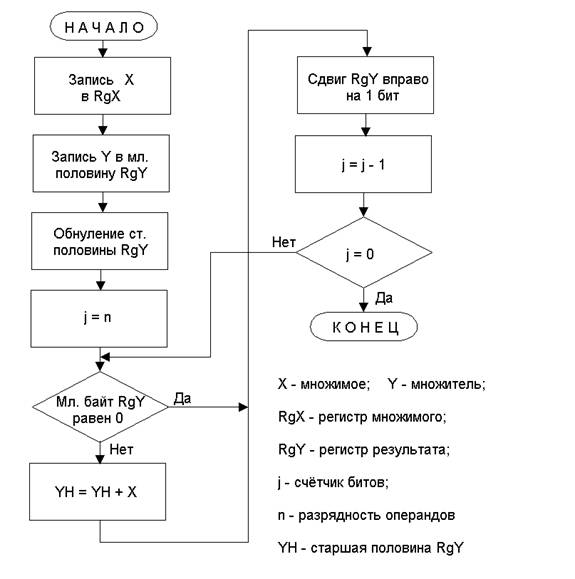

2.6 Разработка принципиальной схемы для формирования выходного сигнала СВыходной сигнал С появляется в момент появления сигнала В, а исчезает, когда число появлений сигнала А сравняется с числом 14. Число появлений сигнала А отслеживает счетчик и при появлении сигнала А 14 раз сигнал С исчезает и счетчик обнуляется. Для формирования выходного сигнала С используются микросхемы: К561ТР2, К561ЛА8, К561ИЕ10. Принципиальная схема представлена на рисунке7.

Рисунок 7 - Принципиальная схема для формирования выходного сигнала С

2.7 Расчёт и выбор элементов входных и выходных УСО 2.7.1 Расчёт и выбор элементов входных УСОК входным устройствам согласования с объектами (УСО) относится защита от дребезга контактов. Для создания сигналов d, b и c используются соответственно нормально замкнутый контакт, нормально разомкнутый и перекидной контакт. При замыкании контактов после касания подвижного контакта с неподвижным в силу упругих свойств подвижный контакт начинает вибрировать около неподвижного на протяжении 0,1 - 1мс. В релейно-контакторных схемах этот дребезг не оказывал существенного влияния на работу реле. В логических схемах логика успевает сработать. Это приводит к появлению “пачки” из нескольких десятков импульсов. Чтобы логика не реагировала на эти лишние импульсы используются УСО.

Похожие работы

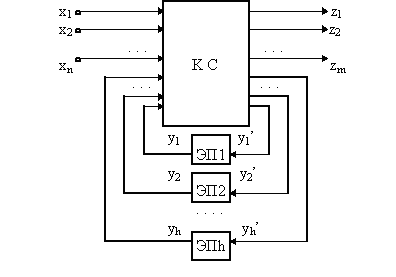

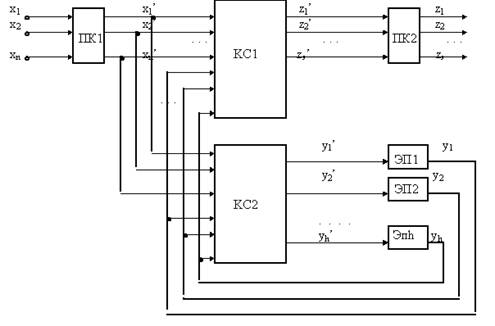

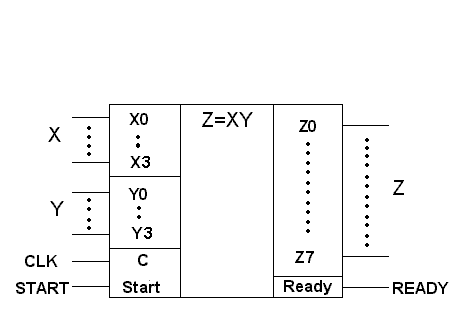

... переходов автомата. 3. Проектирование алгоритма и построение абстрактного автомата арифметико-логического устройства 3.1 Задание и исходные данные Разработка арифметико-логического устройства, выполняющего операцию сложения и вычитания в прямом двоичном коде. Исходные данные: – разрядность операндов – 8 бит; – разрядность результата – 8 бит; – элемент памяти – ПЗУ; – формат ...

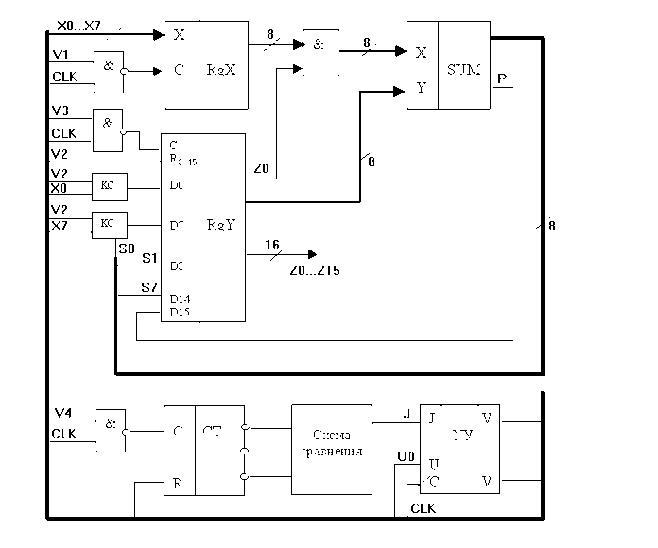

... RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре. Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел. Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме. 3 Синтез ...

... лекций. Основное внимание при выполнении курсового проекта обращается на умение принимать технические решения и обосновывать их. Объектом курсового проектирования является специализированное вычислительное устройство, включающее процессор и запоминающее устройство. Процессор проектируется для заданного списка команд и должен удовлетворять заданным требованиям технического задания. 2.Задание ...

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

0 комментариев