Навигация

Определение знака частного: 0Å0=0 2. Определения модуля частного

1. Определение знака частного: 0Å0=0 2. Определения модуля частного

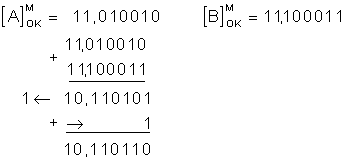

| № цикла | № такта | Наименование операции | Дей-ствие | Разряды частного | |||||||||||||||

| 0 | 1 | Вычит. делит. | А | 00 | 10011 | ||||||||||||||

| 2 | из делимого | [-B]д | 11 | 00111 | |||||||||||||||

| R0 | 11 | 11010 | 0, | 1 | 1 | 0 | 0 | ||||||||||||

| 3 | Восстановл. | +В | 00 | 11001 | |||||||||||||||

| 0-остатка | R1 1 | 00 | 10011 | ||||||||||||||||

| 1 | 1 | Сдвиг остатка | ¬ R1 | 01 | 00110 | ||||||||||||||

| 2 | Вычит. делит. | [-B]д | 11 | 00111 | |||||||||||||||

| формирование | R2 1 | 00 | 01101 | ||||||||||||||||

| разряда частн. | |||||||||||||||||||

| 2 | 1 | Сдвиг остатка | ¬ R2 | 00 | 11010 | ||||||||||||||

| 2 | Вычит. делит. | [-B]д | 11 | 00111 | |||||||||||||||

| формирование | R3 1 | 00 | 00001 | ||||||||||||||||

| разряда частн. | |||||||||||||||||||

| 3 | 1 | Сдвиг остатка | ¬ R3 | 00 | 00010 | ||||||||||||||

| 2 | Вычит. делит. | [-B]д | 11 | 00111 | |||||||||||||||

| формирование | 11 | 01001 | |||||||||||||||||

| разряда частн. | |||||||||||||||||||

| 3 | Восстан. ост. | +В | 00 | 11001 | |||||||||||||||

| R4 1 | 00 | 00010 | |||||||||||||||||

| 4 | 1 | Сдвиг остатка | ¬ R4 | 00 | 00100 | ||||||||||||||

| 2 | Вычит. делит. | [-B]д | 11 | 00111 | |||||||||||||||

| формирование | 11 | 01011 | |||||||||||||||||

| разряда частн. | |||||||||||||||||||

| 3 | восстановл. ост | +В | 00 | 11001 | |||||||||||||||

| 1 | 00 | 00100 | |||||||||||||||||

С=0,1100

Таким образом, цифры частного получаются как инверсное значение знаковых разрядов текущего остатка, которые принимают значение 00 или 11. Однако при сдвиге остатка влево в знаковых разрядах может возникнуть сочетание 01. В некоторых случаях, для того чтобы цифры частного формировались как прямое значение знакового разряда текущего остатка, деление выполняют с инверсными знаками. При этом делимое передается в сумматор не прямым, а инверсным кодом, а на нулевом шаге выполняется операция «+В», вместо операции «—В».

5.2 Деление без восстановления остатковРассмотренный способ деления с восстановлением остатков является аритмичным процессом с переменным числом шагов того или иного вида в каждом конкретном случае (3 шага при 2Ri < В и 2 шага при 2Ri>B). Для ритмизации процесса на каждую цифру частного необходимо затратить по 3 шага, в результате чего увеличивается время выполнения операции. Вместе с тем, операцию можно упростить и получить каждую цифру частного за 2 шага.

Рассмотрим случай, когда Ri <0. В предыдущем способе в этом случае выполнялись следующие операции.

Восстановление остатка:

R’і= 2 Rі +|В|=2 Rі-1-|B|+|B|=2 Rі-1

Сдвиг восстановленного остатка влево:

¬R'i = 2 R'i = 2 Ri-1 х 2 = 4 Ri-1.

Вычитание модуля делителя из восстановленного и сдвинутого влево остатка для определения следующего остатка:

Rі+1 =4 Rі-1-|B|

Если не восстанавливать остаток, а сразу сдвинуть отрицательный Rі на один разряд влево, то получим

R’і+1= 2 Rі =2(2 Rі-1-|B|)=4Rі-1 - 2 |B|.

Результат в данном случае отличается от действительного на величину + |B|. Поэтому в качестве второго шага необходимо произвести коррекцию результата на эту величину:

Rі+1 =4 Rі-1-2|B|+|B=4 Rі-1-|B|

В результате получаем требуемую величину последующего остатка Rі+1 , за 2 шага.

Таким образом, чтобы определить очередную цифру частного, необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак полученного таким образом следующего остатка и определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный - записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр.

Пример

Заданы А=0,101; В=0,110 [-B]доп= 11,010; |В|= 0,110

Похожие работы

... с их использованием, имеют свою устойчивую долю рынка. В данной курсовой работе на примере цифрового сигнального процессора семейства ADSP-21xx производится разбор команд умножения и деления, выполняемых в АЛУ. Обобщенная структурная схема персонального компьютера Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть построен на одной микросхеме (БИС,СБИС). ...

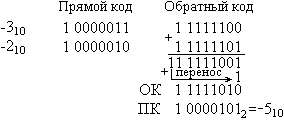

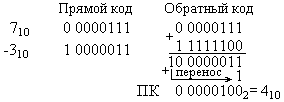

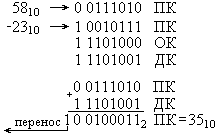

... нельзя рассматривать как единое целое. Кроме того, необходимо кроме сумматора иметь и вычитатель. В результате этого прямой код не применяется для выполнения операции алгебраического сложения, но применяется для выполнения операций умножения и деления. 1.1.3 Дополнительный код В дополнительном коде операция вычитания заменяется операцией алгебраического сложения. При этом знаковый разряд и ...

... позволит технически реализовать четыре действия арифметики в одном устройстве, называемом арифметико-логическом (АЛУ), используя одни и те же электрические схемы. 1.4.1. Представление чисел со знаками При выполнении арифметических операций в ЭВМ применяют прямой, обратный и дополнительный коды. Как уже говорилось выше, кодом называют такую запись числа, которая отличается от естественной и ...

... , связанный с формированием представлений о системно-информационном подходе к анализу окружающего мира, о роли информации в управлении, специфике самоуправляемых систем, общей закономерности информационных процессов в системах различной природы. Основой мировоззрения, главным его компонентом является научная картина мира, рассматриваемая как высший уровень систематизации и обобщения научных ...

0 комментариев