Навигация

2. Порядок виконання роботи

Ознайомилися з теоретичною частиною роботи, лабораторним стендом і програмою EWB.

Отримали від викладача елементи, необхідні для виконання роботи - мікросхеми К155ЛА3 (аналог 7400), К155ТМ2 (аналог 7474), К155 TB1 (аналог 7472), а також з’єднувальні провідники. Якщо для дослідження використовуємо моделююче середовище EWB, то п.п. 2.3 – 2.8 виконуємо на зарубіжних аналогах вказаних мікросхем (див. Додаток).

Ознайомилися з структурною і функціональною схемою та схемами комутації мікросхеми К155ТМ2 (рис. 1) і К155ТВ1 (рис. 2). При роботі в статичному режимі для контролю станів тригера до виходів підключили індикаторні світлодіоди (свічення світлодіода означає стан логічної "1"). Для дослідження D і JK-тригерів на інформаційні входи подавали сигнали з тумблерних регістрів, а на входи С – сигнал із формувача одиночних сигналів додатної полярності.

Дослідили в статичному режимі D-тригер (ІМС К155ТМ2). Склали таблицю переходів і переконатися на її відповідність таблиці 1.

Дослідили в статичному режимі Т-тригер на основі D-тригера (ІМС К155ТМ2). Для цього D-тригер перевели в режим роботи Т-тригера шляхом з’єднання інверсного виходу `Q з D-входом. Склали таблицю переходів. Таблиця станів відповідає таблиці 3.

Таблиця 3. Стани Т-тригера (мікросхема КІ55ТМ2)

| ВХІД | ВИХІД | Режими | ||||

| C | (D =`Qn) | `S | `R | Qn+1 | `Qn+1 | роботи |

| X | X | 0 | 1 | 1 | 0 | Асинхр. встановлення “1” |

| X | X | 1 | 0 | 0 | 1 | Асинхронне скидання в “0” |

| 0 | X | Х | Х | 0 (Qn) | 1(`Qn) | Пам'ять Qn+1=Qn |

| ↑↓ | 1 | 1 | 1 | 1 | 0 | Рахунок |

| ↑↓ | 0 | 1 | 1 | 0 | 1 | Рахунок |

Дослідили в статичному режимі JK-тригер (ІМС К155TB1). Склали таблицю переходів і переконалися на її відповідність таблиці 2.

Дослідили в статичному режимі Т-тригер на основі JK-тригера (ІМС К155ТВ1). Для цього JK-тригер перевели в режим роботи Т-тригера шляхом з’єднання всіх входів J (3“&”) і K (3“&”) з логічною 1 (+5В). Склали таблицю переходів. Таблиця станів відповідає таблиці 4.

Таблиця 4. Стани Т-тригера (мікросхема КІ55ТВ1)

| ВХІД | ВИХІД | Режими | |||||

| C | J (J1=J2=J3) | K (K1=K2=K3) | `S | `R | Qn+1 | `Qn+1 | роботи |

| X | X | X | 0 | 1 | 1 | 0 | Асинхр. встановлення “1” |

| X | X | X | 1 | 0 | 0 | 1 | Асинхронне скидання в “0” |

| 0 | X | X | Х | Х | 0 | 1 | Пам'ять Qn+1=Qn |

| ↑↓ | 1 | 1 | 1 | 1 | 1 | 0 | Рахунок |

| ↑↓ | 1 | 1 | 1 | 1 | 0 | 1 | Рахунок |

Дослідили в статичному режимі D-тригер на основі JK-тригера (ІМС К155ТВ1). Для цього JK-тригер перевели в режим роботи D-тригера шляхом з’єднання всіх входів J (3“&”) з всіма входами K (3“&”) через інвертор і в якості D-входу використали будь-який J-вхід.

(В якості інвертора використали 1-ий елемент 2”І-НІ” мікросхеми К155ЛА3 - ніжки 1 і 2 об’єднали). Склали таблицю переходів. Таблиця станів відповідає таблиці 5.

Таблиця 5. Стани D-тригера (мікросхема КІ55ТВ1)

| ВХІД | ВИХІД | Режими | |||||

| C | D (J1=J2=J3) | (K1=K2=K3) | `S | `R | Qn+1 | `Qn+1 | роботи |

| X | X | X | 0 | 1 | 1 | 0 | Асинхр. встановлення “1” |

| X | X | X | 1 | 0 | 0 | 1 | Асинхронне скидання “0" |

| X | X | X | 0 | 0 | --- | --- | Недопустимий режим. |

| 0 | X | X | 1 | 1 | Qn | `Qn | Пам'ять поперед.стану |

| ↑↓ | 1 | 0 | 1 | 1 | 1 | 0 | D=1 → Q= 1 і`Q =0 |

| ↑↓ | 0 | 1 | 1 | 1 | 0 | 1 | D=0 → Q= 0 і`Q =1 |

Висновок

В даній лабораторній роботі ми ознайомились з будовою спеціалізованих інтегральних мікросхемах D і JК-тригерів, здійснили синтез T-тригерів на їх основі та синтез D-тригера на основі універсального JК-тригера та дослідили їх роботу.

Література

1. Бабич М.П. і ін. Комп’ютерна схемотехніка. “МК-Прес”, Київ, 2004

2. Колонтаєвський Ю.П. і ін. Промислова електроніка та мікро схемотехніка: теорія і практикум. К.: Каравела, 2004.

Додаток. Схеми дослідження тригерів засобом моделюючої програми EWB

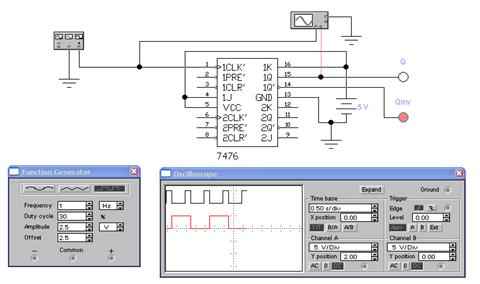

Рис.1. Дослідження синхронного JK тригера – динаміка (ІМС 7476 – аналог К176ТВ1).

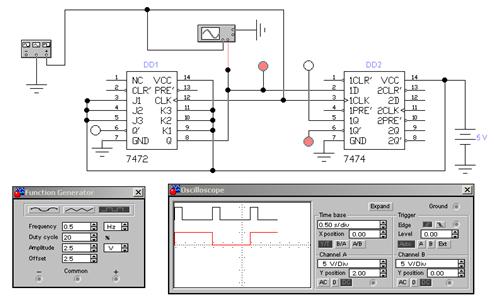

Рис.2. Дослідження синхронного JK і D тригерів – динаміка (ІМС 7474 – аналог К155ТМ2, 7472 – аналог К155ТВ1).

Похожие работы

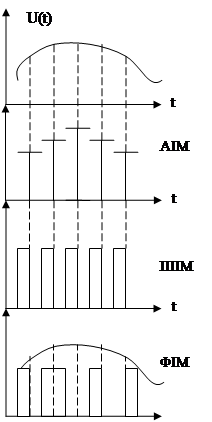

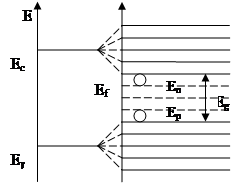

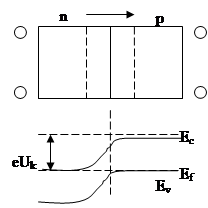

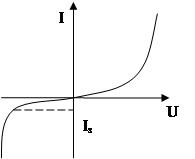

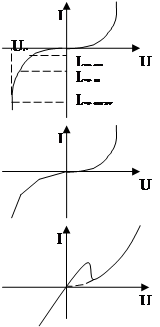

... і ключі реалізовані із зворотними зв’язками на діодах Шоткі. Це дозволило значно підвищити швидкодію схем і є зараз основою надвеликих інтегральних схем, які в свою чергу є базою всієї комп'ютерної електроніки. Окрім цього використовуються елементи емітерно-зв’язної логіки (ЕЗЛ) (на основі диференційних каскадів струмових ключів), n-, p- МОН логіка (на польових транзисторах) та комплементарна ...

0 комментариев