Навигация

4. Архітектура СМП

Для перерахованих вище типів МП існують поняття статичної й динамічної послідовності команд.

Статична - це впорядкована послідовність команд у пам'яті мікропроцесора.

Динамічна - безліч послідовностей інструкцій у порядку їхнього виконання, що відповідає динаміці налагодження програми. Динамічна структура програми може бути змінена, при незмінній статичній структурі. Це й дає підвищення ступеня паралельності виконання команд. При виконанні програми мікропроцесор як би просуває за статичною структурою програми вікно виконання. Команди в цьому вікні можуть виконуватися паралельно, якщо між ними немає залежності.

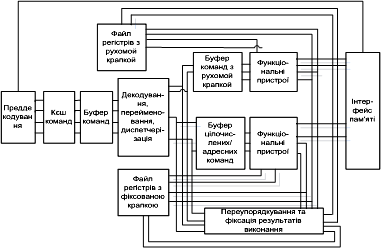

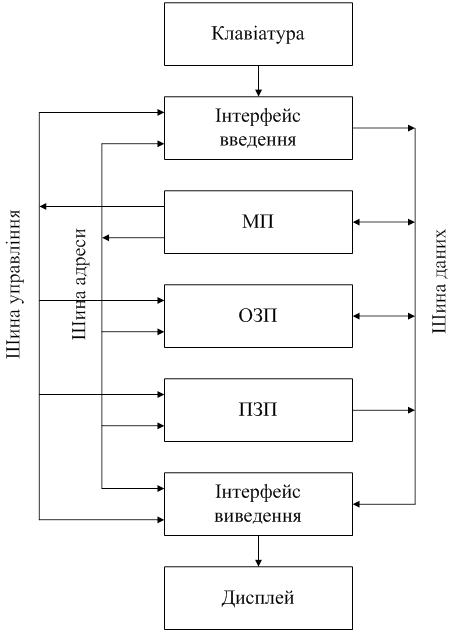

Малюнок 1. Архітектура суперскалярного мікропроцесора

5. Основні прийоми підвищення швидкодії в СМП Передвиборка команд і пророкування переходівБлок передвиборки команд витягає з пам'яті декілька команд за один такт мікропроцесора й тому особливі вимоги пред'являються до пропускної здатності інтерфейсу мікропроцесор-пам'ять. Для цього застосовуються багаторівневі роздільні кеш-пам'яті дані й кеш-пам'яті команд.

У блоці пророкування переходів використаються або додаткові біти в коді операції або переддекодування при виборі з кеш-пам'яті.

Декодування команд, перейменування ресурсів і диспетчеризація

На цьому етапі визначаються істотні залежності й переборюються несуттєві, виробляється розподіл команд по буферах функціональних пристроїв.

Для подолання зайвих залежностей, що виникають у результаті обмеженості логічних ресурсів, комірок пам'яті, регістрів використається механізм динамічного відображення логічних ресурсів на фізичні ресурси мікропроцесора.

Коли команда створює нове значення для фізичного ресурсу, він одержує ім'я. Дана процедура називається перейменуванням регістрів. Існують два основних способи перейменування:

1 - фізичний файл регістрів більше логічного. Зі списку вільних фізичних регістрів береться один і йому зіставляється відповідне логічне ім'я. Якщо список вільних регістрів порожній, диспетчеризація команд припиняється до моменту появи вільних фізичних регістрів.

2- фізичний файл регістрів дорівнює логічному файлу , але є один буфер, що використається для встановлення порядку виконання команд при перериваннях . Команди містяться в кінець буфера й після виконання її результат заноситься в заздалегідь певний елемент черги. Якщо команда досягла кінця буфера й була вже виконана, її результат міститься в регістровий файл, а сама команда вилучається. Не виконана команда перебуває в буфері до одержання необхідного їй операнда. Коли буфер заповнюється, диспетчеризація призупиняється.

Виконання командПісля формування для кожної команди впорядкованих трійок (коду операції, операнда-источника, операнда-приймача) і розміщення їх у буферах, наступає фаза динамічної перевірки готовності значень операндів для виконання команди.

Команда готова, як тільки готові операнди, але є ряд обмежень, пов'язаних з доступністю фізичних ресурсів (виконавчі пристрої, комутатори й порти регістрових файлів) і переупорядкуванням буфера. Для організації вікна виконання використаються різні методи:

1- Одна черга - перейменування регістрів не потрібно й доступність операндів відзначається бітом резервування в кожному регістрі. Регістр резервується, що коли модифікує його команда призначається на виконання й звільняється коли команда виконана;

2- Кілька черг - кожна черга організується для команд одного типу, команди роботи з FPU, робота з АЛУ, робота з пам'яттю;

3- Використання станції, що резервує. Вона складається з елементів, кожний з яких містить:

- код операції;

- найменування першого операнда;

- сам перший операнд;

- ознака доступності першого операнда;

- найменування другого операнда;

- сам другий операнд;

- ознака доступності другого операнда;

- найменування регістра результату.

Коли команда виконується, то найменування результату рівняється з операндом у результуючій станції, і, у випадку порівняння, установлюється ознака доступності результату. Коли в команди доступні всі операнди, дозволяється її виконання.

6 .Напрямок розвитку суперскалярної архітектури

При всіх перевагах суперскалярної архітектури принаймні дві обставини обмежують ефективність її використання.

По-перше, є обмеження на ступінь паралелізму на рівні команд, навіть якщо застосовується сама зроблена техніка суперскалярних обчислень. Перше обмеження виникає з умовних переходів. Друге з того, що розмір вікна виконання ( число активних команд, які можуть виконуватися паралельно) обмежує можливий програмі паралелізм, тому що не розглядається паралельне виконання команд, що перебувають на відстані, що перевищує розмір вікна.

По-друге, складність СМП зростає як кількість паралельна команд, що виконують, і навіть швидше. Орієнтовно межею є запуск на паралельне виконання 7-8 команд СМП.

Альтернативою суперскалярній обробці є використання довгого командного слова (VLIW). Використання цього методу припускає завдання в командному слові сукупності паралельно виконуваних команд. Підготовкою таких програм повинен займатися компілятор.

Переваги VLIW полягають у наступному:

- компілятор може більш ефективно досліджувати залежності між командами й вибирати паралельно виконуючі, чим це робить апаратури;

- є більш простий пристрій керування й можна мати більше високу тактову частоту.

Недоліки VLIW наступні :

- наявність команд розгалуження, які залежать від динаміки обчислень;

- VLIW - реалізація вимагає великого регістра пам'яті імен, багатовхідних регістрових файлів, великої кількості перехресних зв'язків.

Висновок

Крім VLIW-реалізації є перехід до мультипроцесорного виконання, коли вводиться кілька лічильників команд. Для цього необхідно наявність распаралелюючих компіляторів з мов високого рівня.

Література

1. Ю-Чжен Лю, Г.Гибсон Микропроцессоры семейства 8086/8088 М.: Радио и связь, 1987.

2. Б.В.Шевкопляс Микропроцессорные структуры. Инженерные решения М.: Радио и связь, 1990

3. В.Шевкопляс Микропроцессорные структуры. Инженерные решения. Дополнение первое. М.: Радио и связь, 1993

4. М.Гук Аппаратные средства IBM PC С.Петербург ²Питер² 2000

5. В.Корнеев, А.Киселев Современные микропроцессоры Санкт-Петербург ² БХВ – Петербург ² 2003

6. Локазюк В.М. и др Микропроцессоры и микроЭВМ в производственных системах Киев Издательский центр ² Академия ² 2002

7. Гуржий А.М. и др Архитектура, принципы функционирования и управления ресурсами IBM PC Харьков, 2003

8. В.В.Сташин, А.В. Урусов, О.Ф. Мологонцева Проектирование цифровых устройств на однокристальных микроконтроллерах Л. Энергоатомиздат

9. Под ред.А.Д.Викторова Руководство пользователя по сигнальным микропроцессорам семейства ADSP-2100 Санкт- Петербургский государственный электротехнический университет. Санкт- Петербург 1997

10. М.Предко Руководство по микроконтроллерам в 2-х томах М: Постмаркет, 2001

Похожие работы

... команд називається суперскалярною. Завдяки використовуванню даної технології і забезпечується додаткова ефективність в порівнянні з процесором 486. Суперскалярна архітектура звичайно асоціюється з мікросхемами RISC (Reduced Instruction Set Computer — комп'ютер із спрощеною системою команд). Процесор Pentium — одна з перших мікросхем CISC (Complex Instruction Set Computer — комп'ютер з складною ...

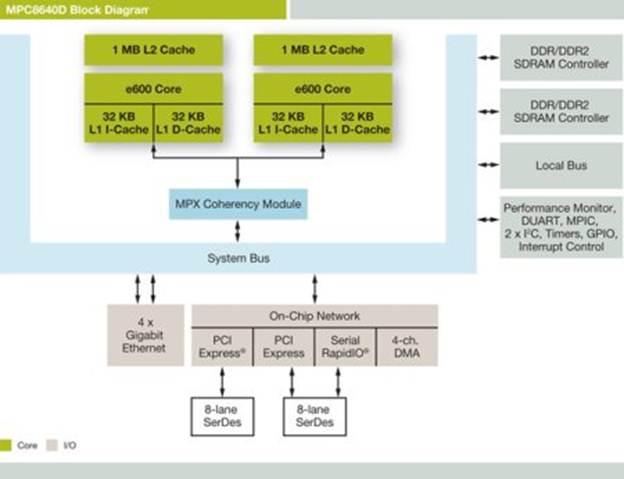

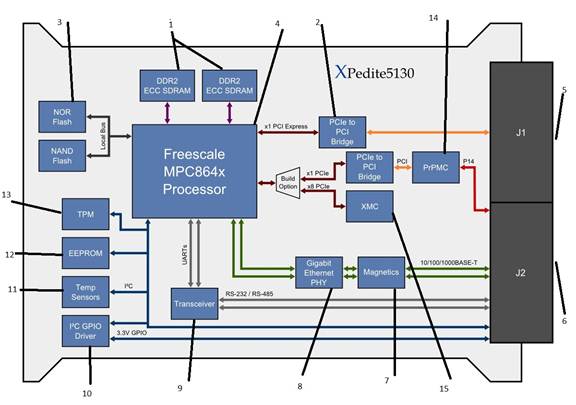

... , винайдена послідовність інструкцій, які зберігають всі модулі виконання максимально зайнятими на обох ядрах. 5. Ці числа живлення тільки для моделей MC8640Dwxx1067Nz і MC8640wxx1067Nz. VDD_Coren = 0.95 V і 1.2 Архітектура мікропроцесора MPC8640D Блок цього процесора включає в себе 2 ядра процесора та 1Мб кеш-пам’яті другого рівня (L2) (чотири блоки по 32Кб Cache SRAM). Високошвидкісна ...

обачив світло спрощений варіант процесора Pentium II, назва ,що отримала Celeron. В ньому вдвічі зменшений вторинний кеш і, немовби, прибрана підтримка багатопроцесорних систем. Однак шляхом “хірургічного” втручання підтримку багатопроцесорності можна повернути. Це пояснюється тим, що в Celeron застосоване ядро Pentium II без будь-яких змін. В 1999 році з'явився процесор Pentium III. В ньому ...

... "ВНІЇЕМ-3", а також надшвидкодіюча БЕСМ-6 з продуктивністю 1 млн операцій в секунду. 2.3 Третє покоління комп'ютерів Поява інтегрованих схем започаткувала новий етап розвитку обчислювальної техніки - народження машин третього покоління. Інтегрована схема, яку також називають кристалом, являє собою мініатюрну електронну схему, витравлену на поверхні кремнієвого кристала площею приблизно 10 ...

0 комментариев