Навигация

Микрооперация записи данных

3.2.2. Микрооперация записи данных.

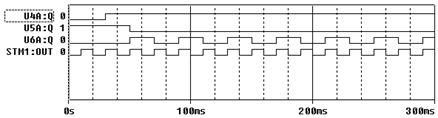

Когда операция записи данных разрешена, т.е. Y =1, и при подаче на синхровходы триггеров тактового импульса С по его заднему фронту, информация, находящаяся на входах триггеров, переписывается в ячейки памяти дискретного устройства и появляется на выходах Qi. При изменении входных данных, т.е. при переключении сигналов X i они с задержкой распространения импульса по цепям микросхем, участвующих в микрооперации записи данных, появляются на входах триггеров. При подаче следующего тактового импульса С микрооперация записи данных повторяется.

| X | Qt | Qt+1 | J | K | J | K | |||||

| 0 | 0 | 0 | 0 | * | X | X | |||||

|

| 1 | 0 | * | 1 | |||||||

|

| 0 | 1 | 1 | * | 0 | 1 | * | * | |||

|

| 1 | 1 | * | 0 | * | * | Qt | 1 | 0 | Qt |

![]()

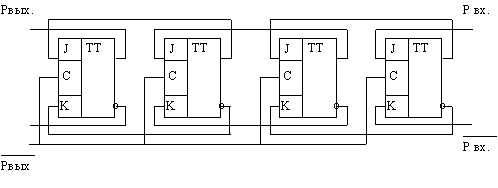

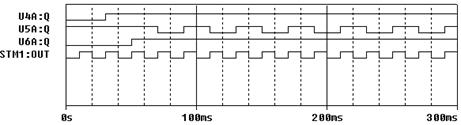

3.2.3. Микрооперация сдвига кода вправо на один разряд.

Когда Y =2, по заднему фронту тактового импульса информация со входов триггера поступает на их выходы, а затем осуществляется сдвиг кода, хранящегося в данный момент в ячейках памяти, в сторону старших разрядов т.е. вправо. При сдвиге каждый запоминающий элемент должен :

- передать хранимую информацию на элемент Ti+1

- изменить свое состояние за счет приема информации от триггера Т i-1 при сдвиге на один разряд вправо.

Передача от триггера Тi и изменение его состояния не могут проходить одновременно. В данном курсовом проекте эта трудность исключается за счет использования синхронных двухступенчатых JK-триггеров с динамическим управлением записью. Внутренняя организация таких триггерных схем предусматривает разделение во времени этапов приема входной информации и смены выходной. В них по переднему фронту синхронизирующего сигнала происходит прием информации, а по заднему - изменение состояния.

| Pi | Qt | Qt+1 | J | K | J | K | ||||

| 0 | 0 | 0 | 0 | * | Qt | Qt | ||||

| 0 | 1 | 0 | * | 1 | ||||||

| 1 | 0 | 1 | 1 | * |

| Pi | * | 1 | ||

| 1 | 1 | 1 | * | 0 | 1 | * |

![]()

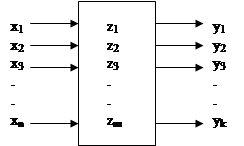

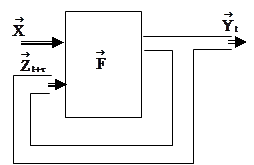

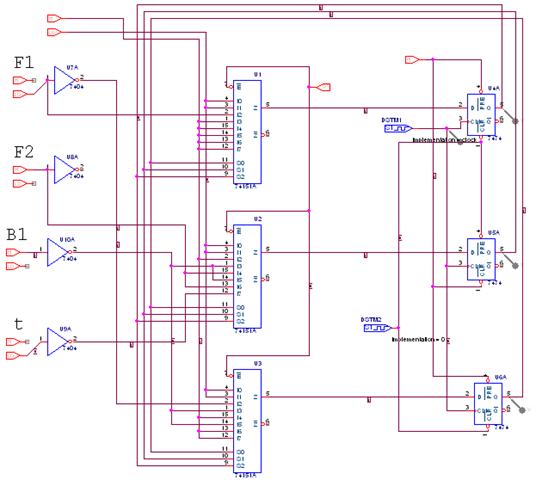

Схема цепи, реализующей данную операцию, изображена на рис. 3.3

рисунок 3.3

Похожие работы

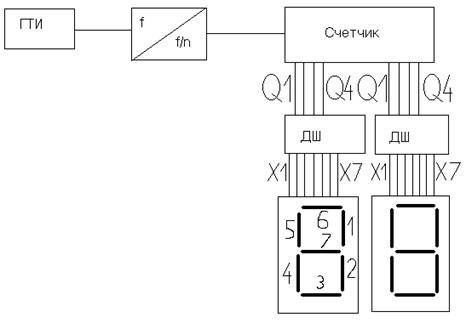

лиз сигналов и минимизация автомата. 3. Заключение. 4. Приложение. 5. Список литературы. Структурная схема. ГТИ - генератор тактовых импульсов. F/n - делитель частоты. 1. Проектирование дешифратора. В синтезируемом ДУ дешифратор расшифровывает значение выдаваемой в каждом состоянии счетной схемы кодовой комбинации, преобразуя ее в код, отображаемый на индикаторе в виде ...

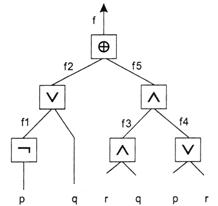

... ответ на этот вопрос положителен. Штрих Шеффера является отрицанием конъюнкции, стрелка Пирса – отрицание дизъюнкции, сумма Жегалкина – отрицание эквивалентности. М. Жегалкин (1869–1947) – российский математик и логик, один из основоположников современной математической логики. Чарльз Пирс (1839–1914) – американский логик, математик и естествоиспытатель. Основоположник семиотики, родоначальник ...

... в народном хозяйстве. Специальная часть. 3. 1. Определение задачи. Из задания на курсовое проектирование определим суть задачи: для некоторого синхронного цифрового автомата необходимо спроектировать устройство управления на основе жёсткой логики, которое в соответствии с заданными кодами микрокоманд формирует на выходной десятиразрядной шине управляющую последовательность цифровых сигналов. 3. ...

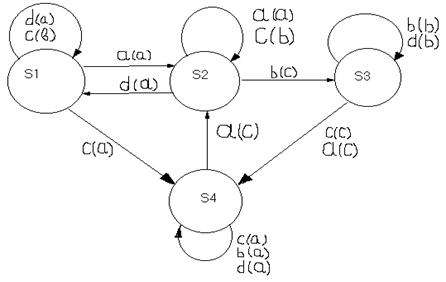

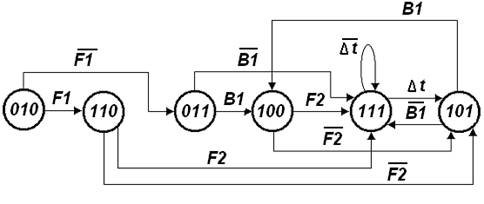

... автомата производится по приведенному в задании алгоритму. 2. Структурный синтез управляющего автомата 2.1 Построение направленного графа абстрактного автомата При проектировании устройства логического управления будем ориентироваться на синхронный дискретный автомат Мура, поскольку для асинхронного дискретного автомата опасен эффект состязания ("гонок"). Для исключения эффекта " ...

0 комментариев