Навигация

Микро ЭВМ на основе МПК - 1804

Проектирование микроЭВМ на основе микропроцессорного комплекта серии 1804

Введение.

Современный этап научно технического прогресса характеризуется широким применением электроники и микроэлектроники во всех сферах жизни и деятельности человека. Важную роль при этом сыграло появление и быстрое совершенствование элементной базы для разработки и проектирования различных периферийных устройств и устройств вычислительной техники.

Вычислительные машины и комплексы применяются в настоящее время практически во всех отраслях жизнедеятельности человека – связи и передачи данных, медицине и в быту, измерительных и контролирующих системах, в системах автоматического управления и многих других, где играют немаловажную роль и поэтому должны отвечать высоким требованиям, как точности, так и надежности.

Особую роль, с недавнего времени, стали играть и так называемые специализированные или бортовые компьютеры. Эффективность различных современных подвижных и стационарных систем зависит во многом и от их качества. Основное назначение этого класса вычислительных устройств – сбор самой различной информации, как о состоянии окружающей среды, так и возможно, о состоянии самого объекта, её обработка и передача более высокому звену управления объектом.

Процесс проектирования данного класса вычислительных устройств определяется целым рядом факторов, которые необходимо учитывать при построении такого устройства. Этими факторами могут служить:

степень подвижности объекта, несущего бортовой компьютер;

степень сложности алгоритмов вычислений, производимых им и их объем;

точность получаемых, обрабатываемых и выходных данных.

Обычно функционирование таких вычислительных устройств происходит не автономно (хотя не исключён и такой вариант), а под управлением различных более мощных и стационарных объектов или комплексов. В связи с эти сложность разработки структуры и программного обеспечения к таким устройствам требует существенных временных и материальных затрат.

Область применения подобного класса вычислительных устройств можно сказать всеобъемлющая. Практически на любом подвижном объекте возможно (или даже просто необходимо) применение бортового компьютера, который может предоставлять оператору или управляющему устройству – человеку или машине, данные об объекте управления или даже самостоятельно принимать какие-либо решения. Необходимо также сказать, что применение таких вычислительных устройств уже достаточно широкое, что доказывает перспективность их дальнейших разработок и применения в жизни.

1. Разработка архитектуры микрокомпьютера.

1.1 Проектирование алгоритмов, выбор состава макроопераций, проектирование задач.

При реализации данного курсового проекта проектируемая микро ЭВМ должна была решать следующие задачи:

· выполнение арифметической операции ![]() , где

, где ![]() (

(![]() - содержимое портов);

- содержимое портов);

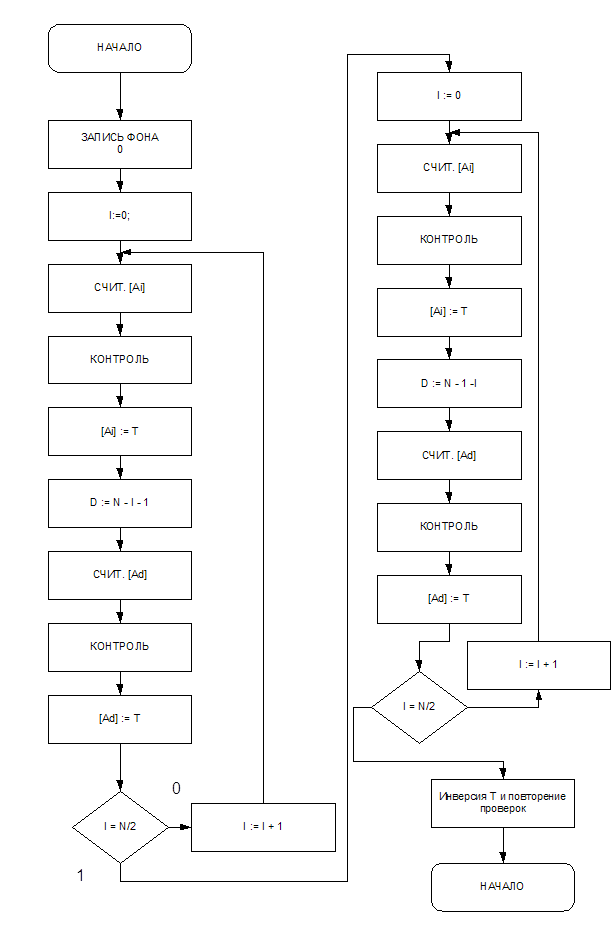

· тест ОЗУ методом “Обращение по прямому и дополняющему адресам”;

На основании этих самых алгоритмов была выбрана система команд проектируемой микро ЭВМ (система микроопераций).

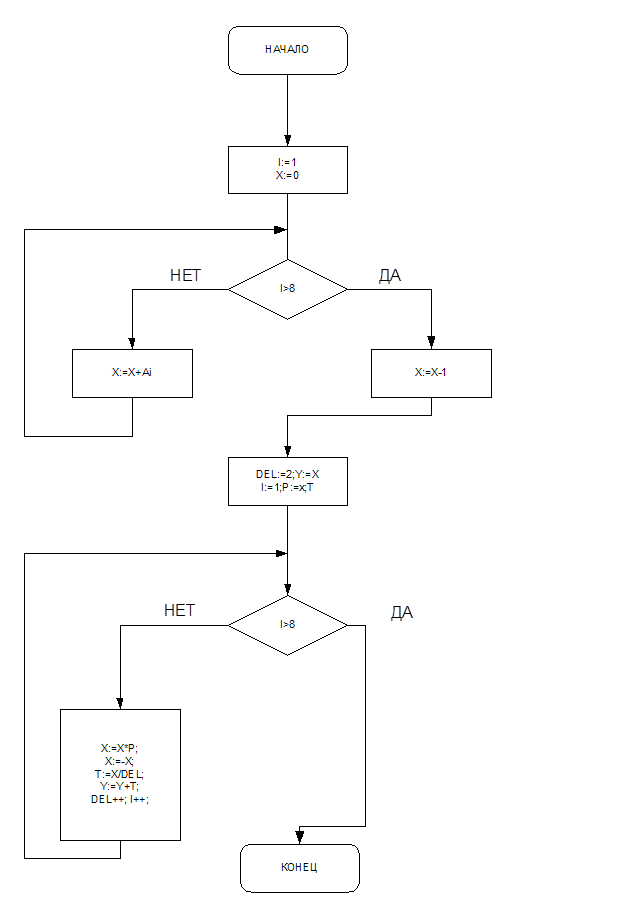

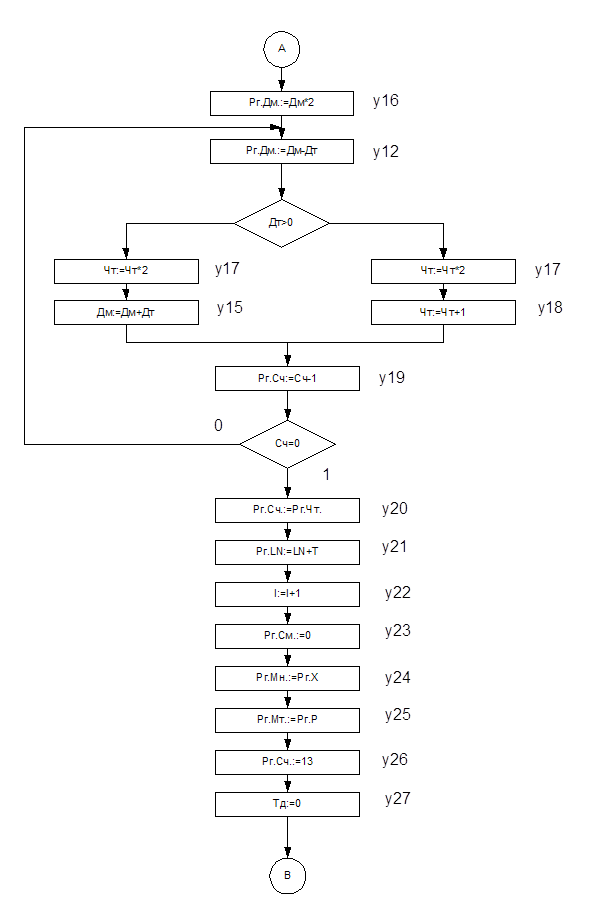

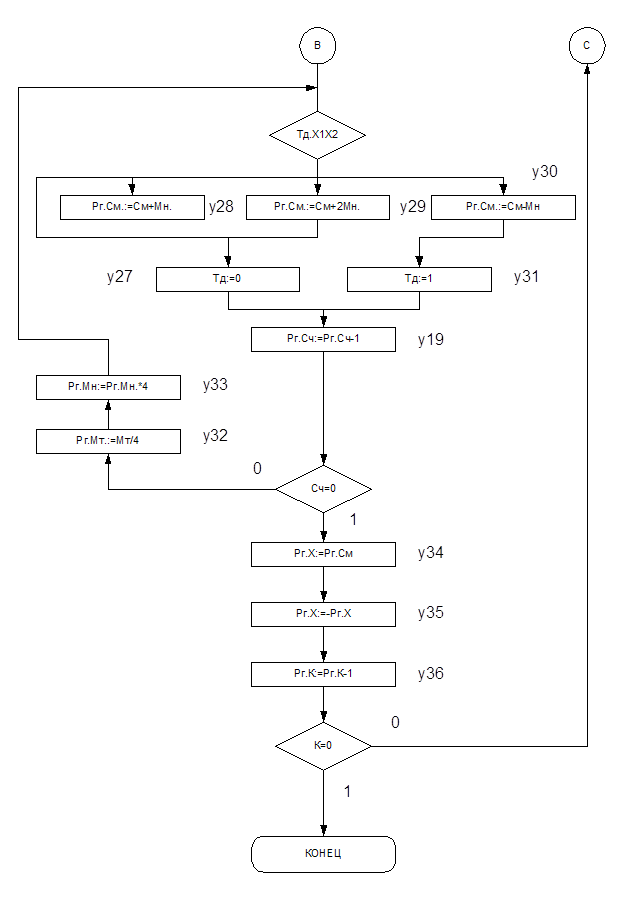

Изложенные выше алгоритмы представлены далее в виде блок-схем.

Рис. 1. Арифметическая операция

Рис. 1. Арифметическая операция ![]()

Рис. 2. Тест ОЗУ.

На основании данных алгоритмов для микро-ЭВМ была выбрана следующая система команд (микроопераций):

mov Reg, операнд

mov Reg, Reg

mov Reg, Mem

mov Mem, Reg

add операнд (к аккумулятору)

add Reg (к аккумулятору)

inc Reg

dec Reg

inc Mem

dec Mem

cmp операнд

jz адрес

jmp адрес

neg Reg

mut Reg (аккумулятор на Reg)

div Reg (аккумулятор на Reg)

in Reg (в Reg номер порта)

out Reg (в Reg номер порта)

shr Reg (сдвиг регистра вправо)

shl Reg (сдвиг регистра влево)

and Reg, операнд

and Reg (Reg с аккумулятором)

or Reg (аккумулятор с Reg)

xor Reg (аккумулятор с Reg)

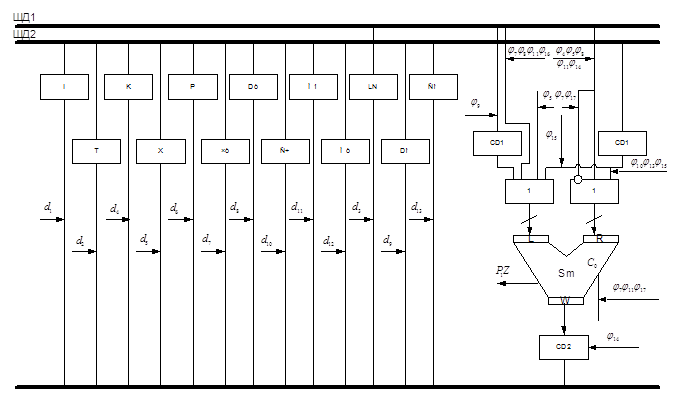

1.2 Разработка обобщённой структуры микро ЭВМ на основе алгоритмов решения задач.

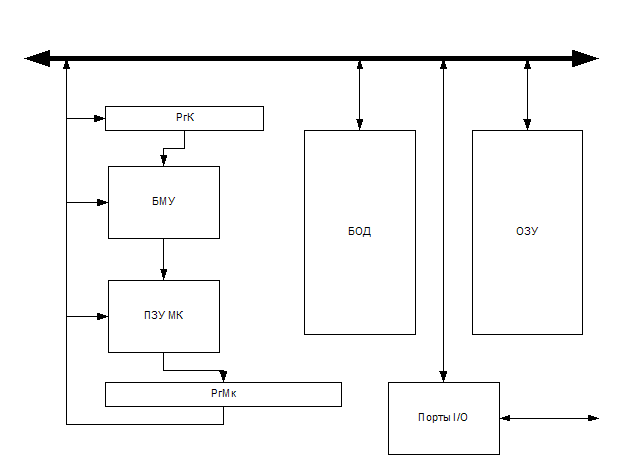

С учётом вышеизложенных алгоритмов обобщённую структуру микро ЭВМ можно представить следующим образом (рис. 3.).

Рис. 3. Обобщённая структура микро ЭВМ.

1.3 Синтез операционных автоматов для процессорных элементов микро ЭВМ.

В качестве операционного автомата для процессорных элементов микро ЭВМ выберем операционный автомат М-типа.

Автоматы данного типа меньшую аппаратную сложность, однако, производительность вычислений уменьшается до одной операции за такт. Логические условия в автомате М-типа могут формироваться как в АЛУ, так и в самих регистрах – путём соответствующих выводов к управляющему автомату.

Далее синтезирован операционный автомат М-типа, реализующий арифметическую операцию, заданную в условии (![]() ).

).

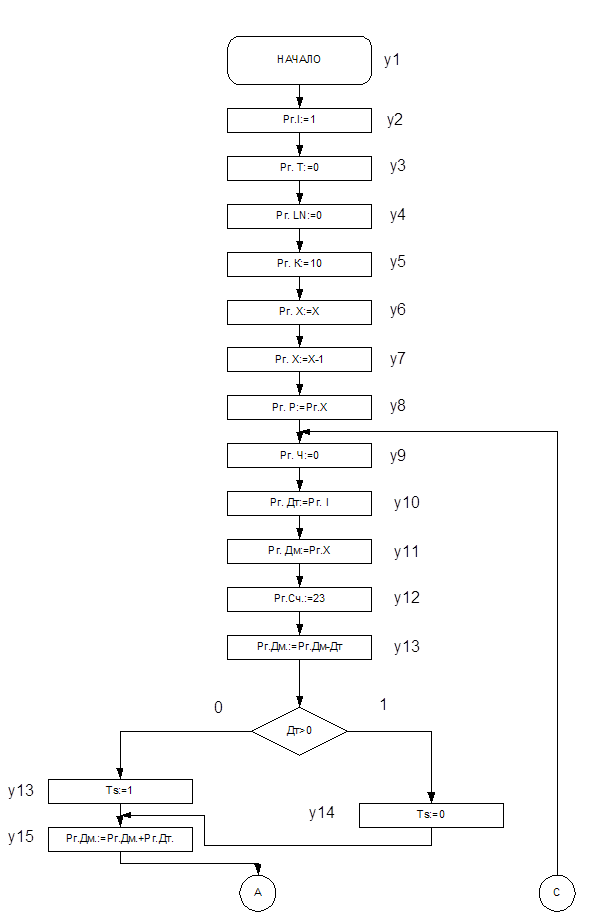

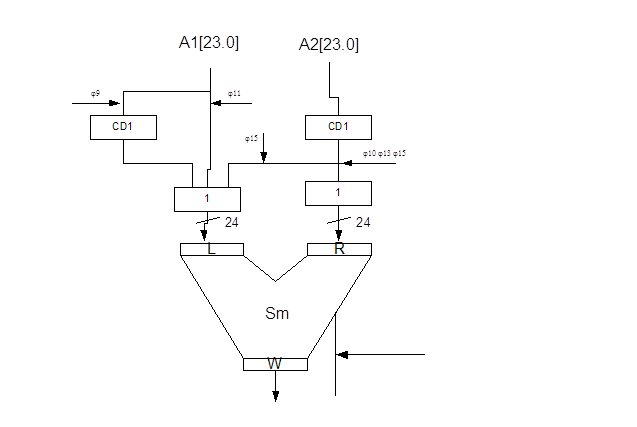

Блок-схема микроопераций, реализующая данную математическую операцию представлена ниже. (Рис. 4.)

Рис. 4.1 Блок схема микроопераций.

Рис. 4.2 Блок схема микроопераций.

Рис. 4.3 Блок схема микроопераций.

В структуре М-автомата использованы две шины данных ШД1 и ШД2. Они соединены с входами АЛУ А1 и А2 соответственно. Разделим множество операндов АЛУ на два подмножества исходя из условий.

Если регистры Ri и Rj операнды одной микрооперации, то они включаются в различные подмножества.

Каждое слово R должно принадлежать хотя бы одному из подмножеств.

Подмножества формируются таким образом, чтобы затраты на коммутацию были минимальные.

Для определения каждого из подмножеств построим таблицу выполняющихся микроопераций, и распределим регистры по шинам.

Результат произведенных действий поместим в таблицу.

|

| Содержание микроопераций | ШД1 | ШД2 |

|

| Рг. I[3.0] := 1 | - | 1 |

|

| Рг. Т[23.0] := 0 | - | - |

|

| Рг. LN[23.0]:=0 | - | - |

|

| Рг. К[3.0] := 10 | - | 10 |

|

| Рг. Х[23.0] := Х | - | Х |

|

| Рг. Х[23.0] := Рг. X[23.0] – 1 | - | Рг. Х |

|

| Рг. Р[23.0] := Рг. Х[23.0] | - | Рг.Х |

|

| Рг. Чт.[23.0] := 0 | - | - |

|

| Рг. Дт.:=Рг.I. | - | Рг.I |

|

| Рг.Дм.[23.0]:=Рг.Х[23.0] | - | Рг.Х |

|

| Рг.Сч.[23.0] := 23 | - | 23 |

|

| Рг.Дм.[23.0] := Рг.Дм.[23.0] + Рг.Дт + 1 | Рг.Дм. | Рг.Дт. |

|

| Т3 := 1 | - | - |

|

| Т3 := 0 | - | - |

|

| Рг.Дм. := Рг.Дм.[23.0] + Рг. Дт. [23.0] | Рг.Дм. | Рг.Дт. |

|

| Рг.Дм. := L1(Рг.Дм.[23.0].0) | Рг.Дм. | - |

|

| Рг.Чт. := L1(Рг.Чт.[23.0].0) | - | Рг.Чт. |

|

| Рг.Чт.[23.0] := Рг.Чт.[23.0] + 1 | - | Рг.Чт. |

|

| Рг.Сч.[23.0] := Рг.Сч.[23.0] – 1 | - | Рг.Сч. |

|

| Рг.Т. := Рг.Чт.[23.0] | - | Рг.Чт. |

|

| Рг.LN[23.0] := Рг.LN[23.0] + Рг.Т.[23.0] | Рг.LN | Рг.Т |

|

| Рг.I[23.0] := Рг.I[23.0] + 1 | - | Рг.I |

|

| Рг.См.[23.0] := 0 | - | - |

|

| Рг.Мн.[23.0] := Рг.Х[23.0] | - | Рг.Х |

|

| Рг.Мт.[23.0] := Рг.Р[23.0] | - | Рг.Р |

|

| Рг.Сч.[23.0] := 13 | - | 13 |

|

| Tд. := 0 | - | - |

|

| Рг.См.[23.0] := Рг.См.[23.0] + Рг.Мн.[23.0] | Рг.См. | Рг.Мн. |

|

| Рг.См.[23.0] := Рг.См. + L1(Рг.Мн.[23.0].0) | Рг.См. | Рг.Мн. |

|

| Рг.См.[23.0] := Рг.См. + | Рг.См. | Рг.Мн. |

|

| Tд. := 1 | - | - |

|

| Рг.Мт.[23.0] := R2(00.Рг.Мт.[23.0]) | - | Рг.Мт. |

|

| Рг.Мн.[23.0] := L2(Рг.Мн.[23.0].00) | - | Рг.Мн. |

|

| Рг.Х[23.0] := Рг.См.[23.0] | Рг.См. | - |

|

| Рг.Х[23.0] := | - | Рг.Х |

|

| Рг.К. := Рг.К.[23.0] – 1 | - | Рг.К. |

Таким образом в первое подмножество попадают регистры:

Рг.Дм;

Рг.См;

Рг.LN.

Во второе подмножество попадают регистры:

Рг.Х;

Рг.I;

Рг.Дт;

Рг.Чт;

Рг.Т;

Рг.Сч;

Рг.Р;

Рг.Мн.;

Рг.Мт;

Рг.К.

Поставим в соответствие каждой микрооперации выполняемой функции оператор присваивания АЛУ. Эти операторы характеризуют действия, выполняемые непосредственно в АЛУ.

Составим таблицу соответствующих микроопераций:

|

| Содержание оператора D | Приемник результата |

|

|

| D := 000…01 | D->Рг.I |

|

|

| D := 000…0 | D->Рг.Т. |

|

|

| D := 000…0 | D->Рг.LN |

|

|

| D := 000…01010 | D->Рг.К |

|

|

| D := A2[23.0] | D->Рг.Х |

|

|

| D := A2[23.0] + 111…1 | D->Рг.Х |

|

|

| D := A2[23.0] | D->Рг.Р |

|

|

| D := 00..00 | D->Рг.Чт |

|

|

| D := A2[23.0] | D->Рг.Дт |

|

|

| D := A2[23.0] | D->Рг.Дм. |

|

|

| D := 000…010111 | D->Рг.Сч. |

|

|

| D := A1[23.0] + | D->Рг.Дм. |

|

|

| D := 000…01 | D->Т3 |

|

|

| D := 000…0 | D->Т3 |

|

|

| D := A1[23.0] + A2[23.0] | D->Рг.Дм. |

|

|

| D := L1(A1[23.0].0) | D->Рг.Дм. |

|

|

| D := L1(A2[23.0].0) | D->Рг.Чт |

|

|

| D := A2[23.0] + 1 | D->Рг.Чт |

|

|

| D := A2[23.0] + 1111…11 | D->Рг.Сч. |

|

|

| D := A2[23.0] | D->Рг.Т. |

|

|

| D := A1[23.0] + A2[23.0] | D->Рг.LN |

|

|

| D := A2[23.0] + 1 | D->Рг.I |

|

|

| D := 000…00 | D->Рг.См. |

|

|

| D := A2[23.0] | D->Рг.Мн. |

|

|

| D := A2[23.0] | D->Рг.Мт. |

|

|

| D := 000…01101 | D->Рг.Сч. |

|

|

| D := 000…00 | D->Тд |

|

|

| D := A1[23.0] + A2[23.0] | D->Рг.См. |

|

|

| D := A2[23.0] + L1(A2[23.0].0) | D->Рг.См. |

|

|

| D := A1[23.0] + | D->Рг.См. |

|

|

| D := 000…01 | D->Тд. |

|

|

| D := R2(00.A2[23.0]) | D->Рг.Мт |

|

|

| D := L2(A2[23.0].00) | D->Рг.Мн. |

|

|

| D := A1[23.0] | D->Рг.Х |

|

|

| D := | D->Рг.Х |

|

|

| D := A2[23.0] + 111…11 | D->Рг.К. |

|

Построим таблицу выбора источников операндов для АЛУ и таблицу выбора приемников результатов.

Таблица источников.

| Источники | Сигналы управления | ||

| A1 | A2 | ai | bj |

| - | I | - | b1 |

| - | T | - | b2 |

| LN | - | a3 | - |

| - | К | - | b4 |

| - | X | - | b5 |

| - | P | - | b6 |

| - | Чт | - | b7 |

| - | Дт | a9 | b8 |

| Дм | - | - | |

| - | Сч | - | b10 |

| - | Мн | - | b11 |

| - | Мт | - | b12 |

| См | - | a13 | - |

Таблица приемников.

| Приемник | Сигнал управления |

| D->Рг.k | Dк |

| I | d1 |

| T | d2 |

| LN | d3 |

| K | d4 |

| X | d5 |

| P | d6 |

| Чт | d7 |

| Дт | d8 |

| Дм | d9 |

| Сч | d10 |

| Мн | d11 |

| Мт | d12 |

| См | d13 |

| Тд | d14 |

| Т3 | d15 |

Выполним кодирование микроопераций наборами управляющих сигналов:

|

|

|

|

|

|

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

| - | - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

| - | - |

|

|

|

|

|

|

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

|

|

|

|

|

|

| - |

|

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

|

|

|

|

|

|

|

| - |

|

|

|

| - | - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

| - | - |

|

|

|

| - | - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| - | - |

|

|

|

|

| - |

|

|

|

|

| - |

|

|

|

| - |

|

|

|

|

|

| - |

|

|

|

|

| - |

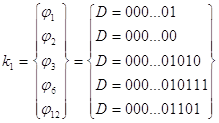

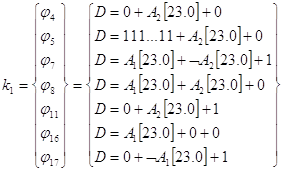

На основании полученных данных составим подмножества эквивалентных операторов:

;

;

;

;

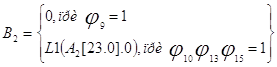

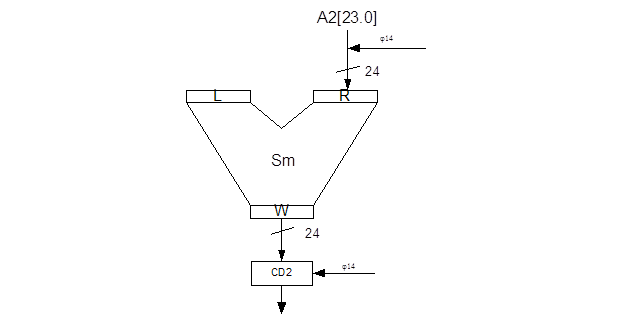

![]()

![]()

![]()

![]()

![]()

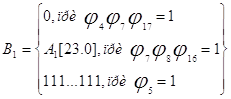

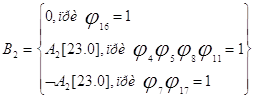

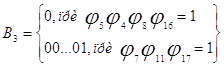

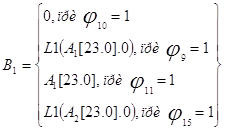

Построим обобщенные операторы.

Класс ![]()

Для установки регистров

2. Класс ![]()

D = B1 + B2 + B3

При этом

Объединим классы k3, k4, k5, k7 в класс k8. Для этого обобщенный оператор примет вид:

Класс ![]() :

:

D = B1 + B2

Класс ![]() :

:

D = B1

![]()

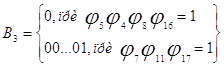

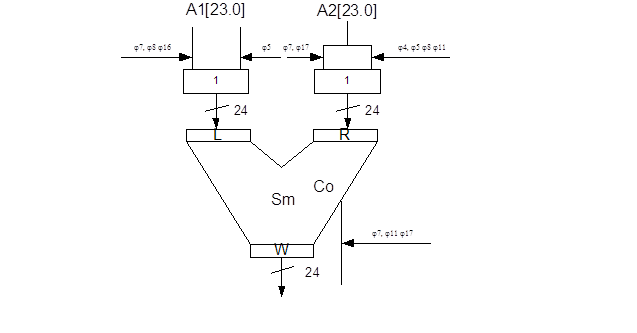

Построим структурные схемы узлов, реализующих обобщенные операторы:

Класс![]() :

:

Класс

Класс ![]() :

:

Класс![]() :

:

На основании полученных выше данных построим обобщенную схему операционного автомата. (Рис. 5).

Рис. 5. Обобщенная схема операционного автомата.

Рис. 5. Обобщенная схема операционного автомата.

Похожие работы

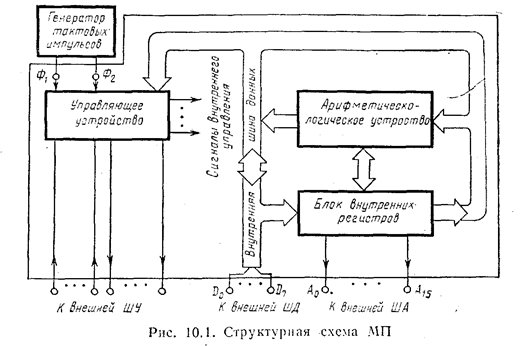

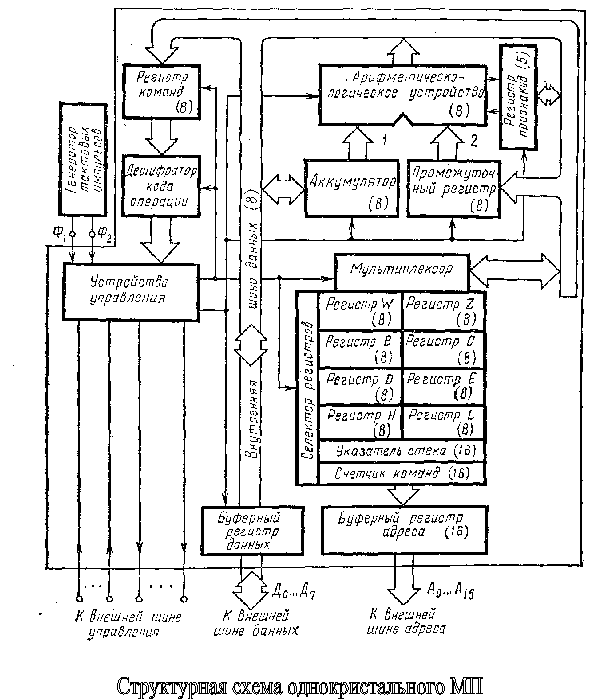

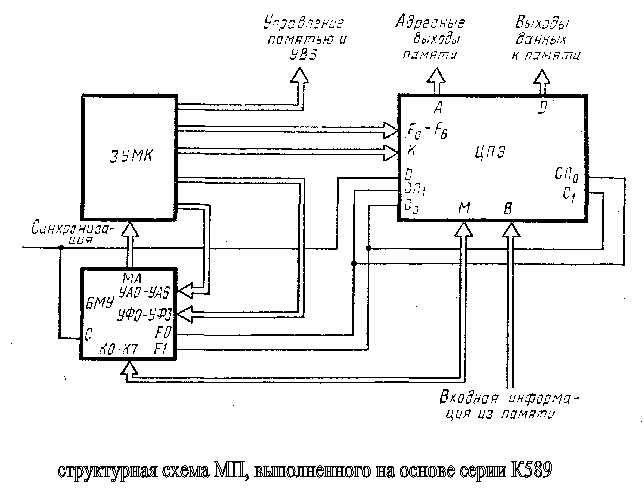

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

0 комментариев