Навигация

Устройство управления микро ЭВМ

2.3.2 Устройство управления микро ЭВМ.

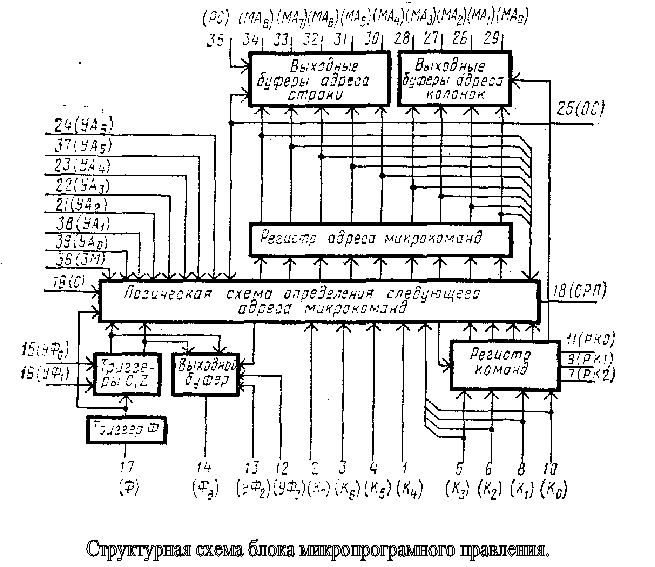

При функционировании микро ЭВМ, в частности при выполнении определенной программы возникает вопрос о времени выполнения определенных микроопераций. Это связано с тем, что некоторые операции выполняются быстрее, другие – медленнее. Поэтому встает вопрос о методах синхронизации некоторых блоков микро ЭВМ для избежания сбоев и ложных срабатываний. Очевидным и наименее сложным является метод тактирования элементов ЭВМ тактами, длительность которых больше максимального времени выполнения микроопераций. Однако из-за неэффективности данного способа (возможно значительное время простоя микро ЭВМ) применение этого метода оказывается неэффективным.

Для построения более эффективных вычислительных устройств может использован следующий метод: предлагается ввести в состав схемы микро ЭВМ схему управления длительностью такта.

В этом случае в Рг.Мк. выделяется определенное поле, которое и определяет время выполнения микрокоманды.

Чтобы избежать излишней громоздкости схемы управления длительностью такта при большом количестве команд с различным временем исполнения, имеет смысл разбить их на группы и применять к каждой группе первый алгоритм.

3. Проектирование структуры микро ЭВМ.

3.1 Проектирование памяти микро ЭВМ.

3.1.1 Проектирование локальной памяти процессорного элемента.

В локальной памяти процессорного элемента хранится микропрограммная интерпретация команд (микрокоманд) компьютера. Очевидно, что количество микросхем модулей памяти определяется двумя факторами:

разрядностью ПЗУ;

разрядностью регистра микрокоманд.

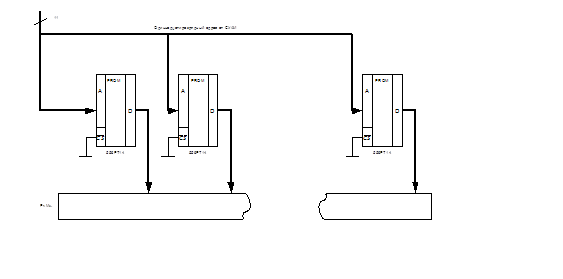

С учетом заданной микросхемы (556РТ14), функциональную схему локальной памяти процессорного элемента можно представить, как показано на рис. 12.

Адрес с выхода СУАМ поступает на адресные входы блока ПЗУ, и на выходных шинах микросхем появляется микрокоманда, поступающая в Рг.Мк.

Рис. 12. Функциональная схема локальной памяти процессорного элемента

3.1.2 Проектирование системы ПЗУ и ОЗУ.

Очевидно, что прикладные программы и другое служебное программное обеспечение находится в оперативном запоминающем устройстве, причем необходимо часть памяти организовать на ПЗУ. В этом случае в нем можно разместить наиболее часто используемые программы, например тест памяти и программу для расчета заданной арифметической операции. С учетом того, что данная микро ЭВМ является специализированной, в ПЗУ можно разместить и обработчики прерываний, которые могут произойти от внешних устройств (портов) центральной ЭВМ или устройства управления.

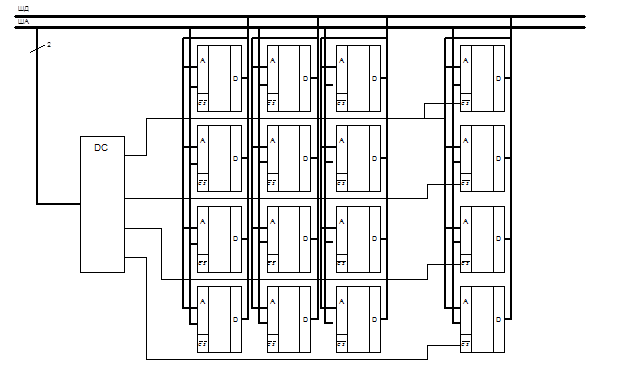

Обобщенную структурную схему ОЗУ можно представить как показано на рис. 13. Подробная принципиальная схема приведена в приложении 1.

3.1.3 Разработка системы адресации.

В разрабатываемой микро ЭВМ поддерживаются следующие методы адресации:

прямая;

непосредственная;

автоинкрементная;

относительная.

Для поддержки перечисленных методов адресации в структуре микро ЭВМ предусмотрен ряд аппаратной поддержки (наличие дополнительных управляющих регистров).

Рассмотрим данные методы адресации и их аппаратную поддержку более подробно.

Прямая адресация.

При считывании команды из памяти в регистр команд вместе с кодом операции попадает адрес первого операнда в выполняемом действии, который может быть передан в блок обработки данных через регистр Рг.ADR. (при наличии соответствующих управляющих сигналов в Рг.Мк.), второй адрес операнда необходимо получить считав в регистр входных данных следующее слово команды из памяти.

2. Непосредственная.

При данном способе адресации в теле команды присутствует сам операнд. Таким образом в регистр команд попадает только код операции, а параметр считывается на следующем такте в регистр входных данных. При реализации данного метода адресации дополнительного аппаратного оборудования не требуется.

3. Автоинкрементная.

При данном способе адресации в качестве номера автоинкрементного регистра используется одно из полей считанного в регистр команд слова. Для аппаратной поддержки данного способа адресации используется регистр с возможностью переключения его выходных шин в третье состояние (высокого сопротивления), выходы которого коммутируются на адресные входы А и В блока обработки данных (МПС).

Рис. 13 Структурная схема ОЗУ.

4. Относительная.

При реализации данного метода адресации были учтены следующие обстоятельства: При считывании слова из оперативной памяти в регистр команд попадает поле (смещение) адресуемого операнда. Это поле может быть передано в блок обработки данных для вычисления исполнительного адреса, в случае, если выставлены разрешающие сигналы в Рг.Мк. Передача этого поля в БОД осуществляется через регистр ADR, который коммутируется на входы данных МПС и имеет возможность переключения своих входных шин в состояние высокого сопротивления.

Обобщая все выше сказанное, можем представить регистр команд в виде, показанном на рис. 14.

| Поле кода операции | Адрес операнда |

| Номер автоинкрементного регистра | |

| Смещение операнда. |

Рис. 14. Регистр команд.

3.2 Разработка системы ввода-вывода и системы прерываний.

3.2.1 Разработка системы ввода-вывода.

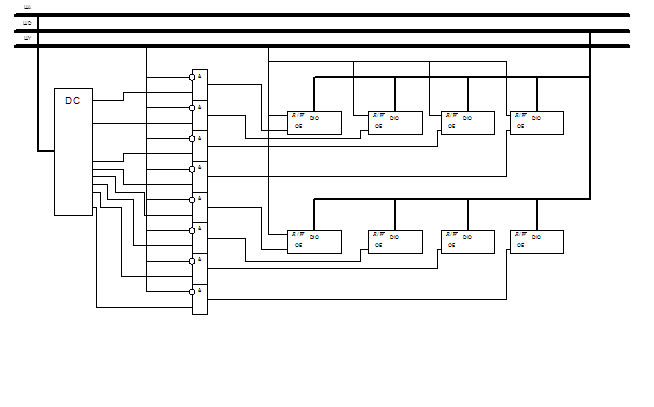

Для адресации портов ввода-вывода будем использовать младшую адресную часть шины адреса и введем идентификатор обращения к портам (памяти). Для передачи (считывания) в порт данных будем использовать младшую часть шины данных.

В этом случае укрупненная функциональная схема портов ввода-вывода может быть представлена в виде, как показано на рис. 15.

Рис. 15. Функциональная схема портов ввода-вывода.

Рис. 15. Функциональная схема портов ввода-вывода.

Похожие работы

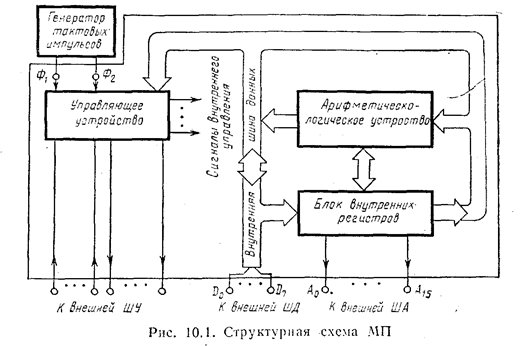

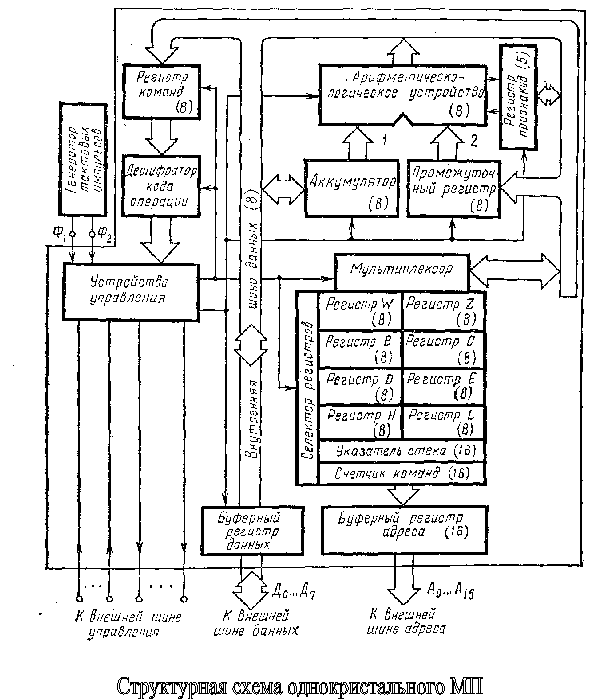

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

0 комментариев