Навигация

2 D< 1 D< 1

1 3 МК(3) D> D>

y17 R 8 y7 S0 8

A У2 C y6 C

A0 У5 > y5 >

y4 C C П9 y5 A1 y1 < y1 <

Р14

МК(0)

D Tзн2 D Tзн1

МК(1) 1 Р2

у1 С у5 С

у5

Рис. 4.

RG3 S3 АЛУ 0 MS D RG2 D RG1

D MK(2) S2 F 1 < > 0 < > 0

MK(1) S1 2 D< 1 D< 1

MK(0) S0 3 МК(4) D> D>

A` P14 y11 R 8 y7 S0 8

B` C9 У2 C y6 C

MK(3) C0 A0 У3 > y3 >

y4 C M y3 A1 y1 < y1 <

y5 1

y3

D Tзн2 D Tзн1

Р2

у1 С у3 С

1 D T

y3

y1 1 C

Рис. 5.

5. Функциональная схема управляющей части

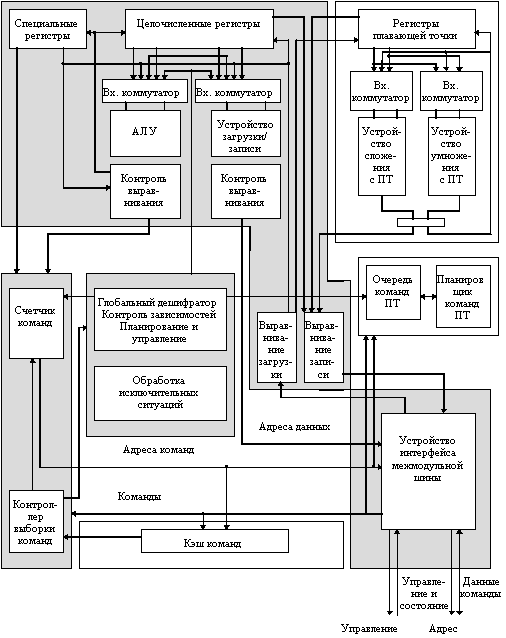

Функциональная схема УЧ устройства представлена на Рис. 8 и включает следующие основные части: триггер запуска (Тзап), управляющую память (УП), регистр адреса МК (RGAMK), схему формирования управляющих сигналов МО у1 - у12 , основу которой составляет дешифратор МК (DCMK), мультиплексор логических условий (MS) и триггер ошибки (Тош), который устанавливается в 1 при обнаружении ошибки в МК, считываемой из УП.

Исходя из количества вершин в графе МП на Рис. 6 и ее сложности, определим ориентировочно количество ячеек в УП, равным 3 сегментам по 16 ячеек в каждом. Формат МК, записываемой в ячейке УП, приведен на Рис. 7.

MK Y XvSнов A` B

0 1 2 3 4 Q1 Q2 Q3 Q4 W P к.р

Рис. 7

Здесь старшие 9 разрядов образуют операционное поле МК. В первых 5 разрядах кодируются горизонтальным способом микроприказы МК(0 - 4),

начало

4

a

0 1 2

y6 6

y11 1 9

0

0 МК(1,2),2 11 МК(0),2

P5

1 1 10

МК(0),у2 7

0 0 15 0

P3 P14 1

1 1 1 12

0 8

P1 9

1 0 4

МК(4), y3, y9 y3, y9 3

1

МК(0),2 1 МК(1,2),2

0

P4 7 0

1 8

0 1

P15 МК(1,2),2 1 МК(0),2

1

МК(1,2), у2 12

5,2

8 1 13

y12 1

0 1

МК(3),2

у2, у5

0 8

1

0 1

1

0 3

1

у12 10

конец

Рис. 6.

в следующих 4-х разрядах ( Q1, Q2, Q3, Q4) кодируются вертикальным способом МО. В них фиксируется номер совокупности импульсных управляющих сигналов МО, входящих в данную МК. В МП на Рис. 6 входят 12 таких совокупностей сигналов. Обозначим их как: Y1=y2 , Y2=y6 , Y3=y1 , Y4=y7 , Y5=y8 , Y6=y9 , Y7={y5 , y2} , Y8=y10 , Y9=y12 , Y10=y4 , Y11=y11 , Y12={y3 , y9}.

Адресное поле МК включает 4-х разрядное поле Х, в котором фиксируется номер логического условия Рi (i=1-15), и 4-х значное поле адреса МК А=А`В где В - младший разряд адреса.

При формировании адреса следующей МК значение проверяемого условия Рi подставляется в младший разряд адреса А.

Также есть разряд W по которому производится останов МП, и разряд межсегментного перехода Р, при единичном значении которого производится межсегментный переход, адрес нового сегмента берется в поле Х.

Последний разряд в МК является контрольным разрядом проверки на четность.

В целом схема на Рис. 8 работает следующим образом. По сигналу “Запуск” в RGAMK фиксируется начальный адрес = 0. При этом на выходах УП с задержкой, равной времени чтения информации из УП, формируются разряды МК, записанной по данному адресу.

Одновременно по сигналу “Запуск” Тзап устанавливается в 1, и в схему УЧ начинают циклически поступать сигналы z1 , z2. По сигналу z1 в ОЧ поступают импульсные управляющие сигналы , по z2 в регистр RGAMK записывается адрес следующей ячейки памяти.

Похожие работы

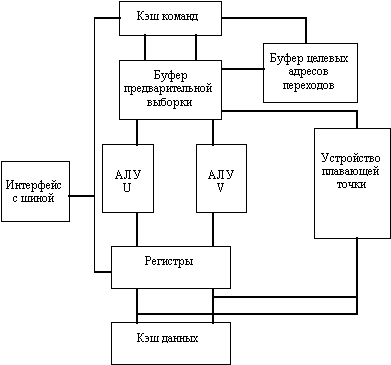

... изменения сегмента (Segment Override). В системе команд насчитывается несколько сотен инструкций, поэтому в данной работе обзорно рассмотрены все команды обработки данных (блоков процессора АЛУ, FPU, MMX, и XMM), а далее более подробно описаны инструкции, появившиеся в процессорах Pentium 3 (блок XMM — SSE) и Pentium 4 (блок XMM — SSE2). Инструкции пересылки данных (см. табл) позволяют ...

... Это почти все что касается самого общего рассказа о процессорах - почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным. 2.2. Алгоритм работы процессора Весь алгоритм работы процессора можно описать в трех строчках НЦ | чтение команды из памяти по адресу, записанному в СК | увеличение СК на длину прочитанной команды | ...

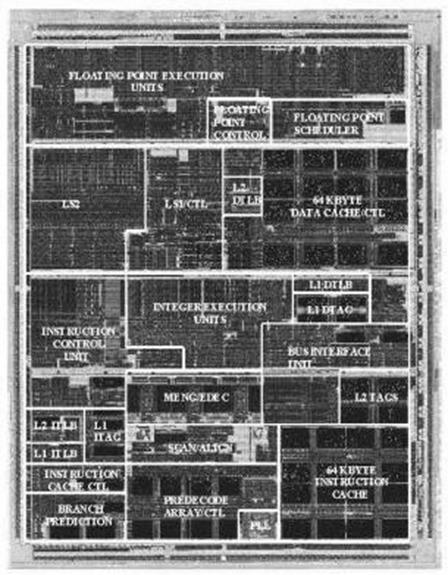

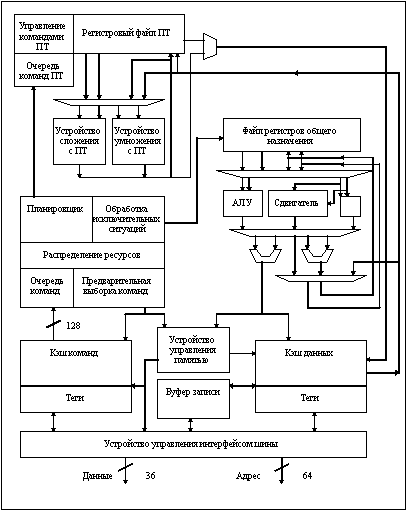

... -инструкций 3DNow!, расширенный дополнительными командами. Всего 45 команд. Ø Выпускаются версии с частотами 500, 550, 600 , 650 и 700МГц. 3. Архитектура процессора AMD Athlon (Thunderbird) Процессор седьмого поколения AMD Athlon (Thunderbird) использует, на данный момент наиболее совершенную микроархитектуру x86. Сочетание указанных ниже свойств предоставляет тем, кто работает с ...

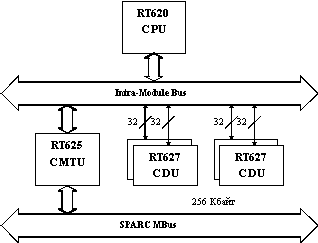

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

0 комментариев