Навигация

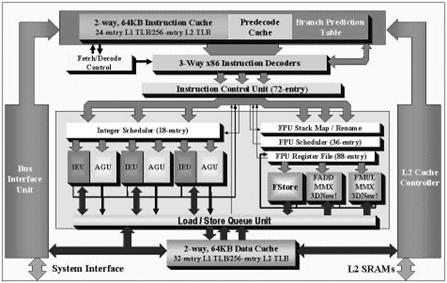

Принципиальная схема управляющей части

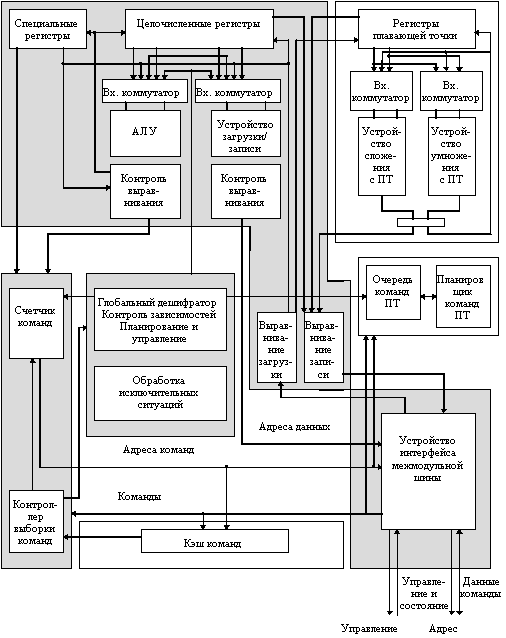

6. Принципиальная схема управляющей части

Принципиальная схема построена на основе общей шины в которую вводятся все входные и выходные сигналы.

Триггеры Тзап , Тош и Т реализованы на микросхеме ТВ9, RGAMK и GRSEG на микросхемах ТМ8, MS - на КП1, схема М2 на 2-х элементах ИП5 и микросхеме ЛП5, схема формирования импульсных сигналов на дешифраторе ИД3, УП - на пяти элементах ПЗУ РТ4.

ош ошибка 0 RG

С & S Тош 1 SEG 0 к.р. ___

Р 1 М2 ОШ

R & C

R ОШ

A УП ...

запуск 0 RG 0

1 J Tзап 1 AMK 1

С C А`` 2 2

остан K 3 3

сброс C

R

R

В

0 MS & 1

Р1 1

R Z2 A`` ...

T & Р15 15 &

D

A

& C &

C Z1 Р

остан

0 0 у1

___ 2 DC 1 схема у2

ОШ 4 MK ... формир. ...

8 у1 - у12

MK(4) 15 у12

MK(3)

MK(2) C

MK(1)

MK(0)

Рис. 8.

7. Таблица микрокоманд

| адрес ячейки | МК | Q | WP | XvS | A` B | Примеч МК | ЛУ |

| 00 0000 | 00000 | 1010 | 00 | 0010 | 0010 | у4 | Р2 |

| 0001 | 00000 | 0000 | 00 | 1111 | 1100 | Р15 | |

| 0010 | 00000 | 0010 | 00 | 0000 | 0100 | у6 | |

| 0011 | 00000 | 0001 | 00 | 0000 | 1111 | у2 | |

| 0100 | 00000 | 1010 | 00 | 0101 | 0110 | у11 | Р5 |

| 0101 | 00000 | 0111 | 00 | 0000 | 1110 | у2, у5 | |

| 0110 | 00000 | 0000 | 00 | 0011 | 1000 | Р3 | |

| 0111 | 10000 | 0001 | 00 | 0011 | 1000 | МК(0), у2 | Р3 |

| 1000 | 00000 | 0000 | 00 | 1110 | 1010 | Р14 | |

| 1001 | 00000 | 0000 | 00 | 0001 | 1010 | Р1 | |

| 1010 | 00000 | 1100 | 00 | 0100 | 0000 | у3, у9 | Р4 |

| 1011 | 00001 | 1100 | 00 | 0100 | 0000 | МК(4),у3,у9 | Р4 |

| 1100 | 00000 | 1001 | 00 | 0000 | 0101 | у12 | |

| 1101 | 01100 | 0001 | 00 | 0000 | 1100 | МК(1,2), у2 | |

| 1110 | 00000 | 1001 | 10 | 0000 | 0000 | у12 | останов |

| 1111 | 00000 | 0010 | 01 | 0001 | 0000 | у6 | межс.БП |

| 01 0000 | 00000 | 0000 | 00 | 1001 | 0010 | Р9 | |

| 0001 | |||||||

| 0010 | 00000 | 0011 | 00 | 1011 | 0100 | у1 | Р11 |

| 0011 | 00000 | 1000 | 10 | 0000 | 0000 | у10 | останов |

| 0100 | 01100 | 0001 | 00 | 1010 | 0110 | МК(1,2), у2 | Р10 |

| 0101 | 10000 | 0001 | 00 | 1010 | 0110 | МК(0), у2 | Р10 |

| 0110 | 00000 | 0100 | 00 | 0111 | 1000 | у7 | Р15 |

| 0111 | 00000 | 0000 | 00 | 0111 | 1000 | Р15 | |

| 1000 | 00000 | 0110 | 00 | 0100 | 1010 | у9 | Р4 |

| 1001 | 00000 | 0000 | 00 | 1100 | 1100 | Р12 | |

| 1010 | 00000 | 0000 | 00 | 0000 | 0010 | БП | |

| 1011 | 00000 | 0000 | 00 | 0011 | 1100 | P3 | |

| 1100 | 00000 | 1001 | 01 | 0010 | 0001 | y12 | межс.БП |

| 1101 | 00000 | 0000 | 00 | 0001 | 1110 | P1 | |

| 1110 | 10000 | 0001 | 01 | 0010 | 0000 | МК(0),у2 | межс.БП |

| 1111 | 01100 | 0001 | 01 | 0010 | 0000 | МК(1,2),у2 | межс.БП |

| 10 0000 | 00000 | 0000 | 00 | 0111 | 0010 | Р7 | |

| 0001 | 00000 | 0111 | 00 | 1000 | 1000 | у5, у2 | Р8 |

| 0010 | 00000 | 0000 | 00 | 1000 | 0100 | Р8 | |

| 0011 | 00000 | 01 | 0001 | 1100 | у | межс.БП | |

| 0100 | 00000 | 0000 | 01 | 0001 | 1100 | межс.БП | |

| 0101 | 00000 | 0000 | 00 | 0001 | 0110 | Р1 | |

| 0110 | 01100 | 0001 | 01 | 0001 | 1100 | МК(1,2),у2 | межс.БП |

| 0111 | 10000 | 0001 | 01 | 0001 | 1100 | МК(0),у2 | межс.БП |

| 1000 | 00000 | 0000 | 00 | 0001 | 1010 | Р1 | |

| 1001 | 00000 | 0000 | 00 | 1101 | 1010 | Р13 | |

| 1010 | 00000 | 0000 | 00 | 1000 | 1100 | Р8 | |

| 1011 | 00010 | 0001 | 00 | 1000 | 1100 | МК(3), у2 | Р8 |

| 1100 | 00000 | 1001 | 10 | 0000 | 0000 | у12 | останов |

| 1101 | 00000 | 0000 | 00 | 0001 | 1110 | Р1 | |

| 1110 | 00000 | 1001 | 10 | 0000 | 0000 | у12 | останов |

| 1111 | 00000 | 0000 | 01 | 0011 | 0000 | межс.БП | |

| 11 0000 | 00000 | 0000 | 00 | 0011 | 0010 | Р3 | |

| 0001 | |||||||

| 0010 | 00000 | 1001 | 10 | 0000 | 0000 | у12 | останов |

| 0011 | 00000 | 1000 | 10 | 0000 | 0000 | у10 | останов |

Литература

1. Курс лекций по предмету “Процессоры”

2. Карцев М.А. Арифметика цифровых машин. М. “Наука” 1969

3. Шило В.Л. Популярные цифровые микросхемы. М. “Радио и связь”

Спецификация

| № | Обозначение | Кол. | Адрес |

| 1 | К155ЛИ4 | 1 | DD1 |

| 2 | К155ЛИ6 | 1 | DD2 |

| 3 | К155ЛЛ1 | 1 | DD3 |

| 4 | К155ТВ9 | 2 | DD4, DD5 |

| 5 | К155ТМ8 | 2 | DD6, DD7 |

| 6 | К556РТ4 | 5 | DD8 - DD12 |

| 7 | К155ИП5 | 2 | DD13, DD14 |

| 8 | К155ЛП5 | 1 | DD15 |

| 9 | К155КП1 | 1 | DD16 |

| 10 | К155ЛИ1 | 1 | DD17 |

| 11 | К155ИД3 | 1 | DD18 |

| 12 | К155ЛН1 | 2 | DD19, DD20 |

Похожие работы

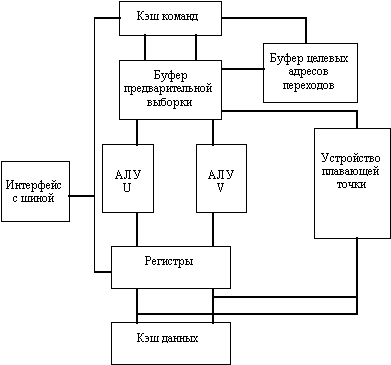

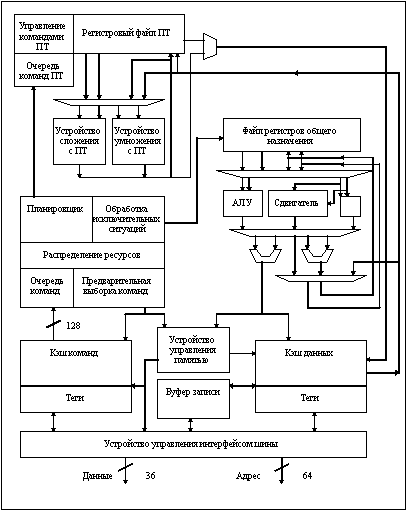

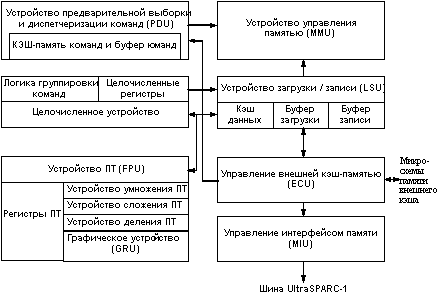

... изменения сегмента (Segment Override). В системе команд насчитывается несколько сотен инструкций, поэтому в данной работе обзорно рассмотрены все команды обработки данных (блоков процессора АЛУ, FPU, MMX, и XMM), а далее более подробно описаны инструкции, появившиеся в процессорах Pentium 3 (блок XMM — SSE) и Pentium 4 (блок XMM — SSE2). Инструкции пересылки данных (см. табл) позволяют ...

... Это почти все что касается самого общего рассказа о процессорах - почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным. 2.2. Алгоритм работы процессора Весь алгоритм работы процессора можно описать в трех строчках НЦ | чтение команды из памяти по адресу, записанному в СК | увеличение СК на длину прочитанной команды | ...

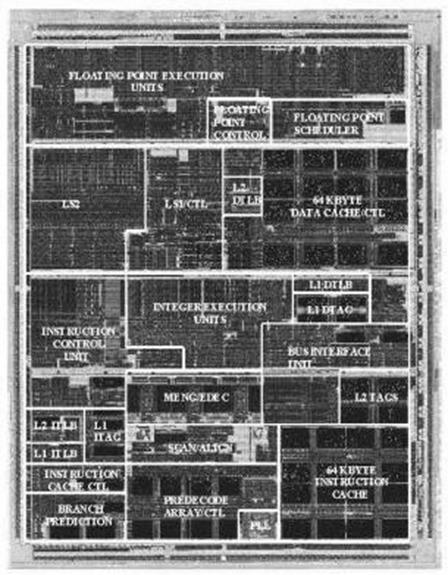

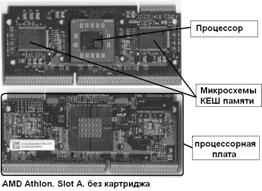

... -инструкций 3DNow!, расширенный дополнительными командами. Всего 45 команд. Ø Выпускаются версии с частотами 500, 550, 600 , 650 и 700МГц. 3. Архитектура процессора AMD Athlon (Thunderbird) Процессор седьмого поколения AMD Athlon (Thunderbird) использует, на данный момент наиболее совершенную микроархитектуру x86. Сочетание указанных ниже свойств предоставляет тем, кто работает с ...

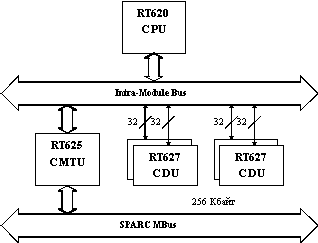

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

0 комментариев