Навигация

3. Автоинкрементная.

При данном способе адресации в качестве номера автоинкрементного регистра используется одно из полей считанного в регистр команд слова. Для аппаратной поддержки данного способа адресации используется регистр с возможностью переключения его выходных шин в третье состояние (высокого сопротивления), выходы которого коммутируются на адресные входы А и В блока обработки данных (МПС).

Рис. 13 Структурная схема ОЗУ.

4. Относительная.

При реализации данного метода адресации были учтены следующие обстоятельства: При считывании слова из оперативной памяти в регистр команд попадает поле (смещение) адресуемого операнда. Это поле может быть передано в блок обработки данных для вычисления исполнительного адреса, в случае, если выставлены разрешающие сигналы в Рг.Мк. Передача этого поля в БОД осуществляется через регистр ADR, который коммутируется на входы данных МПС и имеет возможность переключения своих входных шин в состояние высокого сопротивления.

Обобщая все выше сказанное, можем представить регистр команд в виде, показанном на рис. 14.

| Поле кода операции | Адрес операнда |

| Номер автоинкрементного регистра | |

| Смещение операнда. |

Рис. 14. Регистр команд.

3.2 Разработка системы ввода-вывода и системы прерываний. 3.2.1 Разработка системы ввода-вывода.Для адресации портов ввода-вывода будем использовать младшую адресную часть шины адреса и введем идентификатор обращения к портам (памяти). Для передачи (считывания) в порт данных будем использовать младшую часть шины данных.

В этом случае укрупненная функциональная схема портов ввода-вывода может быть представлена в виде, как показано на рис. 15.

Рис. 15. Функциональная схема портов ввода-вывода.

3.2.2 Разработка системы прерываний.

При функционировании микро ЭВМ возможно возникновение ситуаций, когда требуется немедленное вмешательство процессора. Такими ситуациями для проектируемого устройства могут быть:

- запрос данных от центральной ЭВМ;

- запись новой информации в порт ввода-вывода;

- другие запросы от устройства управления.

При появлении запроса на прерывание, контроллер прерываний через приоритетный шифратор выдает на ПНА номер вектора прерывания и ведет счет вложенных прерываний. При достижении двух уровней вложенности прерываний контроллер игнорирует все запросы вплоть до окончания обработки последнего произошедшего прерывания.

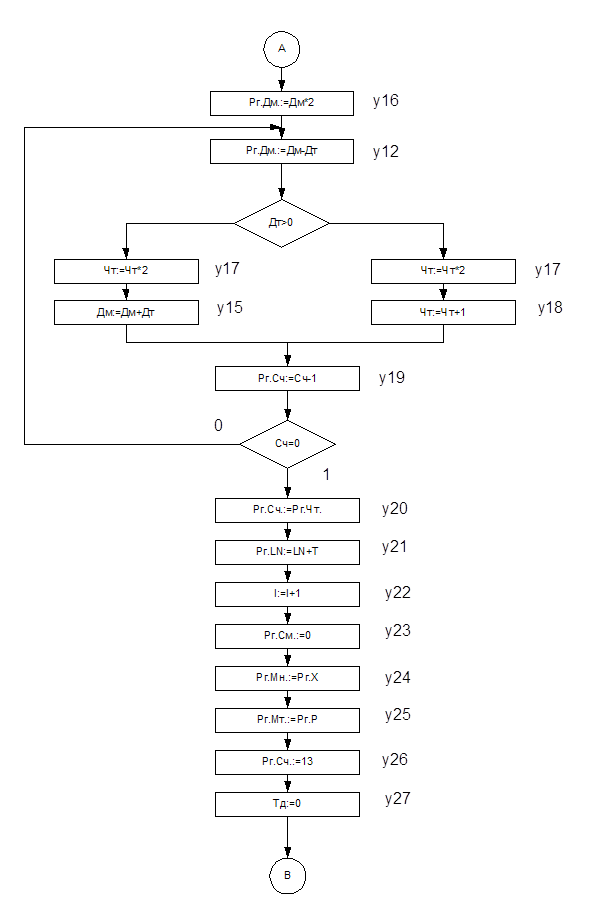

Структурная схема такого контроллера представлена на рис. 16.

Рис. 16. Структурная схема контроллера прерываний.

3.3 Проектирование системы ПДП.В некоторых случаях возникает необходимость в передаче данных без помощи процессора. В этом случае является необходимым использование системы прямого доступа к памяти. Применительно к разрабатываемой микро ЭВМ использование системы ПДП необходимо при запросе от центральной ЭВМ на передачу ей данных. В этом случае процессор отключается от шины и все функции по формированию управляющих сигналов берет на себя контроллер прямого доступа к памяти (ПДП). С учетом этого и структуры памяти центральной ЭВМ (память динамическая на основе микросхем 565РУ6), структурная схема контроллера ПДП может быть представлена, как показано на рис. 17.

Рис. 17. Структурная схема контроллера ПДП.

3.4 Разработка внутреннего интерфейса микрокомпьютера.

Совокупность аппаратных средств, предназначенных для связи отдельных частей микрокомпьютера называют внутренним интерфейсом ЭВМ.

Во внутреннем интерфейсе можно выделить следующие основные части:

- шина адреса (для управления адресными элементами микро ЭВМ);

- шина данных (для обмена операндами);

- шина управления (совокупность управляющих сигналов для заданного режима работы).

В разрабатываемой микро ЭВМ все вышеперечисленные компоненты используются, что позволяет упростить протоколы обмена и максимально увеличить производительность.

4. Разработка микропрограммного обеспечения. 4.1 Микропрограммная интерпретация команд языка компьютера.Всякая команда из системы команд микро ЭВМ представляет собой некоторый набор микроопераций прошитых в ПЗУ микрокоманд, которые выполняются в случае считывания данной команды в регистр команд. При этом отдельные микрооперации попадают в регистр микрокоманд, который по сути дела т выставляет управляющие сигналы ко всем управляемым элементам микро ЭВМ, обеспечивая тем самым корректное выполнение заданной отдельной микрооперации и команды в целом.

Для демонстрации порядка выполнения команд в виде некоторой последовательности микрокоманд рассмотрим формат регистра микрокоманд:

| № п/п | Название | Назначение |

| 0-3 | UI0 - UI3 | Инструкция для УСА |

| 4-15 | D0 - D11 | Адрес для перехода в СУАМ |

| 16-24 | I0 – I8 | Инструкция для МПС |

| 25 - 32 | A, B | Адресные входы БОД |

| 33 – 45 | SI0 – SI12 | Операция СУСС |

| 46 | C0 | Входной перенос в МПС |

| 47 | Разрешение выдачи с DI | |

| 48 | Разрешение выдачи с ADR | |

| 49 | Разрешение выдачи с RON | |

| 50 | Разрешение выдачи с A, B с Рг.Мк. | |

| 51 | Разрешение на запись в DO | |

| 52 | Разрешение выдачи с DO | |

| 53 | Разрешение на запись в Рг.А | |

| 54 | Разрешение на выдачу А | |

| 55 | Обращение к портам ОЗУ | |

| 56 | Чтение – запись | |

| 57 | Запрос на PDP | |

| 58 | Запрет сдвигов |

Таким образом, разрядность регистра микрокоманд – 58 разрядов. Следовательно, для реализации ПЗУ микрокоманд потребуется 15 микросхем 556РТ14.

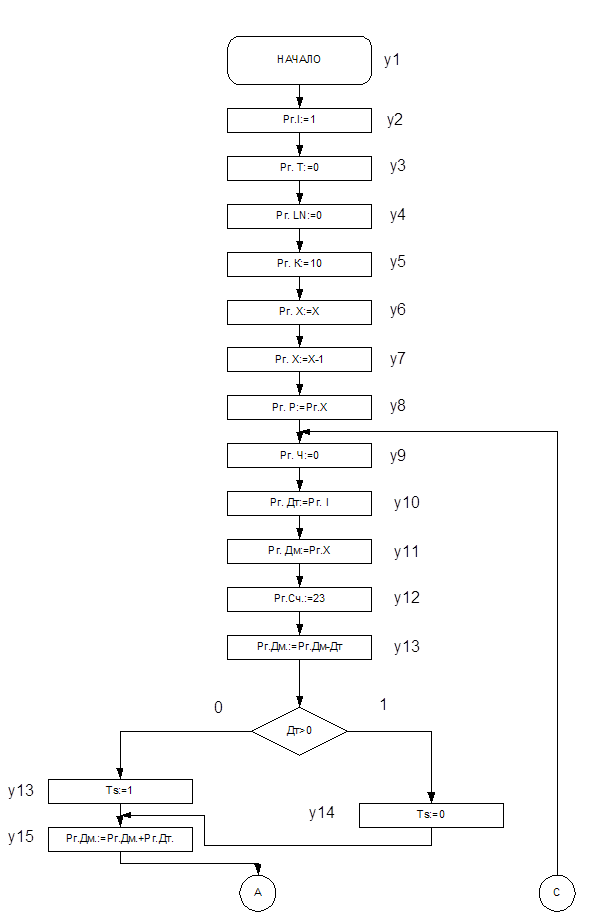

Рассмотрим микропрограммную реализацию некоторых команд микро ЭВМ (макрокоманд):

MOV REG, операнд

| 1) | 1110 | XXXXXXXXXXXX | 011000011 | XXXX | 0000 | XXXXXXXXXXXXX | 1111 011 001 101 |

| 2) | 1110 | XXXXXXXXXXXX | 011000111 | XXXX | XXXX | XXXXXXXXXXXXX | 0010 111 111 101 |

Аналогичным образом строятся все микрокоманды.

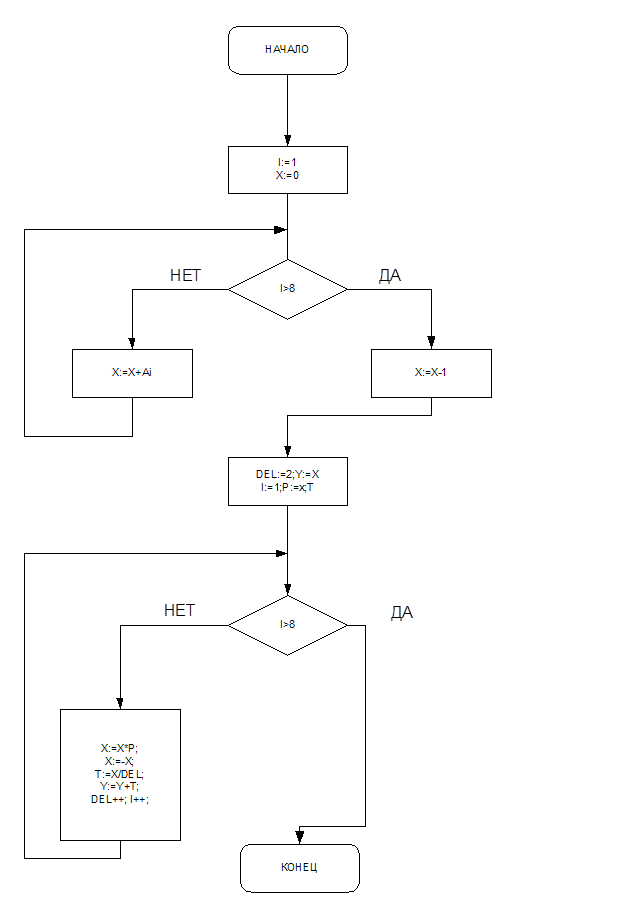

4.2 Разработка программы арифметической операции.Программа вычисления ln x в командах данной микро ЭВМ будет выглядеть следующим образом:

| MOV | R1, | 1 | |

| MOV | R2, | 0 | |

| MOV | R11, | 0 | |

| MOV | R3, | 0 | |

| MOV | R4, | X | |

| DEC | R4 | ||

| M6: | MOV | R5, | R4 |

| M1: | MOV | R6, | 0 |

| MOV | R7, | R1 | |

| MOV | R12, | R4 | |

| MOV | A0, | R7 | |

| SUB | R7 | ||

| CMP | 0 | ||

| JA | MZ | ||

| MOV | R14, | 1 | |

| JMP | M3 | ||

| MZ: | MOV | R14, | 0 |

| M3: | SHL | R12 | |

| MOV | R0, | R12 | |

| SUB | R7 | ||

| CMP | 0 | ||

| JA | M4 | ||

| SHL | R6 | ||

| ADD | R7 | ||

| MOV | R12, | R0 | |

| JMP | M5 | ||

| M4: | SHL | R6 | |

| INC | R6 | ||

| MOV | R12 | R2 | |

| M5: | DEC | R8 | |

| MOV | R0, | R8 | |

| CMP | 0 | ||

| JZ | M6 | ||

| MOV | R2, | R6 | |

| MOV | R0, | R11 | |

| INC | R1 | ||

| MOV | R13, | 0 | |

| MOV | R9, | R4 | |

| MOV | R10, | R5 | |

| MOV | R0, | R9 | |

| MUL | R10 | ||

| MOV | R4, | R0 | |

| NEG | R4 | ||

| DEC | R3 | ||

| MOV | R0, | R3 | |

| CMP | 0 | ||

| JZ | M7 | ||

| JMP | M0 | ||

| M7 | |||

| END |

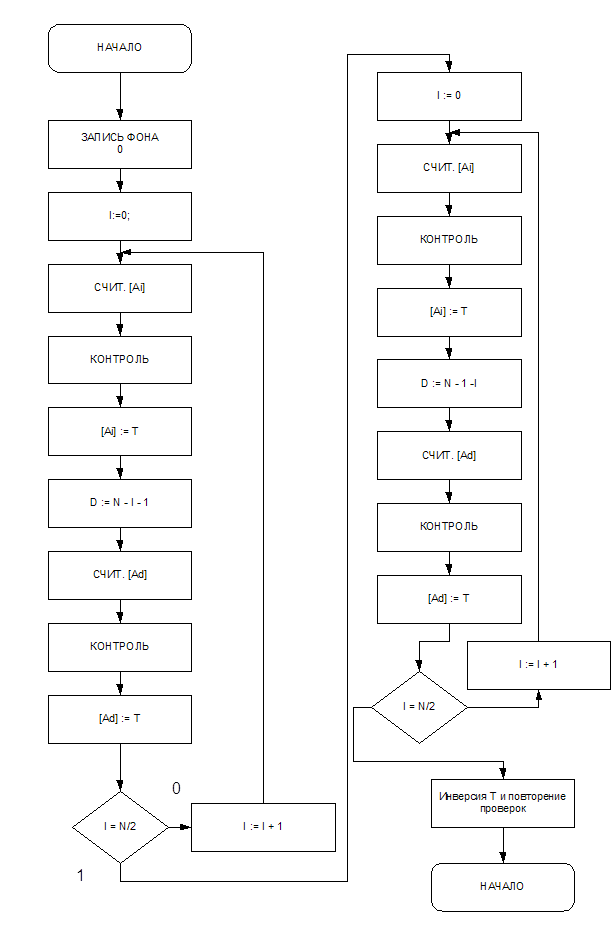

Текст программы теста ОЗУ:

| M0: | MOV | R0, | 7FFF |

| MOV | R1, | 0 | |

| MOV | [R0], | R1 | |

| DEC | R0 | ||

| CMP | 0 | ||

| JZ | M1 | ||

| JMP | M0 | ||

| M1: | MOV | R1, | 0 |

| M2: | MOV | R0, | [R1] |

| CMP | 0 | ||

| JNZ | ERROR | ||

| MOV | [R1], | 111..11 | |

| DEC | R5 | ||

| MOV | R0, | R5 | |

| SUB | R1 | ||

| MOV | R6, | R0 | |

| MOV | R0, | [R6] | |

| CMP | 0 | ||

| JNZ | ERROR | ||

| MOV | [R6], | 11..11 | |

| MOV | R0, | R1 | |

| CMP | 3FFF | ||

| JNZ | MZ | ||

| MOV | R1, | 0 | |

| M3: | MOV | R0, | [R1] |

| CMP | 0 | ||

| JNZ | ERROR | ||

| MOV | [R1], | 0 | |

| MOV | R0, | R5 | |

| DEC | R0 | ||

| SUB | R1 | ||

| MOV | R6, | R0 | |

| MOV | R0, | [R6] | |

| CMP | 0 | ||

| JNZ | ERROR | ||

| MOV | [R6], | 0 | |

| MOV | R0, | R1 | |

| CMP | 3FFF | ||

| JNZ | M3 | ||

| JMP | OK | ||

| ERROR: | HALT | ||

| OK: | |||

| END |

Таким образом в процессе выполнения курсового проекта была создана микро ЭВМ на комплекте серии 1804, позволяющая производить сбор и обработку информации, имеющая свою универсальную систему команд, с возможностью выполнения сложной арифметической функции.

Данная микро ЭВМ может быть использована в качестве периферийной вычислительной машины или как автономный бортовой компьютер в тех областях, где применение таких устройств является необходимым.

Похожие работы

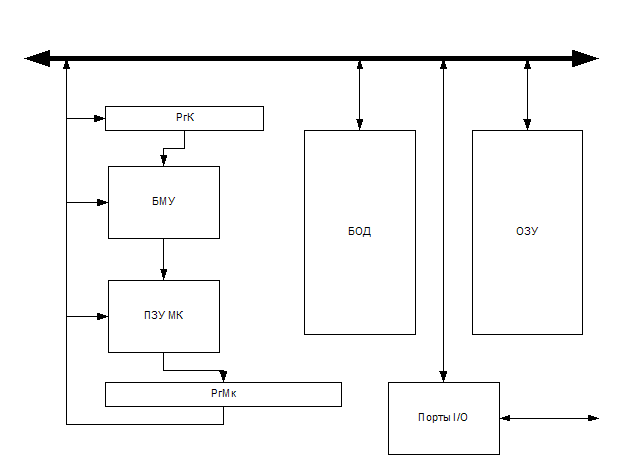

... регистра вправо) shl Reg (сдвиг регистра влево) and Reg, операнд and Reg (Reg с аккумулятором) or Reg (аккумулятор с Reg) xor Reg (аккумулятор с Reg) 1.2 Разработка обобщённой структуры микро ЭВМ на основе алгоритмов решения задач. С учётом вышеизложенных алгоритмов обобщённую структуру микро ЭВМ можно представить следующим образом (рис. 3.). Рис. 3. Обобщённая структура микро ЭВМ. ...

... напряжения. У ЦАП с токовым выходом этот параметр в большой степени зависит от типа выходного ОУ. Виды ЦАП Существуют последовательные и параллельные ЦАП. Последовательные –- используются в микропроцессорных системах, если не требуется высокое быстродействие. Среди параллельных - наиболее просты ЦАП с суммированием весовых токов Большинство схем параллельных ЦАП основано на суммировании ...

0 комментариев