Навигация

3. Технология MMX

Технология ММХ ориентирована на приложения мультимедиа, 2D/3D-графикy и коммуникации. Это расширение базовой архитектуры появилось только после выхода второго поколения процессоров Pentium. Основная идея ММХ заключается в одновременной обработке нескольких элементов данных за одну инструкцию — так называемая технология SIMD (Single Instruction — Multiple Data). Расширение ММХ использует новые типы упакованных 64-битных целочисленных данных:

• упакованные байты (Packed byte) — восемь байт;

• упакованные слова (Packed word) — четыре слова;

• упакованные двойные слова (Packed doubleword) — два двойных слова;

• учетверенное слово (Quadword) — одно слово.

Эти типы данных могут специальным образом обрабатываться в 64-битных регистрах ММХ0-ММХ7, представляющих собой младшие биты стека 80-битных регистров FPU. Каждая инструкция ММХ выполняет действие сразу над всем комплектом операндов (8, 4, 2 или 1), размещенных в адресуемых регистрах. Как и регистры FPU, эти регистры ММХ не могут использоваться для адресации памяти. Совпадение регистров ММХ и FPU накладывает ограничения на чередование кодов FPU и ММХ — забота об этом лежит на программисте приложений с ММХ.

Еще одна особенность технологии ММХ — поддержка арифметики с насыщением (saturating arithmetic). Ее отличие от обычной арифметики с циклическим переполнением (wraparound mode) заключается в том, что при возникновении переполнения в результате фиксируется максимально возможное значение для данного типа данных, а перенос игнорируется. В случае переполнения снизу в результате фиксируется минимально возможное значение. Граничные значения определяются типом (знаковый или беззнаковый) и разрядностью переменных. Такой режим вычислений удобен, например, для определения цветов.

В систему команд введено 57 дополнительных инструкций для одновременной обработки нескольких единиц данных. Одновременно обрабатываемое 64-битное слово может содержать как одну единицу обработки, так и 8 однобайтных, 4 двухбайтных или 2 четырехбайтных операнда. Новые инструкции включают следующие группы:

• арифметические (Arithmetic Instructions), куда входят сложение и вычитание в разных режимах, умножение и комбинация умножения и сложения;

• сравнение (Comparison Instructions) элементов данных на равенство или по величине;

• преобразование форматов (Conversion Instructions);

• логические инструкции (Logical Instructions) — И, И-НЕ, ИЛИ и исключающее ИЛИ, выполняемые над 64-битными операндами;

• сдвиги (Shift Instructions) — логические и арифметические;

• пересылки данных (Data Transfer Instructions) между регистрами ММХ и целочисленными регистрами или памятью;

• очистка ММХ (Empty ММХ State) — установка признаков пустых регистров в слове тегов.

Инструкции ММХ не влияют на флаги условий в слове состояния FPU.

Регистры ММХ в отличие от регистров FPU адресуются физически, а не относительно значения указателя стека ТОР. Более того, любая инструкция ММХ обнуляет поле ТОР регистра состояния FPU. В слове тегов свободному регистру соответствует комбинация 11, остальные комбинации указывают только на занятость регистра. После каждой операции ММХ биты тегов регистра назначения обнуляются. Неиспользуемые в ММХ биты [79:64] регистров FPU заполняются единицами, так что ошибочная обработка данных ММХ инструкцией FPU приведет к исключению.

Инструкции ММХ не порождают новых исключений. Исключения при выполнении инструкций ММХ могут возникать только в случае нарушения границ в обращениях к памяти (как при обмене данными, так и при выборке инструкции). Однако если предшествующая инструкция FPU породила условие исключения, то оно произойдет при выполнении инструкции ММХ. После его обработки инструкция ММХ может исполнена.

С инструкциями ММХ могут применяться префиксы замены сегмента и изменения разрядности адреса (влияют на инструкции, обращающиеся к памяти). Использование префиксов изменения разрядности операнда и повторов зарезервировано (может привести к непредсказуемым результатам). Префикс Lock вызывает исключение #UD.

Инструкции ММХ доступны из любого режима процессора. При переключении задач необходимо следить за корректностью сохранения контекста, как и при работе с FPU.

Любая инструкция ММХ вызывает обнуление полей тегов всех регистров FPU/ММХ, что для FPU означает наличие действительных данных во всех регистрах. Последующая инструкция для FPU над "неправильными" данными может привести к непредсказуемому результату, поскольку "входной контроль" данных осуществляется по состоянию тегов. Чтобы застраховаться от подобных неприятностей, после инструкций ММХ и перед инструкциями FPU в программный код вводят инструкцию EMMS, которая устанавливает в слове тегов значение FFFFh (все регистры пустые).

Различие в способе адресации регистров (относительная для FPU и явная прямая в ММХ), обнуление тегов инструкциями ММХ и некоторые другие нюансы не позволяют чередовать инструкции FPU и ММХ. Блок FPU/MMX может работать либо в одном, либо в другом режиме. Если, к примеру, в цепочку инструкций FPU нужно вклинить инструкции ММХ, после чего продолжить вычисления FPU, то перед первой инструкцией ММХ приходится сохранять контекст (состояние регистров) FPU в памяти, а после этих инструкций снова загружать контекст. На эти сохранения и загрузки расходуется процессорное время, в результате возможна полная потеря выигрыша от реализации технологии SIMD. Совпадение регистров ММХ и FPU оправдывают тем, что для сохранения контекста ММХ при переключении задач не требуется доработок в операционной системе — контекст ММХ сохраняется тем же способом, что и FPU, с которым умели работать издавна. Таким образом, операционным системам было все равно, какой процессор установлен — с ММХ или без. Но для того чтобы реализовать преимущества SIMD, приложения должны "уметь" ими пользоваться (и не проиграть на переключениях).

Частое чередование кодов FPU и ММХ может снизить производительность за счет необходимости сохранения и восстановления весьма объемного контекста FPU.

Похожие работы

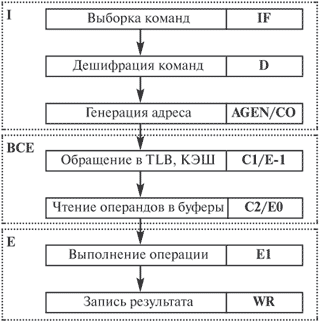

... Это почти все что касается самого общего рассказа о процессорах - почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным. 2.2. Алгоритм работы процессора Весь алгоритм работы процессора можно описать в трех строчках НЦ | чтение команды из памяти по адресу, записанному в СК | увеличение СК на длину прочитанной команды | ...

... руки журналистов называют «королем» системного блока, единовластно повелевающим всеми его ресурсами. Но уследить абсолютно за всем, что происходит в его «королевстве», даже шустрый процессор не в состоянии — королевская занятость разбрасываться не позволяет. И тогда на помощь «королю» приходят «наместники» — специализированные микропроцессоры-чипы по обработке, например, обычной и трехмерной ...

... потокового доступа к памяти. Однако эти изменения не дают никаких особых преимуществ в производительности, а носят скорее косметический характер. Мы же озаботимся вопросом практического функционирования процессора Intel Pentium III. Во-первых, необходимо иметь в виду, что для запуска системы на новом процессоре новая системная плата не требуется. Нужна всего-навсего обновленная версия BIOS, ...

... : -производитель чипсет, если возможно – модель материнской платы; -тактовые частоты процессора, памяти, системных шин; -названия, параметры работы всех системных и периферийных устройств; -расширенная информация о процессоре, памяти, жестких дисках, 3D-ускорителе; -разнообразные параметры программной среды: ОС, драйверы, процессы, системные файлы и т.д.; -информация о поддержке видеокартой ...

0 комментариев