Навигация

Выбор и обоснование функциональной схемы, элементной базы

1.2 Выбор и обоснование функциональной схемы, элементной базы

При работе дешифратора могут возникнуть следующие виды ошибок:

а) наличие двух или более активных сигналов на выходах дешифратора;

б) отсутствие активных сигналов на выходах дешифратора.

Схема контроля дешифратора (рис.3, рис.4) состоит из трех блоков:

а) входного блока - на него подаются сигналы с выходов дешифратора, над этими сигналами выполняются логические операции, после чего формируются выходные сигналы, необходимые для дальнейшего сравнения и анализа;

б) промежуточный блок - в этот блок поступают сигналы с входного блока, которые подвергаются сравнению и анализу, с выходов блока формируются сигналы, необходимые для формирования сигнала сообщающего о ошибке;

в) выходной блок - на него поступают сигналы из промежуточного блока, на основе этих сигналов формируется сигнал ошибки, если сигнал ошибки высокого уровня, т.е. лог.1, есть ошибка. Если лог.0 дешифратор сработал нормально, без ошибки.

В курсовом проекте рассматривается схема - 1, изображенная на рис.3. За счет инвертирующих элементов в схеме - 2 (рис.4), быстродействие ее больше, чем в первой схеме. Но схема - 1проще в построении, также в ней используется меньшее количество ИМС при построении схемы на печатной плате, что приводит к увеличению надежности работы схемы и меньшей ее цене.

Элементная база подбиралась по основным характеристикам: повышенное быстродействие, малая потребляемая мощность, минимальные токи потребления.

ИМС используемые в схеме:

ИМС - КР1533ЛИ1

Изготовлена по ТТЛШ - технологии, выпускается в полимерном корпусе.

Назначения выводов 1,2,4,5,9,10,12,13 - входы 1 - 4 лог. элементов, 3,6,8,11 - выходы лог. элементов. К 14 - выводу подключается Uпит, а вывод 7 является общим.

Параметры и эксплуатационные данные

Iпот - не более 4,0 мА Uвых - не более 0,5 В

Iпот - не более 2,4 мА Uвых - не менее 2,7 В

Iвх - не более 2 мкА tзд.р и tзд.р - не более 15 нс.

Iвх - не более 50 мкА Uпит - 5 В 5%

Tокр - от -10’C до +70’C

ИМС - КР1531ЛЛ1

Изготовлена по ТТЛШ - технологии, выпускается в полимерном корпусе.

Назначения выводов 1,2,4,5,9,10,12,13 - входы 1 - 4 лог. элементов, 3,6,8,11 - выходы лог. элементов. К 14 - выводу подключается Uпит, а вывод 7 является общим.

Параметры и эксплуатационные данные

Iпот - не более 15,5 мА Uвых - не более 0,5 В

Iпот - не более 8,3 мА Uвых - не менее 2,7 В

Iвх - не более -0,6 мА tзд.р. - не более 5,0 нс

Iвх - не более 20 мкА tзд.р - не более 5,5 нс

Uпит - 5 В 5% Tокр - от -10’С до +70’С

ИМС - К155ЛЕ4

Изготовлена по ТТЛ - технологии, выпускается в пластмассовом корпусе.

Назначения выводов 1,2,3,4,5,9,10,11,13 - входы 1 - 3 лог. элементов, 6,8,12 - выходы лог. элементов. К 14 - выводу подключается Uпит, а вывод 7 является общим.

Параметры и эксплуатационные данные

Iпот - не более 26 мА Uвых - не более 0,4 В

Iпот - не более 16 мА Uвых - не менее 2,4 В

Iвх - не более -1,6 мА tзд.р. - не более 11 нс

Iвх - не более 40 мкА tзд.р - не более 15 нс

Uпит - 5 В 5% Tокр - от -10’С до +70’С

ИМС - КР531ЛН1

Изготовлена по ТТЛШ - технологии, выпускается в пластмассовом корпусе.

Назначения выводов 1,3,5,9,11,13 - входы 1 - 6 лог. элементов, 2,4,6,8,10,12 - выходы лог. элементов. К 14 - выводу подключается Uпит, а вывод 7 является общим.

Параметры и эксплуатационные данные

Iпот - не более 54 мА Uвых - не более 0,5 В

Iпот - не более 24 мА Uвых - не менее 2,5 В

Iвх - не более -2,0 мА tзд.р. - не более 5 нс

Iвх - не более 50 мкА tзд.р - не более 4,5 нс

Uпит - 5 В 5% Tокр - от -10’С до +70’С

2. СПЕЦИАЛЬНАЯ ЧАСТЬ

Логический расчет схемы

Расчет входного блока

В входной блок (рис.3) поступают сигналы A0, A1, A2, A3, B0, B1, B2, B3 с дешифратора, после логических операций с четырех элементов выходного блока формируются сигналы E и S. Чтобы рассчитать выходные сигналы, нужно посмотреть табл.1. Из таблицы истинности видно, что сигнал E=1, только в том случае, если сигналы A и B равны лог. 1. На основе этого можно построить карту Карно, она приведена рядом, далее из карты можно получить следующую формулу для сигнала E:

Рис.3. Схема контроля дешифратора с прямыми выходами

Рис.4. Схема контроля дешифратора с инверсными выходами

E=AŸB

Для сигнала S получается следующая формула:

S=A+B,

Таблица 1.

Таблица истинности входного блока и карты Карно для сигналов E и S.

Карта Карно Карта Карно

для сигнала E для сигнала S

| A | B | E | S | B | B | B | B | |||||||

| 0 | 0 | 0 | 0 | A | 1 | A | 1 | 1 | ||||||

| 0 | 1 | 0 | 1 | A | A | 1 | ||||||||

| 1 | 0 | 0 | 1 | |||||||||||

| 1 | 1 | 1 | 1 |

Расчет промежуточного блока

Промежуточный блок состоит из двух под блоков, эти блоки полностью аналогичны. В промежуточный блок поступают сигналы E1,E2,S1 и S2 с элементов выходного блока,

после логических операций, в промежуточном блоке на выходах формируются сигналы E и S. Для логического расчета выходных сигналов, можно рассмотреть один из под блоков схемы.

Табл.2, по данным в таблицы истинности, строятся карты Карно, а из карт можно получить следующие формулы:

Формула для сигнала E:

E=E1+E2+S1ŸS2

Формула для сигнала S:

S=E1+E2+S1+S2=A0B0+A1B1+A1+B1+A2+B2=A0+B0+A1+B1=S1+S2

Таблица 2.

Таблица истинности промежуточного блока и карты Карно для сигналов Е и S.

Карта Карно

для сигнала E

| E1 | S1 | E2 | S2 | E | S | S1 | S1 | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | E1 | 1 | 1 | X | X | E2 | |||||||||||

| 0 | 0 | 0 | 1 | 0 | 1 | v | X | 1 | X | X | E2 | |||||||||||

| 0 | 0 | 1 | 0 | X | X | E1 | X | 1 | 1 | X | ||||||||||||

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | E2 | |||||||||||||||

| 0 | 1 | 0 | 0 | 0 | 1 | v | S2 | S2 | S2 | |||||||||||||

| 0 | 1 | 0 | 1 | 1 | 1 | |||||||||||||||||

| 0 | 1 | 1 | 0 | X | X | Карта Карно | ||||||||||||||||

| 0 | 1 | 1 | 1 | 1 | 1 | для сигнала S | ||||||||||||||||

| 1 | 0 | 0 | 0 | X | X | |||||||||||||||||

| 1 | 0 | 0 | 1 | X | X | S1 | S1 | |||||||||||||||

| 1 | 0 | 1 | 0 | X | X | E1 | 1 | 1 | X | X | E2 | |||||||||||

| 1 | 0 | 1 | 1 | X | X | X | 1 | X | X | E2 | ||||||||||||

| 1 | 1 | 0 | 0 | 1 | 1 | E1 | X | 1 | 1 | X | ||||||||||||

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | E2 | |||||||||||||

| 1 | 1 | 1 | 0 | X | X | S2 | S2 | S2 | ||||||||||||||

| 1 | 1 | 1 | 1 | 1 | 1 | |||||||||||||||||

v - комбинации получившиеся при нормальной работе дешифратора.

x - запрещенная комбинация, появляется только в том случае, если E1=1 и S1=0 или E2=1 и S2=0.

Похожие работы

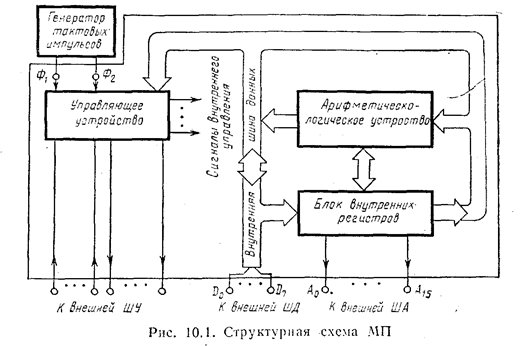

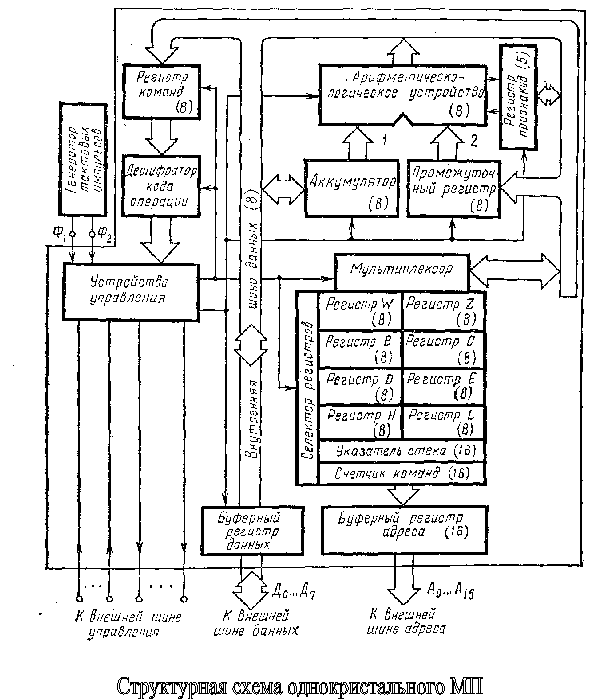

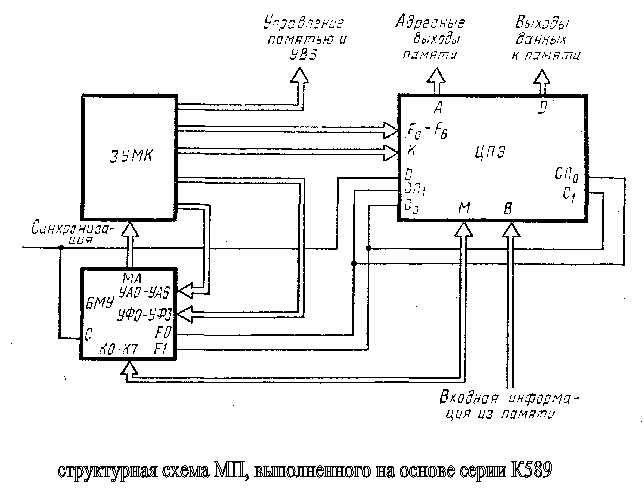

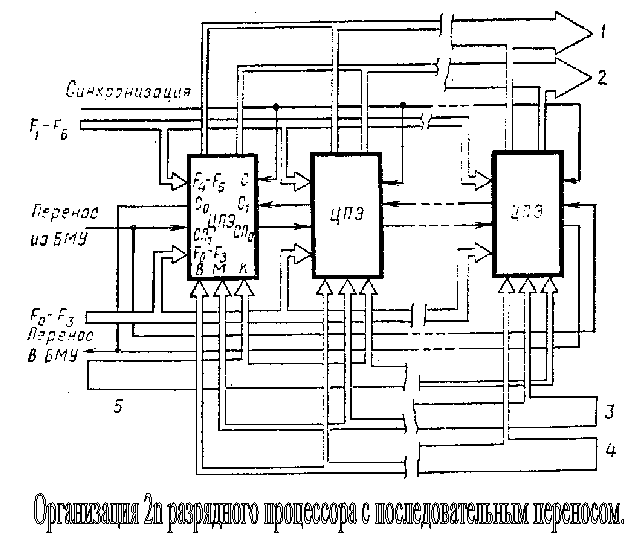

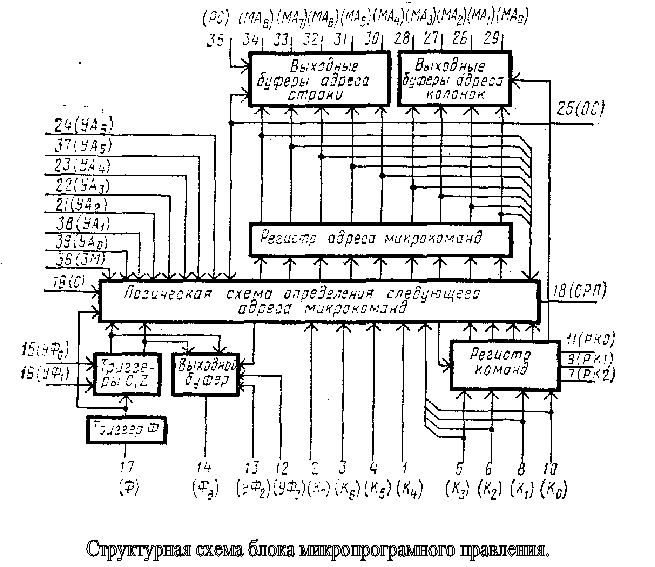

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

... РАССМОТРЕНИЕ РАЗЛИЧНЫХ ВАРИАНТОВ ПОСТРОЕНИЯ СТРУКТУРНОЙ СХЕМЫ Исходя из назначения устройства, можно представить устройство в виде некоего блока, который обеспечивает пространственно-временную коммутацию 256ти входящих цифровых каналов, в соответствии с сигналами УСТРОЙСТВА УПРАВЛЕНИЯ, и выравнивает входящие групповые каналы по циклам. Структурная схема такого устройства показана на рисунке 3.1. ...

... легко отображения и использования ключевых слов. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ПРОЕКТИРУЕМОЙ ЗАКАЗНОЙ БИС 5. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ГРУППОВОГО КАНАЛЬНОГО ИНТЕРФЕЙСА ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ .Любое цифровое устройство предназначено для выполнения той или иной логической функции, следовательно, такое устройство можно представить в ...

0 комментариев