Навигация

2.1.3 Расчет выходного блока

Из промежуточного блока в выходной поступают сигналы E1, S1, Е2 и S2. Эти сигналы необходимы, для формирования сигнала сообщающего об ошибке. После логических операций в выходном блоке, на его выходе формируется сигнал ERR. Таблица истинности и карта Карно для этого сигнала приведены в табл. 3, после всех логических преобразований формула для сигнала ERR получится следующая:

ERR=E1+E2+S1ŸS2+S1ŸS2

Таблица 3.

Таблица истинности и карта Карно для сигнала ERR

| E1 | S1 | E2 | S2 | ERR | Карта Карно | ||||||||||||||||||

| 0 | 0 | 0 | 0 | 1 | для сигнала ERR | ||||||||||||||||||

| 0 | 0 | 0 | 1 | 0 | v | ||||||||||||||||||

| 0 | 0 | 1 | 0 | X | S1 | S1 | |||||||||||||||||

| 0 | 0 | 1 | 1 | 1 | E1 | 1 | 1 | X | X | E2 | |||||||||||||

| 0 | 1 | 0 | 0 | 0 | v | X | 1 | X | X | E2 | |||||||||||||

| 0 | 1 | 0 | 1 | 1 | E1 | X | 1 | 1 | X | ||||||||||||||

| 0 | 1 | 1 | 0 | X | 1 | 1 | E2 | ||||||||||||||||

| 0 | 1 | 1 | 1 | 1 | S2 | S2 | S2 | ||||||||||||||||

| 1 | 0 | 0 | 0 | X | |||||||||||||||||||

| 1 | 0 | 0 | 1 | X | |||||||||||||||||||

| 1 | 0 | 1 | 0 | X | |||||||||||||||||||

| 1 | 0 | 1 | 1 | X | |||||||||||||||||||

| 1 | 1 | 0 | 0 | 1 | |||||||||||||||||||

| 1 | 1 | 0 | 1 | 1 | |||||||||||||||||||

| 1 | 1 | 1 | 0 | X | |||||||||||||||||||

| 1 | 1 | 1 | 1 | 1 | |||||||||||||||||||

v - ERR=0, ошибки нет - нормальная работа дешифратора.

x - запрещенная комбинация, получается только в том случае, если E1=1 и S1=0 или E2=1 и S2=0.

Похожие работы

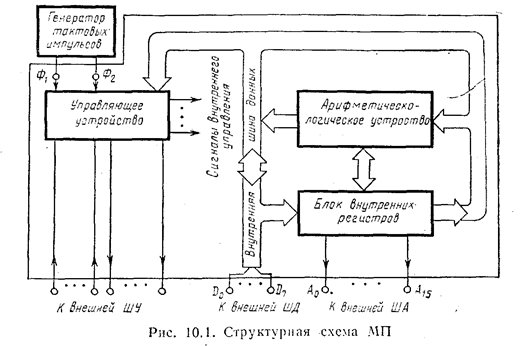

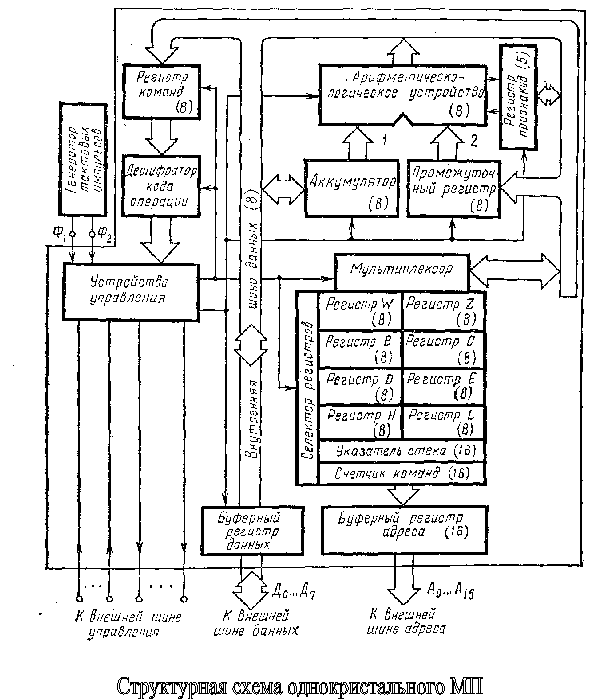

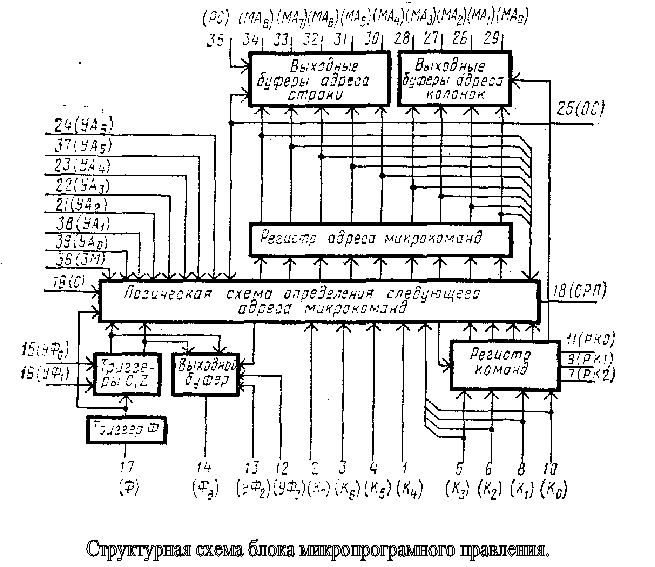

... БПП. Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами. Описание структурной схемы микропроцессора. В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров. Арифметическо-логическое устройство ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

... РАССМОТРЕНИЕ РАЗЛИЧНЫХ ВАРИАНТОВ ПОСТРОЕНИЯ СТРУКТУРНОЙ СХЕМЫ Исходя из назначения устройства, можно представить устройство в виде некоего блока, который обеспечивает пространственно-временную коммутацию 256ти входящих цифровых каналов, в соответствии с сигналами УСТРОЙСТВА УПРАВЛЕНИЯ, и выравнивает входящие групповые каналы по циклам. Структурная схема такого устройства показана на рисунке 3.1. ...

... легко отображения и использования ключевых слов. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ПРОЕКТИРУЕМОЙ ЗАКАЗНОЙ БИС 5. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ГРУППОВОГО КАНАЛЬНОГО ИНТЕРФЕЙСА ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ .Любое цифровое устройство предназначено для выполнения той или иной логической функции, следовательно, такое устройство можно представить в ...

0 комментариев