Навигация

Графический редактор печатных плат PC-CARDS

2.3. Графический редактор печатных плат PC-CARDS.

2.3.1. Назначение программы.

Графический редактор печатных плат PC-CARDS используется для решения следующих задач:

-построения/редактирования графического изображения конструкторско-топологического образа (конструктива) отдельного компонента электронного устройства (создается файл с расширением .PRT);

-построения/редактирования контура ПП, на которой осуществляется установка компонентов (создается файл с расширением .PCB);

-построения/редактирования топологии ПП в режиме ручного или полу автоматического проектирования;

-создания вспомогательных файлов для вывода чертежей на принтер, плоттер и фотоплоттер.

Принцип работы графического редактора печатных плат PC-CARDS тот же, что для редактора принципиальных схем PC-CAPS. Ряд команд идентичен. Далее расмотрим принципиальные различия графического редактора PC-CARDS.

Вызываеться программа PC-CARDS с помощью управляющей оболочки или непосредственно с помощью командной строки.

2.3.2. Общие принципы работы с графическим редактором PC-CARDS

После выбора в начальном меню режима Edit Database экран дисплея форматируется и разбивается на несколько зон аналогично экрану программы PC-CAPS (рис. 2.1).

При построение чертежа платы в системе P-CAD используются две системы единиц: английская (English unit) и метрическая (metric unit). В английской системе условная единица редактора PC-CARDS составляет 1 мил = 0,001 дюйма, т.е. 0,0254 мм, а в метрической системе - 0,01 мм. Максимальный размер чертежа, помещающегося в базе данных, составляет 60000 7& 060000 условных единиц. Текущие координаты курсора x, y указываются в самом правом поле строки состояния.

В английской системе единиц координаты приводятся в относительных единицах DBU, в метрической системе - в миллиметрах с точностью 0,01 мм.

2.3.3. Структура слоев чертежа.

В программе PC-CARDS полная информация о чертеже заносится в 45 цветовых слоёв, устанавливаемых по умолчанию. На каждой фазе работы с графическим редактором необходима не вся имеющаяся информация, поэтому часть слоев делают невидимыми, чтобы не перегружать чертеж. Пользователь может ввести новые слои, в частности, для проектирования многослойных ПП. Всего программа PC-CARDS поддерживает до 100 различных слоев.

Приведем структуру слоев графического редактора, устанавливаемую по умолчанию:

Имя Цвет Состоя-

слоя слоя ние по Назначение слоя

умолча-

нию

PADCOM 7 ON Графика контактных площадок на верхней

стороне платы (со стороны компонентов)

FLCOMP 7 OFF Информация для фотоплоттера о контактных

площадках на верхней стороне платы

PADSLD 8 OFF Графика контактных площадок на нижней

стороне платы

FLSOLD 8 OFF Информация для фотоплоттера о контактных

площадках на нижней стороне платы

PADINT 9 OFF Графика контактных площадок внутренних

слоев

FLINT 9 OFF Информация для фотоплоттера о контактных

площадках внутренних слоев

GNDCON 10 OFF Графика контактных площадок на слое "земли"

FLGCON 10 OFF Информация для фотоплоттера о контактных пло-

щадках на слое "земли"

CLEAR 12 OFF Графическая информация о зазорах

FLCLER 12 OFF Информация для фотоплоттера о зазорах

PWRCON 13 OFF Графика контактных площадок на слое полей и

шин питания

FLPCON 13 OFF Информация для фотоплоттера о контактных пло-

щадках на слое полей и шин питания

SLDMSK 14 OFF Графика маски пайки

FLSMSK 14 OFF Информация для фотоплоттера о маске пайки

DRILL 15 OFF Графическая информация о сверлении отверстий

FLDRLL 15 OFF Информация для фотоплоттера о контроле

сверления отверстий

PIN 4 ON Слой обозначений выводов (графика)

BRDOUT 4 ON Слой контура ПП

FLTARG 4 OFF Информация о реперных знаках на фотошаблонах

слоев

SLKSCR 6 ON Графика контуров компонентов для односторон-

него монтажа

DEVICE 5 ON Имена компонентов при размещении компонентов

на одной стороне ПП (используются при создании

псевдонимов по команде Alias программы PC-LIB)

ATTR 6 ON Слой атрибутов

REFDES 6 OFF Позиционные обозначения компонентов при

одностороннем монтаже

COMP 1 ABL Слой трассировки на верхней стороне платы

(сторона компонентов)

SOLDER 2 ABL Слой трассировки на нижней стороне платы

(сторона проводников)

INT1 14 OFF Первый внутренний слой трассировки

INT2 6 OFF Второй внутренний слой трассировки

DRLGIN 5 OFF Графика сверления внутренних слоев

DRLFIN 6 OFF Информация для фотоплоттера для контроля

сверления внутренних слоев

PINTOP 4 OFF Слой планарных контактных площадок на верхней

стороне платы

PINBOT 3 OFF Слой планарных контактных площадок на нижней

стороне платы

MSKGTP 13 OFF Графика маски пайки верхней стороны платы

MSKGBT 14 OFF Графика маски пайки нижней стороны платы

MSKFTP 3 OFF Информация для фотоплоттера о графике маски

пайки верхней стороны платы

MSKFBT 8 OFF Информация для фотоплоттера о графике маски

пайки нижней стороны платы

PSTGTP 1 OFF Графика пайки верхней стороны платы

PSTGBT 2 OFF Графика пайки нижней стороны платы

PSTFTP 12 OFF Информация для фотоплоттера о графике пайки

верхней стороны платы

PSTFBT 13 OFF Информация для фотоплоттера о графике пайки

нижней стороны платы

SLKTOP 6 ON Графика основных линий изображений планарных

компонентов на верхней стороне платы

SLKBOT 5 ON Графика основных линий изображений планарных

компонентов на нижней стороне платы

DVCTOP 1 ON Имена планарных компонентов на верхней сторо-

не платы

DVCBOT 2 ON Имена планарных компонентов на нижней сторо-

не платы

REFDTP 3 ON Позиционные обозначения планарных компонентов

на верхней стороне платы

REFDBT 6 ON Позиционные обозначения планарных компонентов

на нижней стороне платы

Первые 16 слоев PADCOM...FLDRLL используются для создания стеков контактных площадок. Слой COMP соответствует верхней стороне ПП (слой компонентов), слой SOLDER - нижней стороне. Слой INT1 - первый внутренний слой, INT2 - второй; при проектировании многослойных ПП остальные внутренние слои создаются пользователем. Слои 27-45 (начиная со слоя INT2), могут использоваться, в частности, для реализации технологии монтажа на поверхность (SMT, Surface-MountTechnology). Дополнительные внутренние слои и любые другие пользователь имеет возможность задать самостоятельно. Кроме того, по команде BARR программа PC-PLACE автоматически создает слои для:

а) запрета размещения компонентов:

BARTOP - на верхней стороне платы,

BARBOT - на нижней стороне платы,

BARPLC - на обеих сторонах платы;

б) запрета трассировки программе PC-ROUTE:

BARALL - на всех слоях,

BARCMP - на слое COMP,

BARSLD - на слое SOLDER,

BARIN1 - на внутреннем слое INT1,

BARVIA - запрет на создание переходных отверстий.

Выше приведена информация о слоях для определенной (американской) технологии. В каждой конкретной разработке пользователь может изменить их назначения и добавить новые слои, определяя самостоятельно распределение графической информации по слоям.

Похожие работы

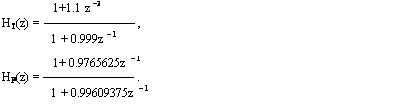

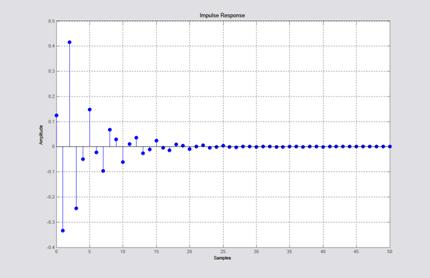

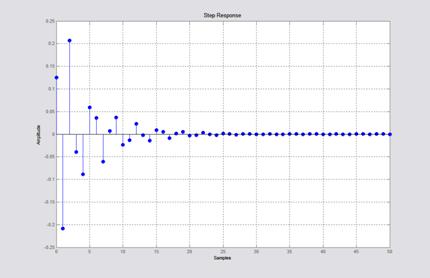

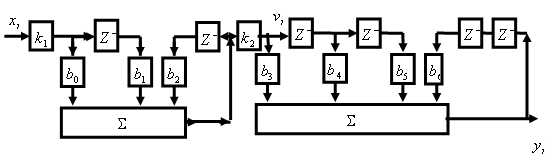

... , b2i , a2i определяют характеристики фильтра. При значениях коэффициентов фильтр имеет АЧХ фильтра верхних частот b 20 = 1;b 21 = 0;b 22 = 1.1; a 21 = 0.999;a 22 = 0.000 Разностное уравнение задает во временной области порядок получения выходной последовательности отсчетов из входной. В z-плоскости свойства цифрового фильтра описывает передаточная функция H(z), которая при двухкаскадной ...

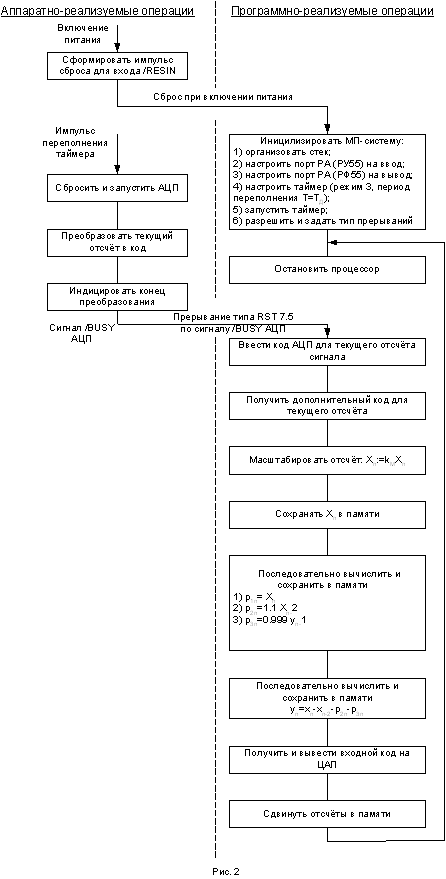

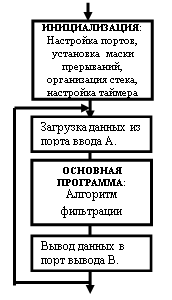

... для каждого звена составим разностные уравнения: 1) первое звено: ; 2) второе звено: ; 3) третье звено: . Результирующее разностное уравнение для цифрового фильтра будет иметь вид: .4 РАЗРАБОТКА АЛГОРИТМА ПРОГРАММЫ ПРОЕКТИРУЕМОГО УСТРОЙСТВА Прежде чем приступить к программированию устройства необходимо основательно изучить его внутреннюю структуру и возможности ресурсов. ...

... ) на 6400(так как масштабирующий коэффициент 26 =64 и амплитуда входного воздействия принята равной 100). (Как получены отрицательные значения?) Заключение В данной работе был спроектирован цифровой фильтр высокой частоты, удовлетворяющий всем требованиям технического задания. Проект занял на интегральной схеме 60% ресурсов или 694 логических ячеек. Были получены навыки программирования ПЛИС. ...

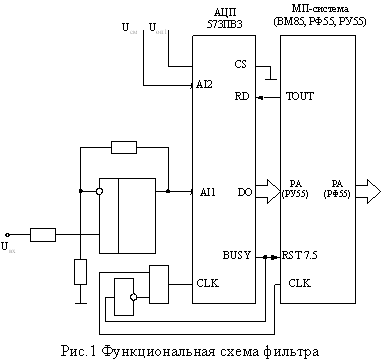

... интервал дискретизации Так как, tmax <Tд, то быстродействие устройства вполне достаточно для обработки выборки в реальном масштабе времени . Составление принципиальной схемы устройства и ее описание Принципиальная схема цифрового фильтра содержит след. микросхемы: DD1 – МП К1821ВМ85 DD2 – ПЗУ К1821РФ55 DD3 – ОЗУ К1821РУ55 DD4 – ЦАП К1108ПА1Б DА5 - ОУ К574УД1 DD6- К174ЛЕ5 ...

0 комментариев