Навигация

Процессор. Блок целочисленной арифметики.

Государственный комитет Российской Федерации

по высшему образованию

Казанский Государственный Технический Университет

имени А. Н. Туполева

----------------------------------------------------------------------------------------------

Кафедра электронно-вычислительных машин

Пояснительная записка

к курсовой работе по дисциплине

“Процессоры”

Тема: Блок целочисленной арифметики.

Студент: Базуев Ю.А. , гр. 4301

Руководитель: Бикмухаметов Р.Р.

Оценка______________________

Дата защиты__________________

Подпись руководителя__________

Казань 1996

Cодержание

1. Задание................................................................................................3

2. Алгоритм.............................................................................................4

2.1. Алгоритм умножения...................................................................4

2.2. Алгоритм деления.........................................................................4

3. Операционная схема и микропрограмма выполнения операций......5

4. Функциональная схема операционной части устройства..................8

5. Функциональная схема управляющей части....................................11

6. Принципиальная схема управляющей части....................................13

7. Таблица микрокоманд......................................................................15

8. Литература........................................................................................16

2. Алгоритм операций

2.1. Алгоритм умножения

Eдоп*Fдоп=Gдоп

Перед началом операции в RG1=Fдоп ; RG2=0 ; RG3=Eдоп

Знаки сомножителей участвуют в операции наравне с остальными разрядами, а это значит что Eдоп и Fдоп перемножаются как обычные (m+1) разрядные целые числа без знака. При этом знак Едоп участвует для того чтобы СЧП (сумма частичных произведений) в RG2 формировалась в доп. коде. Знак Fдоп участвует для того чтобы произведение формировалось в двойном формате.

В каждом из (m+1) циклов умножения производятся действия:

1) Eдоп прибавляется к RG2 если P4=1;

![]() 1

1

2) RG2, RG1, Tзн при сдвиге вправо необходимо сохранять представление СЧП в доп. коде, а это значит что слева нужно вводить 0, если число =>0 и 1, если число < 0.

2.2. Алгоритм деления

Gдоп/Eдоп=Fдоп

а) устанавливаем начальные значения регистров и триггеров

б) сдвигаем делимое на 1 разряд влево

в) анализируем знаки Gi-1 и E. Если одинаковы то вычитаем E из GR2.

Если разные то + E к RG2

г) анализируем знаки Giи E, если одинаковые то цифра частного =1

д) анализируем ТФ, если ТФ=1 выполняем проверку на ПРС 2-го этапа

е) уменьшаем значение счетчика циклов

ж) если счетчик не = 0 то переходим на пункт б)

з) передаем частное в RG1

и) корректируем частное

к) выдаем частное на выходную шину

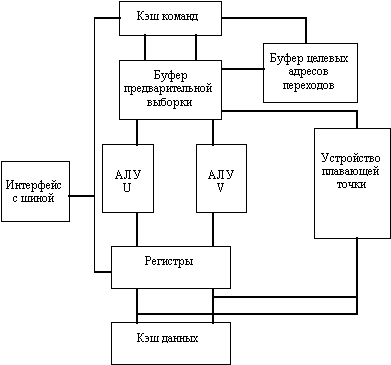

3. Операционная схема и микропрограмма выполнения

операций

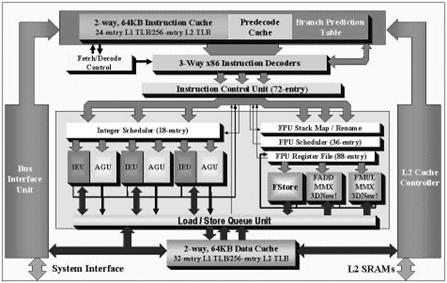

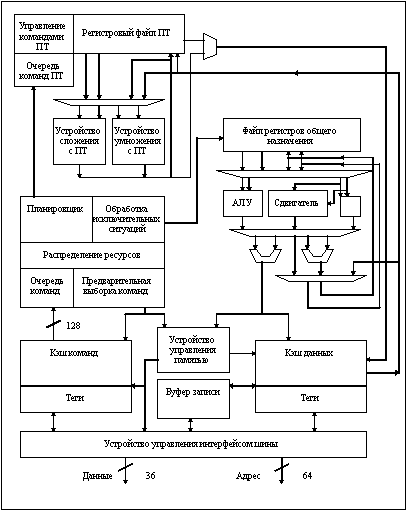

В соответствии с алгоритмом строим ОС (рис. 1) , определяем требуемый набор МО и граф МП (рис. 2) , считая что в RG3 выполняется однотактным способом (по входам D триггеров RG2) по сигналу у4; в RG1 - двухтактным способом (по входам R и S) по сигналам у6 и у7.

В ОС на Рис. 1 использованы следующие обозначения:

Тпп - триггер переполнения

Тпер - триггер переноса

Тзн1 - триггер знака множимого, флаговый триггер при делении

Тзн2 - триггер знака Gi-1

Тзн3 - триггер знака делимого

Х(8:0) - входная шина

Z(8:0) - выходная шина

В МП на Рис. 2 введены 15 осведомительных сигнала:

Р1= RG3(8) Р10 = Р1 Å Р3

Р2 = a Р11 = Р3 Å Р1

Р3 = RG2(8) P12 = P6 Å Р5

Р9 = RG2(7) Å RG2(6) P13 = P1 Tзн2 v P1 Tзн2

P4 = 1 (CT=0) P14 = Tпер

Р5 = RG1(0) Р15 = Тзн1

Р6 = Р1 Tзн2v Tзн2Р1

Р7 = 1 (RG2(8:0)=0)

Р8 = Тзн3

a - внешний сигнал определяющий вид операции

( 0 - умножение ; 1 - деление )

а также 17 импульсных управляющих сигналов:

у1: { RG2=RG2(8:0).RG1(8); у10: Тпп=1

RG1=RG1(7:0).0 } у11: RG2=RG1

y2: RG2=RG2+RG3+1 y12: RG2=RG2+1

y3: RG2=RG2+RG3 y13: Z=RG2

y4: RG3=X y14: { RG1=RG2(0).RG1(8:1);

y5: { RG2=X ; Tзн1=1 } Tзн1=RG1(0) }

y6: { RG1=X; Tзн3=P3; Tпп=0; y15: RG2=0.RG2(8:1)

СТ=9; Тпер=0; } y16: RG2=1.RG2(8:1)

y7: RG1(0)=1 y17: RG2=0

y8: Тзн1=0

у9: СТ=СТ-1

Z(8:0)

![]()

![]() у13

Р15

у13

Р15

![]()

![]() Р5

Р5

![]()

![]()

![]()

![]() зн RG1 1

1 Тзн1

зн RG1 1

1 Тзн1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 8 7 0

8 7 0

![]()

![]()

![]() у6 у1 у14 у7

у6 у1 у14 у7

Р2

![]()

![]() Р3 у18

Р3 у18

![]()

![]()

![]()

![]()

![]() Тзн2

зн 1 1

Тзн2

зн 1 1

![]()

![]()

![]()

![]()

![]()

![]() 8 7 6 RG2 0

8 7 6 RG2 0

![]() у16 у5 у1 у15 ,у16

у16 у5 у1 у15 ,у16

![]()

![]()

Р14

![]()

![]()

![]()

![]() Тпер

зн KSM у2 , у12

Тпер

зн KSM у2 , у12

![]()

![]() 8 7 0

8 7 0

![]()

![]()

![]() P1 у3 у2

P1 у3 у2

![]()

![]()

![]() зн

зн

8 7 RG3 0

![]()

![]() у4

у4

![]()

Х(8:0)

Р4 ПРС Р8

|  |  |

СТ Тпп Тзн3

Рис. 1.

![]() начало

начало

![]()

![]()

![]()

![]() 2

2

![]()

![]()

![]()

![]() a

a

![]()

![]()

![]() 0 1 5

0 1 5

![]()

![]() y6 6

y6 6

![]()

![]()

![]()

![]()

![]() y17 1 9

y17 1 9

![]()

![]()

![]()

![]()

![]() 0

0

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 0

2 11 3

0

2 11 3

![]()

![]()

![]()

![]()

![]()

![]() P5

P5

![]()

![]()

![]()

![]()

![]() 1 1

10

1 1

10

![]()

![]() y3 7

y3 7

![]()

![]()

![]()

![]()

![]()

![]()

![]() 0 0 15 0

0 0 15 0

![]()

![]()

![]()

![]()

![]() P3 P14 1

P3 P14 1

![]()

![]()

![]()

![]() 1 1 1 12

1 1 1 12

![]()

![]()

![]() 0 8

0 8

![]()

![]()

![]()

![]()

![]() P1 9

P1 9

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1 0 4

1 0 4

![]()

![]() y16, y14, y9 y15, y14, y9 3

y16, y14, y9 y15, y14, y9 3

![]()

![]() 1

1

![]()

![]()

![]()

![]()

![]()

![]() 3 1 1 2

3 1 1 2

![]()

![]()

![]()

![]()

![]() 0

0

![]()

![]()

![]()

![]()

![]() P4 7 0

P4 7 0

![]()

![]()

![]()

![]()

![]()

![]() 1 8

1 8

![]()

![]() 0 1

0 1

![]()

![]()

![]()

![]()

![]()

![]() P15

2 1 3

P15

2 1 3

![]()

![]()

![]() 1

1

![]()

![]() y2

13

y2

13

![]()

![]() 11

11

![]()

![]()

![]()

![]()

![]() 8 1 13

8 1 13

![]()

![]()

![]() y13 1

y13 1

![]()

![]()

![]() 0 1

0 1

![]()

![]() 12

12

![]()

![]() y11

y11

![]() 0 8

0 8

![]()

![]() 0

0

![]() 0 3

0 3

1

1

![]()

![]() 10

10

у13

у13

![]()

конец

Рис. 2.

Похожие работы

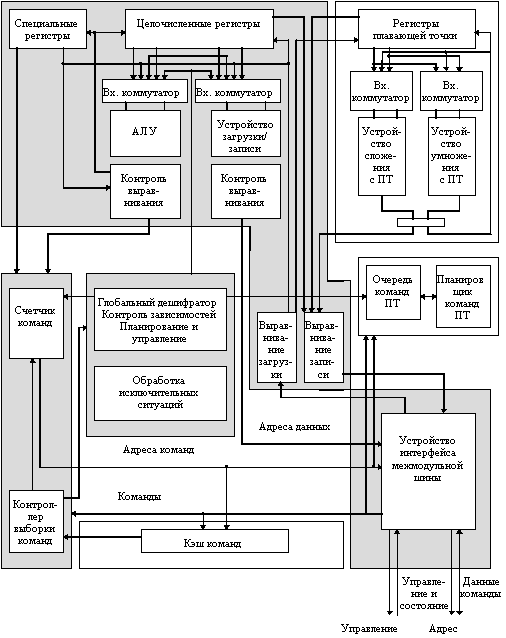

... изменения сегмента (Segment Override). В системе команд насчитывается несколько сотен инструкций, поэтому в данной работе обзорно рассмотрены все команды обработки данных (блоков процессора АЛУ, FPU, MMX, и XMM), а далее более подробно описаны инструкции, появившиеся в процессорах Pentium 3 (блок XMM — SSE) и Pentium 4 (блок XMM — SSE2). Инструкции пересылки данных (см. табл) позволяют ...

... Это почти все что касается самого общего рассказа о процессорах - почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным. 2.2. Алгоритм работы процессора Весь алгоритм работы процессора можно описать в трех строчках НЦ | чтение команды из памяти по адресу, записанному в СК | увеличение СК на длину прочитанной команды | ...

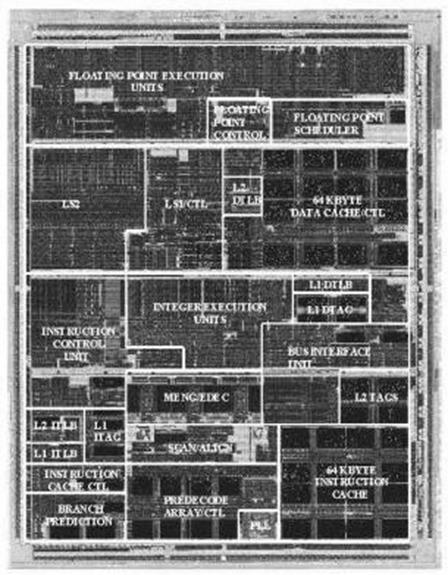

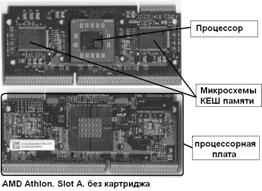

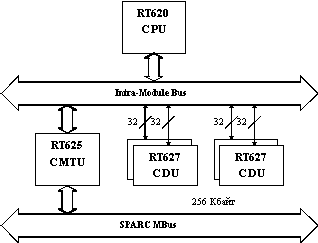

... -инструкций 3DNow!, расширенный дополнительными командами. Всего 45 команд. Ø Выпускаются версии с частотами 500, 550, 600 , 650 и 700МГц. 3. Архитектура процессора AMD Athlon (Thunderbird) Процессор седьмого поколения AMD Athlon (Thunderbird) использует, на данный момент наиболее совершенную микроархитектуру x86. Сочетание указанных ниже свойств предоставляет тем, кто работает с ...

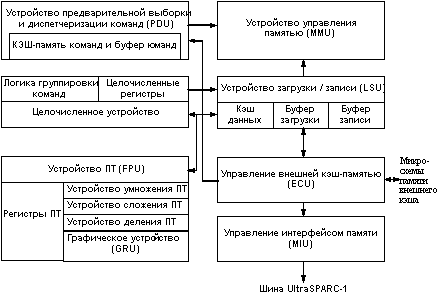

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

0 комментариев