Навигация

Функциональная схема операционной части

4. Функциональная схема операционной части

устройства

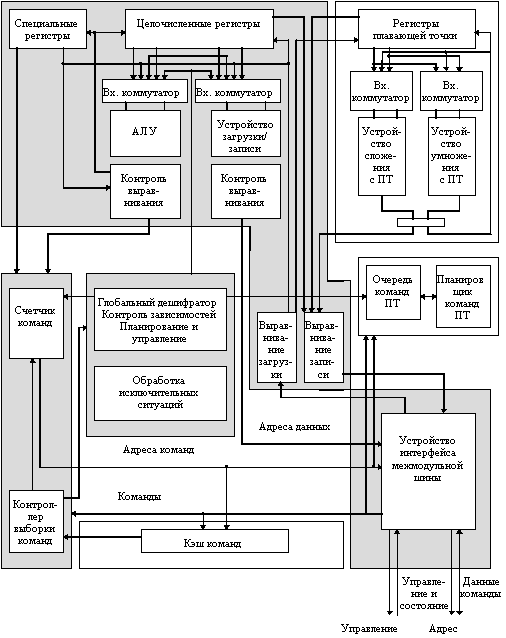

На Рис. 3. представлена функциональная схема операционной части (ОЧ) на регистрах и мультиплексорах. В схему из УЧ подаются 15 импульсных управляющих сигналов с длительностью, равной 50 нс, причем часть управляющих сигналов ( у2 , у3 , у12 ) подаются на входы синхронизации регистров и одновременно участвуют в формировании сигналов на информационных входах триггеров с помощью различных комбинационных схем. Следовательно, во-первых, если время задержки упомянутых комбинационных схем превышает значение 50 нс, то схемой пользоваться нельзя, так как к моменту переключения триггеров сигналы на их информационных входах не успеют сформироваться. Например, сигнал у3 должен иметь длительность, достаточную для того, чтобы успели сработать элементы 2,3 и4 ступеней схемы, иначе в момент окончания у4 в RG2 зафиксируется неправильный результат. Таким образом, в данной схеме длительность сигналов МО должна определяться по времени выполнения самой длительной МО, которое при заданной элементной базе превышает заданное значение.

Во-вторых, так как сигналы на входах “С” и “D” триггеров RG2 при выполнении у2 , у3 и у12 оканчиваются одновременно (без учета задержек сигналов в комбинационных схемах), то триггеры могут не переключиться требуемым образом из-за возможной “игры фронтов” на входах “С” и “D”.

Для решения указанных проблем с целью повышения быстродействия и надежности схемы разобьем все МО на 2 группы.

В первую группу выделим МО у2 , у3 и у12 , связанные не только с переключением триггеров по входам синхронизации, но и с формированием сигналов на информационных входах этих триггеров.

Во вторую все остальные МО, для выполнения которых достаточны импульсные управляющие сигналы с длительностью равной 50 нс. Как правило, в эту группу входят действия, связанные с переключением триггеров по асинхронным входам, либо по входам синхронизации, если сигналы на информационных входах триггеров при этом не меняются.

Для выполнения МО 1-ой группы необходимы дополнительные потенциальные управляющие сигналы (сигналы с длительностью, не меньшей такта Т) , называемые микроприказами. Тогда импульсные управляющие сигналы подаются лишь на входы синхронизации триггеров, а формирование сигналов на информационных входах этих триггеров осуществляется с помощью микроприказов, которые должны поступать в схему ранее и заканчиваться позднее сигналов на входах синхронизации триггеров.

В управляющей части с программируемой логикой микроприказы формируются с помощью разрядов операционного поля микрокоманы, считываемой из управляющей памяти. Обозначим эти разряды и соответствующие им микроприказы через МК(j) , где j = 0 , 1 , 2 , ...

Если использовать три микроприказа, то схема Рис.3. преобразуется к виду, представленному на Рис.4 (без цепей записи со входной шины, без триггеров Тпп , Тзн3 , счетчика циклов и цепи выдачи на выходную шину). Здесь: во-первых, отсутствует триггер переноса, так как при использовании микроприказов сигнал переноса на выходе KSM становится потенциальным, и необходимость в его запоминании отпадает.

Во-вторых, сигналы у15 , у16 , у5 поступающие на один и тот же вход сдвига вправо RG2 , заменен одним сигналом у5 .

С целью упрощения ОЧ устройства заменим 2, 3 ступени схемы на Рис. 4. арифметико-логическим устройством (АЛУ). Тогда количество микроприказов увеличится до 5.

Функциональная схема ОЧ устройства, в которой применяется АЛУ, представлена на Рис. 5. Здесь АЛУ используется для выполнения трех действий, определяемых таблицей 1.

Таблица 1.

| S3 | S2 | S1 | S0 | F` |

| 0 | 0 | 0 | 0 | A` + C0 |

| 0 | 0 | 0 | 1 | A` + B` + C0 |

| 0 | 1 | 1 | 0 | A` - B` - C0 |

В таблице А` и B` - значения операндов, поступающих в АЛУ, F` - значение результата, формируемого на входах АЛУ; С0 - значение сигнала на входе переноса младшего разряда АЛУ.

В соответствии с таблицей 1 в схеме Рис 5. использованы пять микроприказов: МК(0) - S0 , MK(1) - S1 , MK (2) - S2 , MK(3) - C0 , MK(4) - вход данных вдвигаемых при сдвиге вправо на RG2.

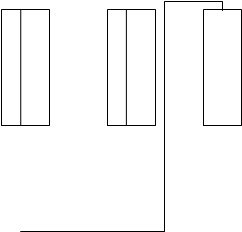

Работа схемы определяется МП, представленной на Рис. 6. Список используемых импульсных сигналов:

у1: { <RG2=\/ ; у10: Тпп=1

<RG1=\/ ; C Тзн2=/\ } у11: RG2=0

y2: С RG2=\/ y12: Z=RG2

y3: { >RG2=\/ ; >RG1=\/ }

y4: RG3=X

y5: RG2=RG1;

y6: { RG1=X; Tзн3=P3; Tпп=0;

Тзн1=1; СТ=9; }

y7: RG1(0)=1

y8: Тзн1=0

у9: СТ=СТ-1

![]() 9

9

X(8 : 0)

X(8 : 0)

| |||||||

|  |  | |||||

![]()

RG3 MS KSM 0 MS D RG2 D RG1

RG3 MS KSM 0 MS D RG2 D RG1

![]()

![]()

![]()

![]()

![]()

![]()

![]() D

0

1 < > 0 < > 0

D

0

1 < > 0 < > 0

![]()

![]()

Похожие работы

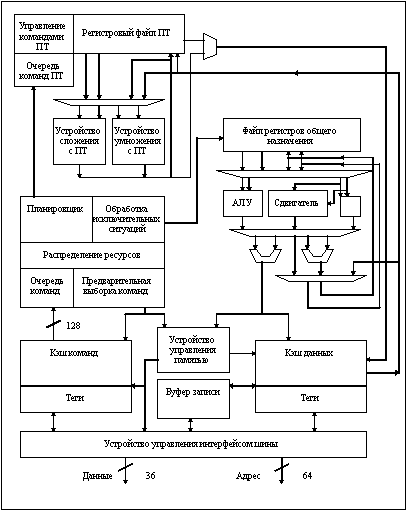

... изменения сегмента (Segment Override). В системе команд насчитывается несколько сотен инструкций, поэтому в данной работе обзорно рассмотрены все команды обработки данных (блоков процессора АЛУ, FPU, MMX, и XMM), а далее более подробно описаны инструкции, появившиеся в процессорах Pentium 3 (блок XMM — SSE) и Pentium 4 (блок XMM — SSE2). Инструкции пересылки данных (см. табл) позволяют ...

... Это почти все что касается самого общего рассказа о процессорах - почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным. 2.2. Алгоритм работы процессора Весь алгоритм работы процессора можно описать в трех строчках НЦ | чтение команды из памяти по адресу, записанному в СК | увеличение СК на длину прочитанной команды | ...

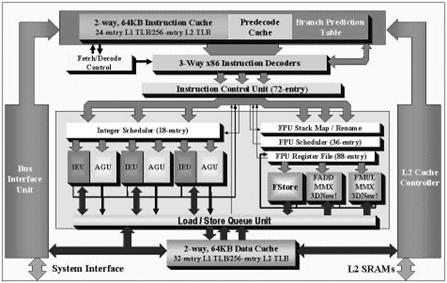

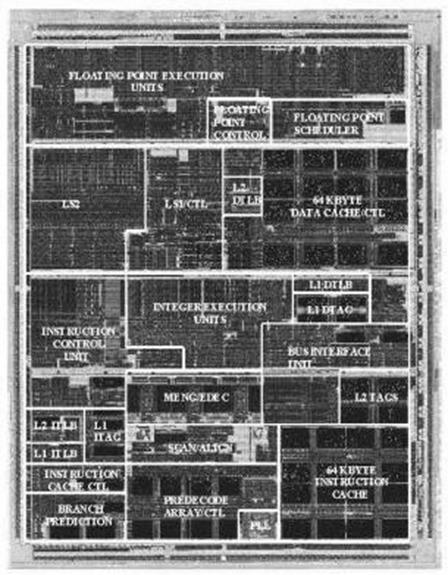

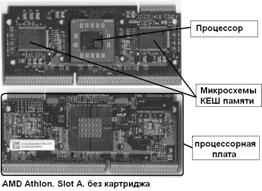

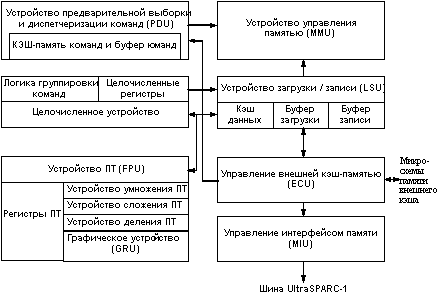

... -инструкций 3DNow!, расширенный дополнительными командами. Всего 45 команд. Ø Выпускаются версии с частотами 500, 550, 600 , 650 и 700МГц. 3. Архитектура процессора AMD Athlon (Thunderbird) Процессор седьмого поколения AMD Athlon (Thunderbird) использует, на данный момент наиболее совершенную микроархитектуру x86. Сочетание указанных ниже свойств предоставляет тем, кто работает с ...

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

0 комментариев