Навигация

2. Внутренний кэш процессора

Внутренне кэширование обращений к памяти применяется в процессорах, начиная с 486-го. С кэшированием связаны новые функции процессоров, биты регистров и внешние сигналы.

Процессоры 486 и Pentium имеют внутренний кэш первого уровня, в Pentium Pro и Pentium II имеется и вторичный кэш. Процессоры могут иметь как единый кэш инструкций и данных, так и общий. Выделенный кэш инструкций обычно используется только для чтения. Для внутреннего кэша обычно используется наборно-ассоциативная архитектура.

Строки в кэш-памяти выделяются только при чтении, политика записи первых процессоров 486 – только Write Through (сквозная запись) – полностью программно-прозрачная. Более поздние модификации 486-го и все старшие процессоры позволяют переключаться на политику Write Back (обратная запись).

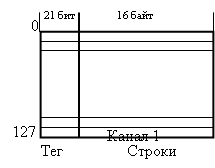

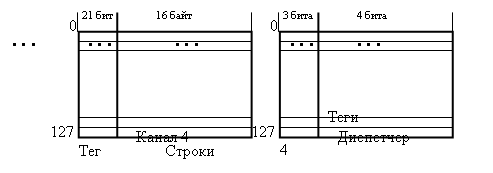

Работу кэша рассмотрим на примере четырехканального наборно-ассоциативного кэша процессора 486. Кэш является несекторированным – каждый бит достоверности (Valid bit) относится к целой строке, так что стока не может являться “частично достоверной”.

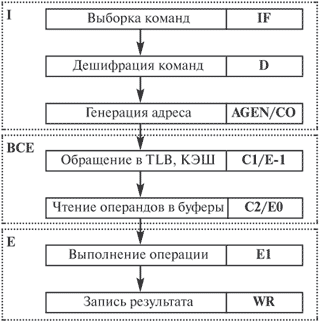

Работу внутренней кэш-памяти характеризуют следующие процессы: обслуживание запросов процессора на обращение к памяти, выделение и замещение строк для кэширования областей физической памяти, обеспечение согласованности данных внутреннего кэша и оперативной памяти, управление кэшированием.

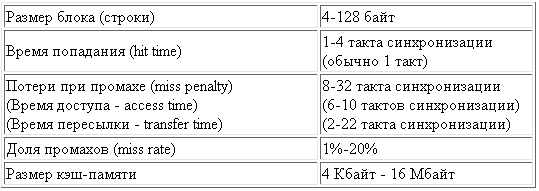

Любой внутренний запрос процессора на обращение к памяти направляется на внутренний кэш. Теги четырех строк набора, который обслуживает данный адрес, сравниваются со старшими битами запрошенного физического адреса. Если адресуемая область представлена в строке кэш-памяти (случая попадания –cache hit), запрос на чтение обслуживается только кэш-памятью, не выходя на внешнюю шину. Запрос на запись модифицирует данную строку, и в зависимости от политики записи либо сразу выходит на внешнюю шину (при сквозной записи), либо несколько позже (при использовании алгоритма обратной записи).

В случае промаха (Cache Miss) запрос на запись направляется только на внешнюю шину, а запрос на чтение обслуживается сложнее. Если этот зарос относится к кэшируемой области памяти, выполняется цикл заполнения целой строки кэша – все 16 байт (32 для Pentium) читаются из оперативной памяти и помещаются в одну из строк кэша, обслуживающего данный адрес. Если затребованные данные не укладываются в одной строке, заполняется и соседняя. Заполнение строки процессор старается выполнить самым быстрым способом – пакетным циклом с 32-битными передачами (64-битными для Pentium и старше).

Внутренний запрос процессора на данные удовлетворяется сразу, как только затребованные данные считываются из ОЗУ – заполнение строки до конца может происходить параллельно с обработкой полученных данных. Если в наборе, который обслуживает данный адрес памяти, имеется свободная строка (с нулевым битом достоверности), заполнена будет она и для нее установится бит достоверности. Если свободных строк в наборе нет, будет замещена строка, к которой дольше всех не было обращений. Выбор строки для замещения выполняется на основе анализа бит LRU (Least Recently Used) по алгоритму “псевдо-LRU”. Эти биты (по три на каждый из наборов) модифицируются при каждом обращении к строке данного набора (кэш-попадании или замещении).

Таким образом, выделение и замещение строк выполнятся только кэш-промахов чтения, при промахах записи заполнение строк не производится. Если затребованная область памяти присутствует в строке внутреннего кэша, то он обслужит этот запрос. Управлять кэшированием можно только на этапе заполнения строк; кроме того, существует возможность их аннулирования – объявления недостоверными и очистка всей кэш-памяти.

Очистка внутренней кэш-памяти при сквозной записи (обнуление бит достоверности всех строк) осуществляется внешним сигналом FLUSH# за один такт системной шины (и, конечно же, по сигналу RESET). Кроме того, имеются инструкции аннулирования INVD и WBINVD. Инструкция INVD аннулирует строки внутреннего кэша без выгрузки модифицированных строк, поэтому ее неосторожное использование при включенной политике обратной записи может привести к нарушению целостности данных в иерархической памяти. Инструкция WBINVD предварительно выгружает модифицированные строки в основную память (при сквозной записи ее действие совпадает с INVD). При обратной записи очистка кэша подразумевает и выгрузку всех модифицированных строк в основную память. Для этого, естественно, может потребоваться и значительное число тактов системной шины, необходимых для проведения всех операций записи.

Аннулирование строк выполняется внешними схемами – оно необходимо в системах, у которых в оперативную память запись может производить не только один процессор, а и другие контроллеры шины – процессор или периферийные контроллеры. В этом случае требуются специальные средства для поддержания согласованности данных во всех ступенях памяти – в первичной и вторичной кэш-памяти и динамического ОЗУ. Если внешний (по отношению к рассматриваемому процессору) контроллер выполняет запись в память, процессору должен быть подан сигнал AHOLD. По этому сигналу процессор немедленно отдает управление шиной адреса A[31:4], на которой внешним контроллером устанавливается адрес памяти, сопровождаемый стробом EADS#. Если адресованная память присутствует в первичном кэше, процессор аннулирует строку – сбрасывает бит достоверности этой строки (она освобождается). Аннулирование строки процессор выполняет в любом состоянии.

Управление заполнением кэша возможно и на аппаратном и на программном уровнях. Процессор позволяет кэшировать любую область физической памяти, но внешние схемы могут запрещать процессору кэшировать определенные области памяти. Это делается по различным причинам, зачастую связанным с определенными условиями создания компьютерной системы.

Похожие работы

... : -производитель чипсет, если возможно – модель материнской платы; -тактовые частоты процессора, памяти, системных шин; -названия, параметры работы всех системных и периферийных устройств; -расширенная информация о процессоре, памяти, жестких дисках, 3D-ускорителе; -разнообразные параметры программной среды: ОС, драйверы, процессы, системные файлы и т.д.; -информация о поддержке видеокартой ...

... на блоки с фиксированным числом слов и обмен данными между основной памятью и кэш-памятью выполняется блоками. При доступе к некоторому адресу центральный процессор должен сначала определить содержит ли кэш-память копию блока с указанным адресом, и если имеется, то определить, с какого адреса кэш-памяти начинается этот блок. Эту информацию ЦП получает с помощью механизма преобразования адресов. На ...

... для всех процессоров нового поколения. Выводы Анализ изложенного выше материала позволяет сделать заключение, что в соответствии с каноническими теориями, современные производители широко используют кэш-память при построении новейших процессоров. Во многом, их превосходные характеристики по быстродействию достигаются именно благодаря применению кэш-памяти второго и даже третьего уровня. Этот ...

... адресов ячеек памяти —весь объем памяти делится на два или несколько банков. Двойные слова с последовательными адресами располагаются в разных банках. Во время считывания информации из оперативной памяти за один цикл можно организовать параллельное извлечение информации из разных блоков, что уменьшает количество циклов ожидания. Преимущество систем с интерливингом проявляется при ...

0 комментариев