Навигация

Цессор

![]() К шине ной

К шине ной

Управления 21 сис-

![]()

![]()

![]() теме

теме

![]()

![]() С3

С3

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 3

3

![]()

![]() R4

R4

![]()

![]()

![]()

![]() С4 R3

С4 R3

Можно использовать резонаторы, имеющие резонансную частоту:

1) 32768 Гц

2) 1048576 Гц

3) 4194304 Гц

Ток потребления зависит от fr.

f=32768 Гц In![]() мкА

мкА

при ![]() f Iпотр может доходить до 4 мА.

f Iпотр может доходить до 4 мА.

Сигнал тактового генератора можно снять с выхода CKOUT для использования в других устройствах системы. Он поступает на этот вход непосредственно (CKFS=1) или после деления частоты на четыре (CKFS=0). Микросхема имеет выход ещё одного сигнала (SQW), получаемого делением частоты тактового генератора. Коэффициент деления задается командами, поступающими от процессора. Включается и выключается этот сигнал также командами процессора.

Распределение памяти микросхемы 512ВИ1:

| Адрес | Данные |

| 00Н 01 02 03 04 05 06 07 09 0А 0В 0С 0D OE-3 FH | Секунды Секунды (будильник) Минуты Минуты (будильник) Часы Часы (будильник) День недели День месяца Месяц Год Регистр А Регистр В Регистр С Регистр D ОЗУ общего назначения |

Микросхема связана с микропроцессором через двунаправленную мультиплексированную шину адреса – данных (AD0![]() AD7). Для управления записью и считыванием информации служат входы

AD7). Для управления записью и считыванием информации служат входы ![]() (выбор микросхемы), AS (строб, адреса), DS (строб данных) и R/

(выбор микросхемы), AS (строб, адреса), DS (строб данных) и R/![]() (чтение – запись).

(чтение – запись).

![]() - «1» шина AD, входы DS и R/

- «1» шина AD, входы DS и R/![]() отключены от шин процессора и снижается мощность потребления.

отключены от шин процессора и снижается мощность потребления.

![]() - «0» должен сохраняться неизменным во время всего цикла записи и чтения.

- «0» должен сохраняться неизменным во время всего цикла записи и чтения.

Сигнал AS подается в виде положительного импульса во время наличия информации об адресе на шине AD0![]() AD7. Адреса записываются во внутренний буфер микросхемы по срезу этого импульса.

AD7. Адреса записываются во внутренний буфер микросхемы по срезу этого импульса.

В этот же момент анализируется логический уровень сигнала на входе DS и в зависимости от него устанавливается дальнейший режим работы входов DS и R/![]() . В нашем случае на вход AS подаем сигнал ALE, который генерируется процессором для фиксации адреса.

. В нашем случае на вход AS подаем сигнал ALE, который генерируется процессором для фиксации адреса.

Если при AS – «1»-![]() «0» DS – «0», то

«0» DS – «0», то

запись производится при DS – «1», R/![]() -«0»,

-«0»,

а чтение производится при DS – «1», R/![]() -«1».

-«1».

Если во время среза импульса AS (AS – «1» ![]() «0») DS – «1», то для считывания необходимо DS-«0» R/

«0») DS – «1», то для считывания необходимо DS-«0» R/![]() -«1»,

-«1»,

а для записи DS-«1» R/![]() -«0».

-«0».

Такая сложная логика используется для подключения к микропроцессорам различных типов. На вход R/![]() будем подавать сигнал WR, а на вход DS-RD, которые генерируются процессором.

будем подавать сигнал WR, а на вход DS-RD, которые генерируются процессором.

Выход ![]() (запрос прерывания) предназначен для сигнализации процессору о том, что внутри микросхемы произошло событие, требующее программной обработки. Прерывания бывают 3-х типов:

(запрос прерывания) предназначен для сигнализации процессору о том, что внутри микросхемы произошло событие, требующее программной обработки. Прерывания бывают 3-х типов:

1) после окончания обновления информации

2) по будильнику

3) периодические (с периодом SQW)

Вход ![]() предназначен для установки в исходное состояние узлов микросхемы, ответственных за связь с микропроцессорной системой.

предназначен для установки в исходное состояние узлов микросхемы, ответственных за связь с микропроцессорной системой. ![]() - «0» – никакое вмешательство со стороны процессора невозможно. На ход часов, календарь и содержание ячеек ОЗУ этот вход не влияет.

- «0» – никакое вмешательство со стороны процессора невозможно. На ход часов, календарь и содержание ячеек ОЗУ этот вход не влияет.

Вход PS (датчик питания) – контроль непрерывности подачи питающего напряжения. Он подключается таким образом, чтобы напряжение на нем падало до 0 при любом, даже кратковременном отключения питания микросхемы.

Для управления работой микросхемы и анализа её состояния предназначены регистры А…D.

Формат управляющих регистров:

| Адрес | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| OAH OBH OCH ODH | UIP* SETIRQF* VRT* | DV2 PIE PF* O* | DV1 AIE AF* O* | DV0 VIE VF* O* | RS3 SQWE O* O* | RS2 DM O* O* | RS1 24/12 O* O* | RS0 DSE O* O* |

* - можно только считывать информацию.

Регистр А.

UIP – единица в этом разряде означает, что происходит или начнется менее чем через 244 мкс обновление информации о времени. На UIP не действует сигнал ![]() . Записав единицу в разряд SET регистра В, можно запретить обновление и тем самым сбросить UIP.

. Записав единицу в разряд SET регистра В, можно запретить обновление и тем самым сбросить UIP.

DVO…DV2 – устанавливает режим работы внутреннего делителя частоты в соответствии с используемой опорной частотой.

Установка опорной частоты:

| DV2 | DV1 | DV0 | Частота |

| 0 0 0 1 | 0 0 1 1 | 0 1 0 0 | 4194304 Гц 1048576 Гц 32768 Гц сброс делителя |

RS0…RS3 – устанавливает частоту сигнала на входе SQW и период повторения периодических колебаний.

| RS3 | RS2 | RS1 | RS0 | f, Гц | Т (4194304 1048576) | f | T (32768) |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | - 32768 16384 8192 4096 2048 1024 512 256 128 64 32 16 8 4 2 | - 30,517 мкс 61,035 мкс 122,07 мкс 244,14 мкс 488,28 мкс 976,56 мкс 1,95312 мс 3,90625 мс 7,8125 мс 15,625 мс 31,25 мс 62,5 мс 125 мс 250 мс 500 мс | - 256 128 8192 4096 2048 1024 512 256 128 64 32 16 8 4 2 | - 3,90625 мс 7,8125 мс 122,07 мкс 244,14 мкс 488,28 мкс 976,56 мкс 1,95312 мс 3,90625 мс 7,8125 мс 15,625 мс 31,25 мс 62,5 мс 125 мс 250 мс 500 мс |

Регистр В.

SET – если в этом разряде записан “0”, то каждую секунду выполняется цикл обновления информации о текущем времени и сравнение текущего времени с заданным. Единица в этом разряде запрещает обновление, позволяя записать в регистры начального значения времени, календаря, будильника.

PIE – разрешение прерываний с периодом, задаваемым PS0![]() PS3.

PS3.

ALE – разрешение прерываний от будильника.

VIE – разрешение прерываний по окончанию цикла обновления.

SQWE – разрешает выдачу сигнала на вход SQW.

PIE, AIE, VIE, SQWE могут быть сброшены сигналом ![]() .

.

DM – «1» данные в двоичном коде

- «0» данные в двоично-десятичном коде.

Значения разряда нельзя изменить без повторной записи начальных значений в ячейки времени и календаря.

24/12 – устанавливает 24 часовой («1») и 12 часовой («0») режим счета времени. В 12 часовом режиме времени после полудня отмечается единицей в старшем разряде часов (адрес О4Н).

DSE – разрешение автономного перехода на летнее время («1»).

Регистр С.

IRQF – флаг запроса прерываний. Устанавливается в единицу при выполнении условия:

PF x PIE + AF x AIE + VF x VIE=1

Одновременно с установкой IRQF=1 на контакте ![]() устанавливается низкий уровень. PF – устанавливается в «1» фронтом сигнала на выходе внутреннего делителя частоты, выбранного в соответствии с разрядами RS0

устанавливается низкий уровень. PF – устанавливается в «1» фронтом сигнала на выходе внутреннего делителя частоты, выбранного в соответствии с разрядами RS0![]() RS3.

RS3.

AF – устанавливается в «1» при совпадении текущего времени м времени «будильника».

VF – устанавливается в единицу после окончания каждого цикла обновления.

Флаги сбрасываются после чтения регистра С или сигналом ![]() .

.

Регистр D.

VRT – в этом разряде устанавливается «0» при низком уровне на входе PS. Единица устанавливается только считыванием регистра D.

Подключение микросхемы 512ВИ1 к микропроцессору серии 1821ВМ85, имеющему мультиплексированную шину адреса/данных не вызывает затруднений. На вход PS; Uп; RES подаем высокий уровень (подключим к аккумулятору через RS-цепь). Так как нет необходимости в использовании частоты кварцевого резонатора в блоке управления, то вывод №20 (CKFS) подсоединим к корпусу.

Сигнал с выхода ![]() через инвертор (PD9) подадим в микропроцессор на вход RST 6,5 (№8).

через инвертор (PD9) подадим в микропроцессор на вход RST 6,5 (№8).

Выводы AD0![]() AD7 (№№4

AD7 (№№4![]() 11) таймера непосредственно подключаются к выводам AD0

11) таймера непосредственно подключаются к выводам AD0![]() AD7 (№№12

AD7 (№№12![]() 19) микропроцессора.

19) микропроцессора.

Подача сигнала CS2 на вход «выбор микросхемы» (№13) будет рассмотрена ниже.

Похожие работы

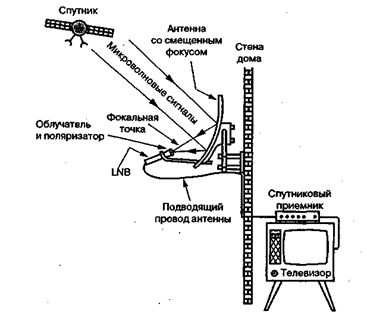

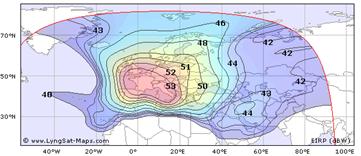

... быть получен неудовлетворительный результат, а в другом - чрезмерное усложнение конструкции может привести к неоправданному увеличению стоимости оборудования, а приемная система будет выглядеть неэстетично. Результатом расчета линии связи является вычисленное значение отношения S/N, величина которого сравнивается с соответствующими значениями по пятибалльной шкале градаций качества принимаемого ...

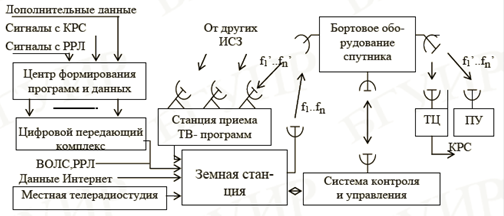

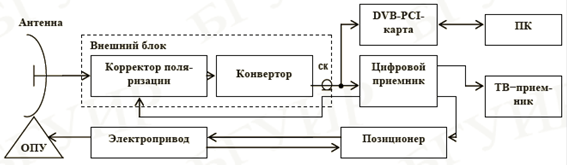

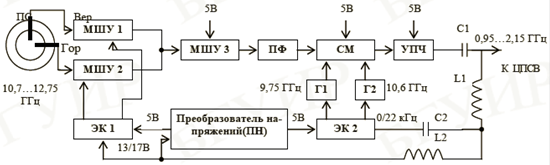

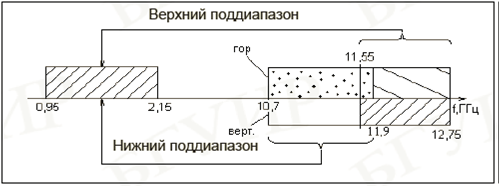

... Прием сигналов осуществляется в г. Гродно с географическими координатами ψ=53,700 с.ш., φз=23,800 в.д. с спутника HotBird 6/7A (130 з.д.) Большинство современных систем индивидуального и коллективного приёма программ спутникового вещания оснащены опорно-поворотным устройством (ОПУ) для оперативного наведения антенны на заданный ИСЗ. Наиболее простым механизмом перестройки антенны ...

... телевидения: жесткая конкуренция со стороны спутникового и кабельного ТВ; ограничения, наложенные государственными регулирующими органами на параметры передачи. Факторы, содействующие развитию цифрового телевидения: принятый срок прекращения аналогового телевизионного вещания; субсидирование абонентского приемного оборудования. До весны 2003 года компания интерактивных ...

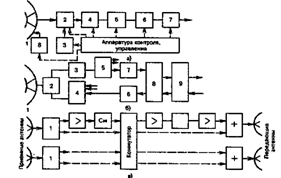

... Изм. Лист № Докум. Подп. Дата Лист 53 6. Заключение. В данном дипломном проекте проведена модернизация управляющего блока тюнера. В базовом блоке тюнера применялось сенсорное управление с ручной настройкой на соответствующий канал. Перестройка производилась с помощью подстроечных резисторов. Все это приводило к ...

0 комментариев