Навигация

Регистры управления сегментированной памятью

4.3. Регистры управления сегментированной памятью

Регистр таблицы глобальных дескрипторов (GDTR). Содержит 32-разрядный линейный адрес и 16-разрядную границу таблицы глобальных дескрипторов.

Регистр таблицы локальных дескрипторов (LDTR). Содержит 16-разрядный селектор для таблицы локальных дескрипторов. Так как эта таблица является специфичным для задачи сегментом, то она определяется значением селектора, хранимым в регистрах системного сегмента. Регистр дескриптора сегмента, связанный с этой таблицей, програмно недоступен.

Регистр таблицы дескрипторов прерываний (IDTR). Указывает на таблицу точек входа в программы обработки прерываний. Регистр содержит 32-разрядный линейный базовый адрес и 16-разрядную границу таблицы дескрипторов прерываний (IDT).

Регистр задачи (TR). Указывает на информацию, необходимую процессору для определения текущей задачи. Регистр TR содержит 16-разрядный селектор дескриптора сегмента состояния задачи. Поскольку этот сегмент специфичен для задачи, то он определяется значениями селекторов, хранящихся в регистрах системного сегмента. Заметим, что с каждым регистром системных сегментов связан программно недоступный регистр дескриптора сегмента.

4.5. Указатель команд

Расширенный указатель команд (EIP) является 32-разрядным регистром. Он содержит относительный адрес следующей команды, подлежащей выполнению. Относительный адрес отсчитывается от начала сегмента текущей программы. Указатель команд непосредственно не доступен программисту, но он управляется явно командами управления потоком, прерываниями и исключениями.

Младшие 16 бит регистра EIP называются IP и могут быть использованы процессором независимо. Это свойство полезно при исполнении команд МП 8086 и 80286, которые имеют только регистр IP.

4.6. Регистры управления

МП 80386 имеет три 32-разрядных регистра управления (CR0, CR2 и CR3, а CR1 зарезервирован фирмой Intel), в которых хранятся состояния машины или глобальные состояния. Глобальное состояние - это такое состояние, к которому может получить доступ любой из логических блоков системы или которое управляет этими блоками. Вместе с регистрами системных адресов эти регистры хранят информацию о состоянии машины, которая влияет на все задачи в системе. Для доступа к регистрам управления определены команды их загрузки и сохранности содержимого.

Системным программистам регистры управления доступны только через варианты команды MOV, которые позволяют их загружать или сохранять в регистрах общего назначения.

4.7. Регистры отладки

Шесть доступных программисту регистров отладки (DR0-DR3, DR6 и DR7) расширяют возможности отладки в МП 80386, они устанавливают точки останова по данным и позволяют устанавливать точки останова по командам без модификации сегментов программ. Регистры DR0-DR3 предназначены для четырех линейных точек останова. Регистры DR4 и DR5 зарезервированы фирмой Intel для будущих разработок. Регистр DR6 показывает текущее состояние точек останова, а регистр DR7 используется для установки точек останова.

4.8. Буфер ассоциативной трансляции

Буфер ассоциативной трансляции (TLB) - это кэш-память, используемая для трансляции линейных адресов в физические.

Механизм проверки TLB является уникальным для МП 80386 и может быть не реализован в том же виде в будущих процессорах. Программы, которые используют этот механизм в его нынешнем виде, могут оказаться несовместимыми с будущими процессорами.

5. Система команд

5.1. Формат команд

Команды МП 80386 состоят из отдельных элементов и могут иметь различные форматы. Из всех описанных ниже элементов только один (код операции, Коп) обязательно присутствует в любой команде. Остальные элементы могут отсутствовать, что определяется характером операции, а также местоположением и типом операндов.

Команды состоят из следующих элементов: необязательных префиксов; одного или двух байтов кодов операции; возможно - описателя адреса, который включает байт Mod R/M и байт масштаба, индекса и базы; смещения - если требуется; поля непосредственных данных - если требуется.

Префиксы - один или несколько байтов, предшествующих команде и модифицирующих операцию этой команды. Имеется 4 типа префиксов.

1. Повторение - используется с командами обработки строк; заставляет команду воздействовать на каждый элемент строки.

2. Размер операнда - переключает разрядность операндов, устанавливая их 32-разрядными или 16-разрядными.

3. Размер адреса - переключает разрядность адреса, определяя образование 32-разрядных или 16-разрядных адресов.

4. Замена сегмента - в явной форме указывает, какой сегментный регистр должна использовать команда. Префикс отменяет действующий по умолчанию выбор сегментного регистра, обычно осуществляемый МП 80386 при выполнении этой команды.

Код операции (Коп) - описывает операцию, выполняемую командой. Некоторым командам присущи несколько кодов операций, каждый из которых описывает определенный вариант операции.

Описатель регистра - в команде могут быть описаны один или два регистра в качестве операндов. Описатель регистра может присутствовать как в байте кода операции, так и в байте описателя режима адресации.

Описатель режима адресации. Этот элемент, если он присутствует, описывает, является ли операнд содержимым регистра или ячейки памяти. Если операнд находится в памяти, описатель режима указывает, надо ли использовать смещение, индексный регистр, регистр базы и масштабирование.

Байты MOD R/M и SIB. Большинство команд, ссылающихся на операнд, находящийся в памяти, содержат после байта основного кода операции еще байт формы адресации. Этот байт описывает используемую форму адреса. Определенные значения кода поля MOD R/M указывают на наличие второго адресного байта SIB.

Байты MOD R/M и SIB содержат следующую информацию:

- тип индексации или номер регистра, используемого в команде;

- используемый регистр или дополнительную информацию о выборе команды;

- информацию о базе, индексе и масштабе;

Смещение. Если описатель режима адресации указывает, что при вычислении адреса операнда будет использовано смещение, в состав кода команды включается поле смещения. Смещение представляет собой 8-, 16- или 32-разрядное целое число со знаком. 8-разрядная форма используется в тех случаях, когда значение смещения невелико.

Непосредственный операнд (данное). Если этот элемент присутствует, он представляет значение операнда команды. Непосредственные операнды могут быть 8-, 16- или 32-разрядными. В случаях когда 8-разрядный непосредственный операнд используется в команде вместе с 16- или 32-разрядным операндом, процессор автоматически увеличивает размер 8-разрядного операнда путем расширения его знакового разряда.

Похожие работы

... высокой производительности. Реализация потенциала архитектуры требует новейшей микроэлектронной технологии, точного разделения функций и внимания к внешним операциям кристалла, в особенности к взаимодействию процессора с памятью. Включение этих свойств обеспечивает 80386 самую высокую произвидительность по сравнению с любым другим существующим микропроцессором. Микропроцессор 80386 реализован ...

... шине данных процессора и посылает слово данных в процессор. Наоборот, выходной порт представляет собой приемник данных ( например, регистр), который избирательным образом подключается к шине данных процессора. Будучи выбран, выходной порт принимает слово данных из микропроцессора. Процессор должен иметь возможность координировать скорость своей работы со скоростью работы ...

... преодолеть присущие архитектуре х86 ограничения (различная длина инструкций). В случае использования инструкций различной длины, чипы 4-го поколения могут одновременно обрабатывать 1 команду, процессоры 5-го поколения (Pentium) - 2 команды. И только микропроцессор AMD5k86 способен обрабатывать до 4 инструкций за такт. Использование раздельного КЭШа инструкций и данных (объем КЭШа инструкций ...

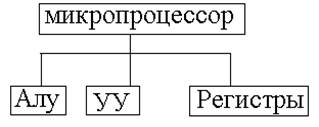

... Особенность однокристального микропроцессора – наличие внутренней шины, по которой происходит обмен информацией между устройствами микропроцессора. По функциональным возможностям микропроцессор соответствует процессору ЭВМ, выполненному на 20-40 ИС малой и средней степени интеграции, но обладает большим быстродействием, существенно меньшими размерами, массой, потребляемой мощностью и стоимостью. ...

0 комментариев