Навигация

Многопроцессорная вычислительная система

МНОГОПРОЦЕССОРНАЯ ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

1 Назначение МВС

Проектируемая МВС предназначена для решения научно-технических задач и

исследовательских задач, отличающихся большой вычислительной мощностью, а также

возможно использование проетируемой МВС в системах реального времени.

2 Состав МВС

Проектируемая МВС состоит из следующих функциональных частей:

процессорные модули

централизованный контроллер приоритетных прерываний

банк глобальной памяти

внешие устройства

централизованный арбитр доступа к общему ресурсу

блок выбора ПЭ-мастера

Процессорные модули состоят из следующих функциональных узлов:

процессорный элемент

локальная память

блок контроля

коммутатор

внутренний автомат арбитра доступа к общему ресурсу

3 Технические требования

3.1 Общие технические требования

3.1.1 Устойчивость к внешним воздействующим факторам

Основные технические параметры устойчивости приведены в табл. 1.

Механические факторы:

Проектируемая МВС должна сохранять внешний вид и работоспособность после

многократного воздействия ударных нагрузок с пиковым ускорением не более 5g при

длительности воздействия ударного ускорения 10-15 мс, а также выдерживать

вибрационную нагрузку с амплитудой виброперемещения 0,1 мм в диапазоне частот 25

Гц.

Защита от попадания твердых тел, проникновения воды и прикосновения токоведущих

частей по ГОСТ 14.254-80 степень IР33.

Таблица 1 - Основные технические параметры устойчивостиПараметры и единицы

измеренияНорма

1Допустимый диапазон температур, оС+5 … 40

2Максимальная допустимая относительная влажность при температуре 25оС, %80

3Диапазон допустимых атмосферных давлений, кПа80 … 105

Защита от внутренних и внешних электрических и радиационных помех

Радиационная стойкость по ГОСТ 15484-74.

Стойкость к индустриальным помехам по ГОСТ 25211-79.

Питание

Питание от сети переменного тока напряжением 220В.

Комплектность Многопроцессорная вычислительная система, шт.1

Руководство по эксплуатации, эск.1

Тара упаковочная, шт.1

Частные технические требования

МВС строится на основе двоичной системы счисления. Процессорные элементы

реализованы с выполнением совмещения выборки и выполнения команд. Объем

локальной памяти в каждом процессорном модуле (ПМ) составляет 2 МБ, банк

глобальной памяти - объемом 12М.

Количество обслуживаемых внешних устройств – 24 шт.

Проектируемая МВС ориентирована на применение многозадачной операционной

системы(ОС) на архитектуре систем с глобальной памятью, работа ведется в режиме

Ведущий-Ведомый (Master-Slave).

4 Требования надежности

коеффициент готовности – не менее 0,998

среднее время безотказной работы – 5000 час.

5 Конструктивные требования

Конструкционная система по МС МЭК 297-1.

МВС строится на стандартных микросхемах.

Этапы проектированияные

1.Техническое задание

2.Техническое предложение

3.Эскизный проект

4.Технический проект

5.Подготовка рабочей документации

7 Перечень документации

7.1 Текстовая документация

техническое задание

пояснительная записка с приложениями

7.2 Графическая документация

Многопроцессорная вычислительная система. Схема электрическая функциональная

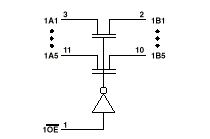

Централизованный арбитр доступа к общему ресурсу. Схема электрическая

принципиальная

Ведомость технического проекта

7.4 Рабочая документация

спецификация многопроцессорной вычислительной системы

ведомость спецификаций

ведомость покупных изделий

ВВЕДЕНИЕ

В данном курсовом проекте разрабатывается многопроцессорная вычислительная

система (МВС) ориентированная на физическую архитектуру систем с Общей Шиной, в

частности на системы с глобальной памятью.

Применение разрабатываемой МВС возможно как для проведения научных исследований,

решения научно-технических задач, отличающихся большой трудоемкостью и

сложностью вычислений так и для задействования данной МВС в контуре управления

объектами систем реального времени (СРВ).

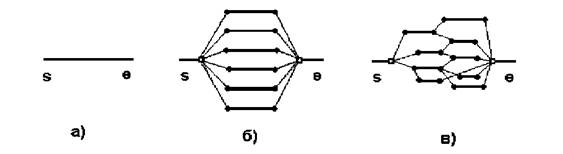

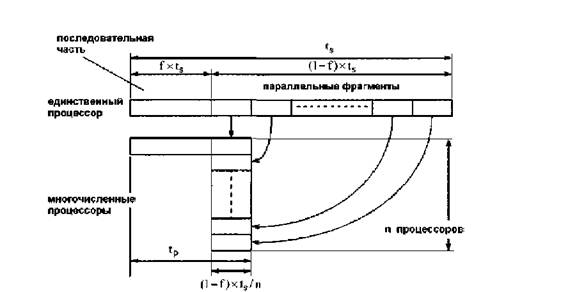

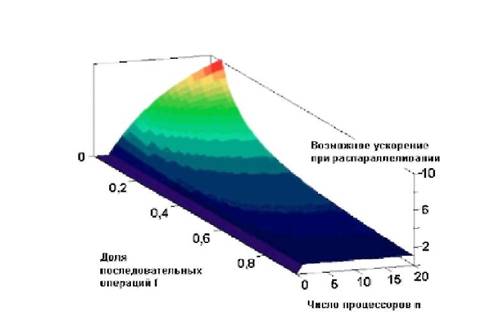

Увеличение скорости обработки информации достигается за счет одновременного

использования нескольких процессорных модулей, то есть распараллеливания

процесса вычислений. При этом подразумевается обмен информацией между

процессорами через глобальную память с использованием системы прерываний.

1 Разработка архитектуры, функционирование МВС

Разработка архитектуры МВС

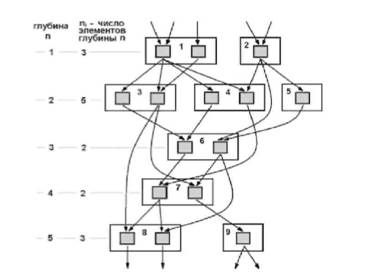

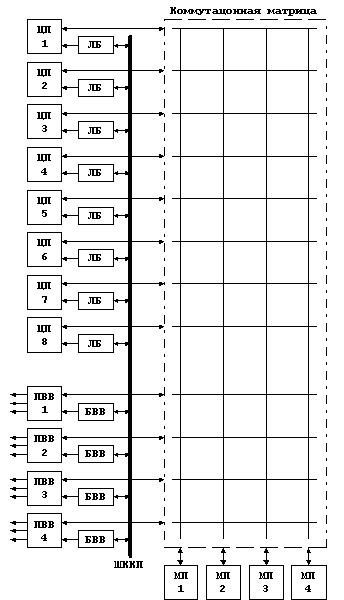

Проектируемая МВС строится из отдельных процессорных модулей, обмен информации

между процессорами основан на применении системы прерываний; доступ отдельных

процессоров к общему ресурсу (системной магистрали) управляется централизованным

арбитром доступа с абсолютным географическим приоритетом процессорных модулей,

что предполагает сосредоточение всех необходимых цепей управления в данном

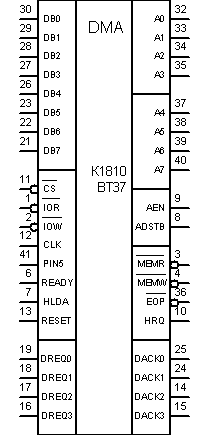

устройстве; обработка ввода/вывода информацией через внешние устройства

осуществляется через централизованный контроллер прерываний, путем обработки

выставляемого внешними устройствами вектора прерывания, который представляет

собой адрес подпрограммы обработки данного события.

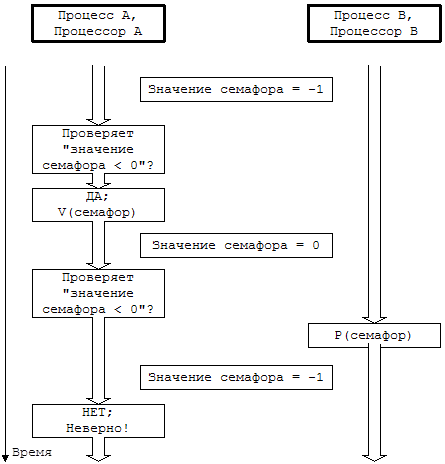

На функциональном уровне основные характеристики проектируемой МВС, а именно:

G – характеристика, описывающая коммутацию компонент системы, (grod)

M – характеристика, описывающая организацию памяти системы, (memory)

показаны с использованием графического языка описания вычислительных систем

MSBI(Master Slave Bus Interface), результат представлен на Рис. 1.1.

В состав процессорного модуля входят локальная память размером 1М, процессорный

элемент, блок контроля, коммутатор, внутренний автомат арбитра доступа к ОР.

МВС содержит 8 процессорных модулей и 1 системную магистраль, к которой

подключен банк глобальной памяти, емкостью 12 М.

Каждый процессорный элемент модет обращаться как к собственному банку локальной

памяти, так и к общему банку глобальной памяти. Очевидно, что глобальная память

является в описываемой МВС общим ресурсом, то есть при одновременной попытке

обращения нескольких процессорных элементов к ГП может возникнуть конфликт

доступа к общему ресурсу (так называемые критические участки). Для решения

данной проблемы на аппаратном уровне в проектируемой МВС предусмотрено

применение централизованого арбитра доступа к СМ, с абсолютным географическим

приоритетом процессорных модулей, что однозначно решает проблему надежного

функционирования МВС в критических участках. Подробное описание механизма

взаимодействия процессорного элемента и арбитра доступа к ОР приведено в Разделе

Похожие работы

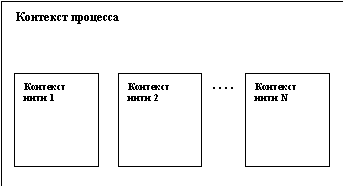

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

... процесса, а либо вообще не сказываются на работе МПВК, либо вызывают постепенную деградацию вычислительной мощности. Меры по обеспечению отказоустойчивости свои для каждого компонента МПВК. Отказы оперативной памяти были рассмотрены выше. Отказы в коммутационной матрице также как и отказы оперативной памяти целесообразно маскировать применением кодов, корректирующих ошибки. Наиболее сложны для ...

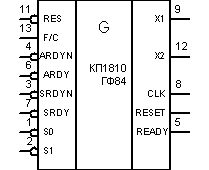

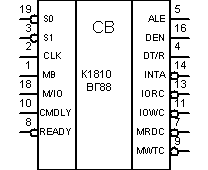

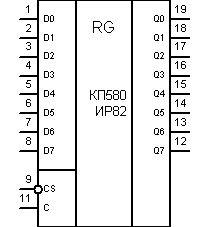

... характер сигналов интерфейса и их временную диаграмму, а также описание электрофизических параметров сигналов. На рис. 2.2 представлена общая схема сопряжения МП с устройствами ввода-вывода УВВ и ОЗУ в микропроцессорной системе. Рис 2.2. Схема интерфейсных связей микропроцессора Связь МП с УВВ требует пять групп связей, обеспечиваемых через выводы корпуса МП. По группе шин 1 передается ...

... канал ввода-вывода и внешнее запоминающее устройство, что требует много времени. 1. Разработка структурной схемы Целью данного курсового проекта является разработка структуры многопроцессорного вычислительного комплекса с многовходовым ОЗУ. Структурная схема такого МПВК приведена в приложении на схеме 1. Рассмотрим блоки, представленные на данной схеме. 1. Блок генерации сигналов. ...

0 комментариев