Навигация

Архітектурний опис на структурному рівні

2.2.2.1 Архітектурний опис на структурному рівні

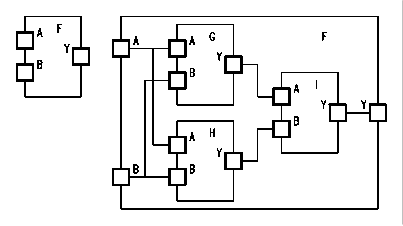

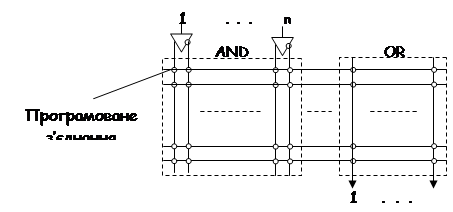

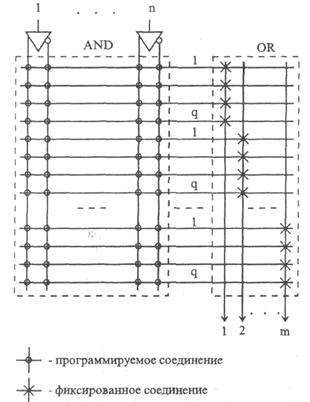

Цифрова електронна система може бути описана як модуль з входами і/або виходами. Електричні значення на виходах є деякою функцією від значень на входах. На рис.2.2(а) показано приклад цього типу цифрової системи. Модуль F має два входи, A і B, і вихід Y. Використовуючи VHDL-термінологію ми називаємо модуль F об’єктом проектування (компонентою), а входи і виходи - портами.

Одним з шляхів опису функції модуля є опис його побудови із субмодулів. Кожний із субмодулів є складовою компоненти, а порти складових об’єднуються використовуючи сигнали. На рис.2.2(b) показано, як компонента F може бути побудована із складових - об’єктів G, H та I. Цей тип опису називається структурним описом. Зауважимо, що кожний із об'єктів G, H та I повинен також мати структурний опис.

|

|

| (a) (b) |

| Рис.2.2. Архітектурний опис на структурному рівні |

Опис виконуваної модулем функції, без розкриття його внутрішньої структури названо функціональним або поведінковим описом.

Для ілюстрації цього приймемо, що функція компоненти F на рис.2.2(а) є функцією “виключаюче АБО”.

Тоді поведінковий опис F може бути булевою функцією:

![]() .

.

Більш складні поведінки не можуть бути описані тільки функцією від входів. В системах з оберненими зв’язками виходи є також функцією від часу. VHDL розв’язує цю проблему, допускаючи опис роботи в формі виконуваної програми.

2.2.2.3 Архітектурний опис на рівні часової діаграмиКоли структура і виконувані функції модуля визначені, стає можливим моделювання його часової діаграми роботи. Це робиться шляхом моделювання його роботи по ходу часу дискретними кроками. В деякий час моделювання вхід модуля може стимулюватись зміною значення на вхідному порті. Модуль реагує зміною коду його поведійного опису і планує нові значення сигналів на вихідних портах в дещо пізніший час моделювання. Це називається плануванням реакції на сигнал. Якщо нове значення відрізняється від попереднього, то і інші модулі, вхідні порти яких під’єднані до виходу цього, можуть активуватися.

Моделювання починається з фази ініціалізації, а в подальшому відбувається повторення двохстадійного циклу моделювання. На фазі ініціалізації всі сигнали отримують початкові значення, час моделювання встановлюється в нуль і виконується програма поведінки кожного модуля.

2.3 VHDL як мова програмування 2.3.1. Лексеми 2.3.1.1 КоментаріКоментар в VHDL - це рядок, що починається з двох коротких тире (‘--’).

2.3.1.2 ІдентифікаториІдентифікатори в VHDL - це резервовані слова та визначені програмістом імена. Їх опис повинен задовільняти правилу:

<ідентифікатор>::=<літера>{<літера>|<цифра>|<знак_підкреслення>}

Мова VHDL нечутлива до регістру літер.

2.3.1.3 Числові константиЧисла можуть виражатись в десятковій формі або в системі числення від 2 до 16. Якщо число у свому записі містить крапку, воно представляє число з рухомою крапкою (float), інакше воно представляє ціле (integer).

Числа в десятковій формі запису:

<число>::=<ціле>[.<ціле>][<експонента>]

<ціле>::=<число> {<знак_підкреслення>|<число>}

<експонента>::=Е[<+>|<->]

Числа,що записані в системі числення з певною основою:

<число_в_системі_числення>::=<десяткове_ціле_як_основа_системи_числення>#<число>

Основа системи числення та експонента записуються десятковим числом. Літери від A до F означають відповідно числа від 10 до 15.

2.3.1.4 СимволиСимвольні літерали представляються як символ ASCII в одиночних лапках.

2.3.1.5 РядкиРядкові літерали - це набір символів ASCII в подвійних лапках. Щоби представити знак подвійних лапок в рядковому літералі, потрібно повторити його двічі. Рядок також може розглядатись як масив символів.

2.3.1.6 Бітові рядкиОписують послідовність бітів:

<бітовий_рядок>::=<основа>“<значення>”

<основа>::=В|О|Х відповідно для двійкових, вісімкових та шістнадцяткових значень.

<значення>::=<число>

2.3.2 Типи даних та об’єктиVHDL надає велику кількість головних типів (скалярних типів) та засоби для утворення складених типів. Скалярні типи включають числові, фізичні величини та перелічувальні типи. Є також велика кількість наперед визначених стандартних типів.

Складені типи включають масиви та записи. VHDL також має тип покажчика (access) та файловий тип (files).

Визначення типу проводиться директивою TYPE:

TYPE<ідентифікатор> IS <опис_типу>;

2.3.2.1 Цілочисельні типиЦе типи, для яких задається діапазон значень:

TYPE <ідентифікатор> IS RANGE <значення_від> TO|DOWNTO <значення_до>;

Максимальний діапазон від -2147483647 до +2147483647 визначений як тип integer.

2.3.2.2 Типи фізичних величинЦе числові типи, які описують якусь фізичну величину, таку як маса, довжина, час, напруга тощо. Опис такого типу дуже схожий на опис цілочисельного типу, в якому задаються базові одиниці, що утворюються множенням коефіцієнту на базові одиниці.

TYPE <ідентифікатор> IS RANGE <значення_від> TO|DOWNTO <значення_до>

UNITS

<базова_одиниця_виміру>;

{<похідна_одиниця>;}

END UNITS;

Важливим наперед визначеним типом в VHDL є час. Він використовується при описі затримок часу, що є необхідним для процесу симуляцій.

2.3.2.3 Тип з рухомою крапкоюЦей тип є дискретним наближенням до множини чисел з рухомою крапкою у вказаному інтервалі. Точність наближення не вказується в стандарті VHDL, але вона має бути хоча б 1E-6. VHDL має наперед визначений тип real в діапазоні від -1Е-38 до +1Е38.

Опис типу з рухомою крапкою такий самий як і опис цілочисельного типу.

2.3.2.4 Перелічувальні типиПерелічувальний тип - це впорядкований набір ідентифікаторів або символів. В межах цього набору ідентифікатори та символи повинні відрізнятись:

TYPE <ідентифікатор_перелічувального_типу> IS ({<ідентифікатор>|<символ>,});

VHDL має кілька наперед визначених перелічувальних типів:

TYPE severity_level IS (note, warning, error, failure);

TYPE boolean IS (false, true);

TYPE bit is (’0’,’1’);

TYPE character IS (... koi-7...);

Символи ‘0’ та ‘1’ є одночасно членами типів bit та character. VHDL сам визначає тип ‘0’ та ‘1’ в залежності від контексту, де вони використовуються.

2.3.2.5 МасивиМасив у мові VHDL - це набір індексованих елементів одного типу. Масиви можуть бути одновимірні (з одним індексом) та багатовимірні (з багатьма індексами). Масиви також можуть бути обмеженими та необмеженими.

Декларування типу масив:

TYPE <ідентифікатор_масиву> IS ARRAY <межі_для_індексів> | RANGE <> OF <тип>;

Індекси для посилання на елементи масиву вказуються в круглих дужках.

2.3.2.6 ЗаписиЗапис є набором іменованих елементів однакового або різних типів:

TYPE <ідентифікатор_запису> IS RECORD <елемент>{,<елемент>} END RECORD;

При посиланні на поля ім’я запису та ім‘я поля відокремлюються крапкою.

2.3.2.7 ПідтипиПідтипи використовуються для декларування ідентифікатора як підмножини деякого базового типу:

SUBTYPE <новий_тип> IS <базовий_тип><межі>;

VHDL має два наперед визначених підтипи:

SUBTYPE natural IS integer RANGE 0 TO <max>;

SUBTYPE positive IS integer RANGE 1 TO <max>;

2.3.2.8 Об’єктиОб’єкт - це спеціальний тип в VHDL. Є три класи об’єктів: константи, змінні та сигнали.

Константа - це об’єкт, що ініціалізується вказаним значенням в момент створення. Далі це значення не змінюється.

CONSTANT <ідентифікатор>:<тип>[:=<значення>];

Константи без присвоєного їм значення використовуються при декларуванні пакетів. Це значення буде присвоюватись у відповідному тілі пакета.

Змінна - це об’єкт, значення якого може змінюватись після його створення.

VARIABLE <ідентифікатор>:<тип>[:=<значення>];

Якщо присвоюване значення відсутнє при декларації змінної, то змінна набуває значення за замовчуванням.

2.3.3 Вирази та операториВирази в VHDL, як і в більшості мов програмування, включають імена об’єктів, літералів, оператори, виклики функцій та операції з дужками.

VHDL має наступні оператори (в порядку зменшення приоритету):

** ABS NOT

* / MOD REM

+(sign) -(sign)

+ - &

= /= < <= > >=

AND OR NAND NOR XOR

Логічні оператори AND, OR, NAND, NOR, XOR і NOT працюють над значеннями типу bit або boolean, а також одновимірний масив з елементів вказаних типів. Для операндів-масивів операція виконується над відповідними елементами масивів.

Розмірність вхідних та вихідного масивів однакова. AND, OR, NAND використовують свій другий операнд, якщо перший операнд не визначає результату. Так AND і NAND використовує другий операнд, якщо перший дорівнює true (‘1’), а OR та NOR використовує другий операнд, якщо перший дорівнює false (‘0’).

Операції порівняння =, /=, <, <=, > та >= повинні мати два оператори однакового типу. Тип результату порівняння завжди boolean. Оператори еквівалентності (= та /=) можуть мати операнди будь-якого типу. Два складених типи вважаються однаковими, якщо однаковими є усі відповідні елементи. Решта операторів порівняння вимагають, щоб їх операнди були скалярного типу або одновимірного масиву.

Знакові оператори (+ та -), а також оператори додавання (+) та віднімання (-) опрацьовують числові операнди.

Оператор конкатенації (&) опрацьовує одновимірні масиви та дає результат - масив, що складається з елементів першого, за яким слідують елементи другого. Він може також під’єднати один новий елемент до масиву або два незалежних елементи об’єднати в масив. Найчастіше цей оператор використовується з рядками.

Оператори множення (*) та ділення (/) працюють над цілими числами, числами з рухомою крапкою та з типами фізичних величин. Операції ділення без остачі (MOD) та остача від ділення (REM) працюють лише з цілими.

Операція абсолютного значення (ABS) працює лише з числовими типами.

Піднесення до степеню (**) може мати цілочисельний або тип з рухомою крапкою першого операнду та цілочисельній тип другого операнду. Від’ємний другий операнд дозволяється лише за умови, коли перший операнд є число з рухомою крапкою.

2.3.4 КонструкціїМова VHDL містить спеціальні конструкції, які дозволяють змінювати стан об’єктів та контролювати потік виконання моделі.

2.3.4.1 Присвоєння значень зміннимЗмінна набуває нового значення за допомогою конструкції присвоєння:

<ім’я_об’єкту> | <агрегат> := <вираз>;

Об’єкт та вираз повинні бути однакового типу.

Алгоритм виконання такого присвоєння наступний: спочатку обраховуються значення елементів агрегату та значення виразу, а далі відбувається присвоєння значення виразу агрегату.

2.3.4.2. Умовна конструкція ifДозволяє виконання інструкцій в залежності від виконання умов.

IF <умова> THEN

<послідовність_конструкцій>

{ ELSE IF <умова> THEN <послідовність_конструкцій> }

[ ELSE <послідовність_конструкцій>]

END IF;

Умовою є вираз, що дає результат типу boolean.

2.3.4.3 Умовна конструкція caseДозволяє виконати послідовність конструкцій в одній з гілок.

CASE <вираз> IS

{ WHEN <вибір> { |<вибір> } | OTHERS =>

<послідовність_конструкцій>

}

END CASE;

<Вираз> та <вибір> мають бути виразами дискретного типу або одновимірними масивами символів.

Всі значення <вибір> мають буті різними. OTHERS повинна включатись як остання альтернатива. Якщо результат виразу - масив, то <вибір> має бути рядком або бітовим рядком.

2.3.4.4 Конструкція циклу loopVHDL має базову конструкцію LOOP, яка може бути у формі WHILE чи у формі FOR. Це дві, так звані, ітераційні схеми.

[<мітка>:]

[<схема_while>|<схема_for>] LOOP

[<послідовність_конструкцій>];

[NEXT [<мітка>] [WHEN <умова>];

[EXIT [<мітка>] [WHEN <умова>];

END LOOP [<мітка>];

Якщо ітераційна схема пропущена, то отримаємо нескінчний цикл.

Ітераційна схема WHILE тестує умову, що обчислюється перед кожною ітерацією.

Ітераційна схема FOR вводить змінну циклу, яка приймає послідовні значення у вказаних межах. У тілі циклу ця змінна розглядається як костанта (їй не можна присвоювати значення). Після закінчення циклу значення цієї змінної не існує.

2.3.4.5 Порожня конструкціяНе виконує ніяких дій. Використовується лише у випадках, коли необхідно явно вказати, що ніяка дія не виконується. Найчастіше застосовується в конструкції CASE у гілці, при виборі якої не віконується жодна дія.

2.3.4.6 Конструкція підтвердженняКонструкція підтвердження використовується для перевірки певних умов і для видачі певного повідомлення в разі, коли ці умови заборонені.

ASSERT <умова>

[REPORT <вираз>]

[SEVERITY <вираз>];

Якщо присутній REPORT, результат виразу повинен бути рядковим. Це буде повідомлення, якщо умова є хибною. Якщо REPORT відсутній, то повідомлення за замовчуванням буде “Assertion violation”. Якщо присутній SEVERITY, вираз повинен мати тип severity_level; якщо його нема, то значення за замовчуванням є error. Симулятор може закінчити своє виконання, якщо умова не виконалась і значення SEVERITY є більшим за якесь порогове значення, величина якого залежить від реалізації. Як правило, величина порогового значення регулюється користувачем.

2.3.5 Підпрограми та пакетиЯк і інші мови програмування, VHDL підтрімує підпрограми у формі процедур та функцій. VHDL також підтримує пакети для групування декларувань та об’єктів в окремі модулі. Пакети також забезпечують деяку абстракцію даних та приховування певних блоків інформації.

2.3.5.1 Процедури та функціїДекларування функцій та процедур відбувається за такими правилами:

PROCEDURE [<список_формальних_параметрів>]

|FUNCTION [<список_формальних_параметрів>]

RETURN <тип_значення>;

Для функцій також вказується тип результату, що буде повертатись коли функція виконається. Така форма декларування підпрограм (не вказуючи їх тіла) часто використовується в пакетах, де тіло підпрограми дається в тілі пакету, а також при визначенні взаємно рекурсивних процедур.

В списку формальних параметрів можуть бути константи, змінні та сигнали.

2.4 Структурний опис мовою VHDL 2.4.1 Декларування елементаЦифрова схема проектується, як правило, ієрархічним набором елементів. Кожен елемент має набір портів для реалізації інтерфейсу із зовнішним світом. При цьому кожен елемент в свою чергу може складатись з інших елементів.

Синтаксис декларації елемента наступний:

ENTITY <ім’я> IS

<заголовок>;

BEGIN

<тіло>;

END <ім’я>;

Заголовок елементу може використовуватись для декларування речей, які потім будуть використовуватись у тілі елемента. В заголовку також можуть записуватись спеціальні пункти, що допомогають при симуляції.

Тут можуть вказуватись константи, що описують поведінку елемента GENERIC CONSTANT, та канали вводу/виводу PORT.

GENERIC CONSTANT описуються так само, як і декларація підпрограм. Всі вони повинні мати клас констант. Дійсні значення констант передаються тоді, коли елемент буде використано. PORTS описуються так само, як і GENERIC CONSTANT, але їх клас повинен бути SIGNAL. Це є новий клас, тому покажемо його синтаксис:

SIGNAL <список_ідентифікаторів>:[<режим>] <тип> [BUS] [:=<статистичний вираз>]

Так, як клас повинен бути SIGNAL за замовчуванням, слово SIGNAL може бути пропущене.

Слово BUS (шина) показує, що порт буде під’єднано до кількох виходів.

2.4.2 Декларування архітектури елементаПісля того, як елемент було декларовано за допомогою ENTITY, потрібно описати його архітектуру в розділі ARCHITECTURE. Кожен елемент може мати кілька таких описів.

ARCHITECTURE <ідентифікатор> OF <ім’я> IS

<заголовок>;

BEGIN

<тіло>;

END <ідентифікатор>;

В тілі архітектури вказуються пункти, що описують елемент конструктивно.

2.4.2.1 Декларування сигналівСигнали використовуються для з’єднання піделементів між собою. Вони описуються за наступним синтаксисом:

SIGNAL <список_ідентифікаторів>:<тип>[REGISTER | BUS] [:=<вираз>];

Значення виразу в декларуванні сигналу використовується для надання сигналу початкового значення під час фази ініціалізації при моделюванні. Якщо вираз не вказано, то буде використовуватись значення за замовчуванням. Порти елемента слід розуміти як сигнали в межах цього елементу.

2.4.2.3 Декларування компонентівВ тілі архітектури дозволяється описувати окремі елементи та поміщати їх до бібліотек для подальшого використання. Для цього в тілі архітектури потрібно декларувати компоненту. Її можна розуміти як тимчасове в межах даної архітектури визначення віртуального елементу.

COMPONENT <ідентифікатор>

[GENERIC (. . .)];

[PORT (. . .);

END COMPONENT;

2.4.2.4. Використання компонентів<мітка>: <ім’я_компоненту>

[<дійсний_generic_map>]

[<дійсний_port_map>];

2.5 Функціональний опис мовою VHDLФункціональний опис передбачає запис засобами мови програмування VHDL законів зміни сигналів.

Присвоєння значень сигналам диспетчеризує одну або кілька транзакцій на сигнал (або порт) в наступний спосіб:

<сигнал> | <агрегат> <= [TRANSPORT]

<значення> [AFTER | NULL]<час>{, . . . };

Цільовий сигнал може бути представлений агрегатом сигналів. Якщо час пропущений, то за замовчуванням береться затримка 0fs. Це означає, що транзакція буде диспетчеризована в той самий час, коли відбулось присвоєння, але в наступний цикл симуляції.

Кожен сигнал асоціюється з хвильовою проекцією виходу (далі проекція). Це є фактично перелік транзакцій майбутніх значень сигналу. Кожне присвоєння сигналу додає транзакцію до проекції.

СПИСОК ВИКОРИСТАНИХ ДЖЕРЕЛ

1. Бобровский С. Delphi 7. Учебный курс. – СПб.:Питер,2004. – 735 с.

2. Энго Ф. Как программировать на Delphi 4.0. Пер. с англ – К.: ДиалСофт, 1999. – 430 с.

3. Архангельський А.Я.. Программирование в Delphi 6. – М.: Бином, 2002. – 823 с.

4. Культин Н.Б.. Delphi 6.0. Программирование на Object Pascal. – СПб.: Питер ,2004. –526 с.

5. Лишнер Р. Секреты Delphi 2. Пер. с англ. – К.: НИПФ ДиаСофтЛтд, 1996. – 800 с.

6. Проектування цифрових систем з використанням мови VHDL: Навч. посібник/ В.В. Семенець, І.В. Хаханова, В.І. Хаханов. – Харків: ХНУРЕ, 2003. – 492 с.

7. Сергиенко А.М. VHDL для проектирования вычислительных устройств. – К.: ТИД ДС , 2003. – 208 с.

Похожие работы

... ї конференції молодих науковців CSE-2007. – Львів: Видавництво Національного університету "Львівська політехніка", 2007. – С.74–75. АНОТАЦІЇ Акимишин О.І. Методи та засоби зменшення обсягів даних тріангуляційного опису об’єктів комп’ютерної томографії. – Рукопис. Дисертація на здобуття наукового ступеня кандидата технічних наук за спеціальністю 05.13.05 – комп’ютерні системи та ...

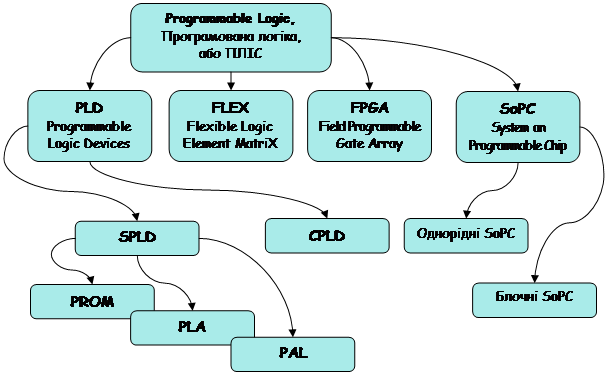

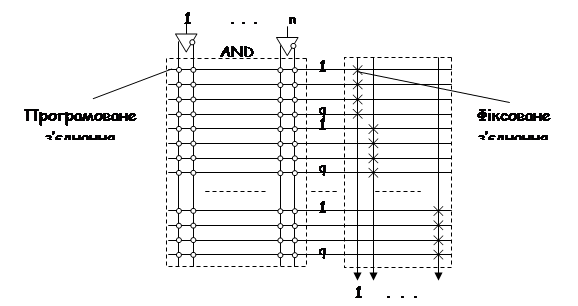

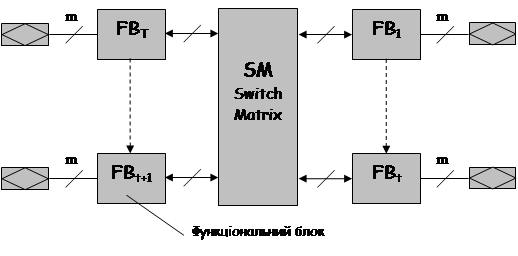

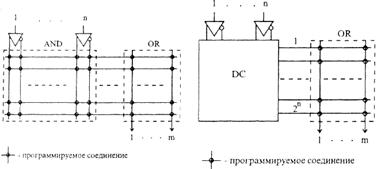

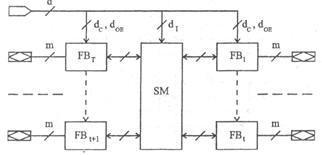

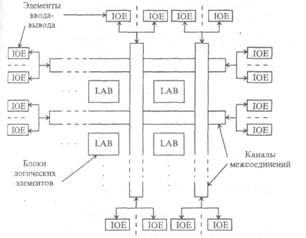

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

... ім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів. 2. Призначення та структура системи автоматизованого проектування MAX+PLUS II Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхі ...

... стиль і деталі виконання проектних робіт. Наступним етапом до стандартного проекту вносять зміни, що відповідають індивідуальним вихідним даним. Після синтезу і імплементування модифікованого проекту розроблюють принципову схему прототипної плати (емулятора) і оформлюють пояснювальну записку. Як аналог проекту емулятора використовують прототипні плати фірми Xess (www.xess.com). Знайдений аналог ...

0 комментариев