Навигация

Розробка цифрових засобів ПЛІС в інтегрованому середовищі проектування MAX+PLUS II

Міністерство освіти і науки України

Національний технічний університет України

“Київський політехнічний інститут”

Приладобудівний факультет

Кафедра приладів та систем орієнтації і навігації

Атестаційна магістерська робота

на тему:

Розробка цифрових засобів ПЛІС в інтегрованому

середовищі проектування MAX+PLUS II

Київ 2009

Зміст

Анотація

Перелік умовних позначень, символів, скорочень і термінів

Вступ

1. Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура

2. Призначення та структура системи автоматизованого проектування MAX+PLUS II

3. Додатки системи автоматизованого проектування MAX+PLUS II

4. Процедура розробки нового проекту в системі автоматизованого проектування MAX+PLUS II

5. Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II

6. Загальні відомості про мову описання апаратури AHDL

7. Реалізація в інтегрованому середовищі MAX+PLUS II базових пристроїв мікроелектроніки

7.1 Теоретичні відомості про тригери

7.1.1 RS-тригер

7.1.2 Синхронний RS-тригер

7.1.3 D-тригер

7.1.4 JK-тригер

7.1.5 Програми реалізації тригерів в інтегрованому середовищі MAX+PLUS II

7.1.6 Результати програмної реалізації тригерів

7.2 Теоретичні відомості про регістри

7.2.1 Послідовні регістри зсуву

7.2.2 Паралельні регістри зсуву

7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II

7.2.4 Результати програмної реалізації регістрів

7.3 Теоретичні відомості про лічильники

7.3.1 Лічильник з крізним переносом

7.3.2 Асинхронний лічильник з модулем 10

7.3.3 Лічильник віднімання

7.3.4 Програми реалізації лічильників в інтегрованому середовищі MAX+PLUS II

7.3.5 Результати програмної реалізації лічильників

7.4 Теоретичні відомості про мультиплексори, демультиплексори, шифратори, дешифратори

7.4.1 Мультиплексор

7.4.2 Демультиплексор

7.4.3 Шифратор

7.4.4 Дешифратор

7.4.5 Програми реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів в інтегрованому середовищі MAX+PLUS II

7.4.6 Результати програмної реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів

7.5 Теоретичні відомості про суматори, віднімачі

7.5.1 Суматори

7.5.2 Віднімачі

7.5.3 Програми реалізації суматорів, віднімачів в інтегрованому середовищі MAX+PLUS II

7.5.4 Результати програмної реалізації суматорів, віднімачів

8. Проект реалізації COM-порту в САПР MAX+PLUS II

8.1 Теоретичні відомості про послідовні порти і протокол RS-232

8.2 Структура COM-порту при його реалізації в САПР MAX+PLUS II

8.3 Програми структурних компонентів COM-порту мовою AHDL в САПР MAX+PLUS II

8.4 Результати програмної реалізації COM-порту в САПР MAX+PLUS II

Висновки

Використана література

Анотація

Дипломна робота викладена на 108 аркушах, містить 61 ілюстрацію, 17 таблиць і 20 посилань на джерела інформації, що мають відношення до даного тематичного напрямку.

Метою дипломної роботи є створення інформаційно-програмної бази для роботи з інтегрованим середовищем MAX+PLUS II.

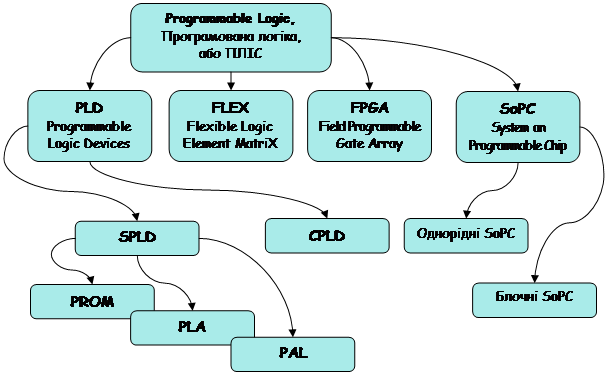

Роботою передбачено теоретичний опис основних приладів мікроелектроніки разом з їх програмною реалізації за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II. В роботі проведено генезис програмувальних логічних інтегральних схем, їх класифікація, архітектура, детально розписана процедура створення нового проекту і процес його компіляції.

З метою більш детального пояснення взаємозв’язку різних додатків зазначеного середовища в дипломній роботі реалізовано проект послідовного COM-порту, що складається з декількох базових мікроелектронних пристроїв, принципи дії яких було описано у відповідних розділах.

Результатом дипломної роботи є описання основ роботи з інтегрованим середовищем MAX+PLUS II, підкріплене прикладами розробки і моделювання конкретних пристроїв. Вони можуть використовуватися як в дидактичних, так і в науково-дослідницьких цілях.

В подальшому можливий розвиток і доповнення роботи за наступними напрямками: створення програмно-інформаційної бази найбільш поширених мікроелектронних приладів на основі ПЛІС фірми Altera; визначення можливості інтеграції інтегрованого середовища MAX+PLUS II з іншими пакетами та системами автоматичного проектування; створення на базі ПЛІС мікропроцесорних пристроїв з відносно малими габаритами і споживчою потужністю.

Ключові слова (словосполучення): архітектура пристрою, електроніка, гнучка логіка, мікроелектронний пристрій, моделювання поведінки, послідовний порт, програмувальна логічна інтегральна схема, програмування, компіляція, система автоматичного проектування.

Перелік умовних позначень, символів, скорочень і термінів

АДП – апаратура передачі даних;

БМК – базовий матричний кристал;

ПЛІС – програмувальна логічна інтегральна схема;

ПЛМ – програмувальна логічна інтегральна матриця;

ПЛП – програмувальний логічний пристрій;

ППЗП – програмувальній постійній запам’ятовуючій пристрій;

ООД – одно кінцевий об’єкт передачі даних

САПР – система автоматизованого проектування;

СБФ – система булєвих функцій;

AMD – Advanced Micro Devices;

CLK – CLocK;

CPLD – Complex Programmable Logic Device;

DCE – Data Communication Equipment;

DTE – Data Transfer Equipment;

ENA – ENAble;

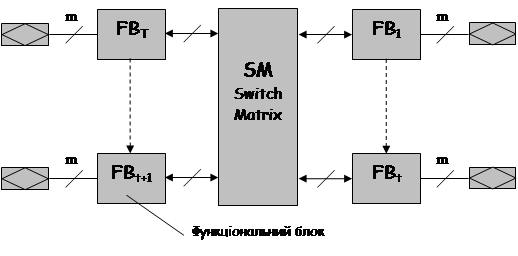

FLEX – Flexible Logic Element Matrix;

FPGA – Field Programmable Gate Array;

GA – Gate Array;

GAL – Generic Array Logic;

IOB – Input/Output Element;

JTAG – Joint Test Action Group;

LAB – Logic Array Block;

LE – Logic Element;

MAX – Multiple Array Matrix;

PLA – Programmable Logic Array;

PLD – Programmable Logic Devices;

PLS – Programmable Logic Sequencers;

PROM – Programmable Read Only Memory;

SPLD – Standart Programmable Logic Devices.

Вступ

Широке впровадження електроніки й автоматики в усі сфери людської діяльності, що спостерігається в даний час, пред'являє все більш жорсткі вимоги до виробів електронної техніки. Це пов'язано, з одного боку, зі зростанням важливості і складності розв'язуваних задач, а, з іншого боку, необхідністю поліпшення таких характеристик, як швидкодія, надійність, споживана потужність, габарити, вартість та інше. Одним з шляхів вирішення даної проблеми є широке використання програмувальних логічних інтегральних схем (ПЛІС - Programmable Logic Devices - PLDs).

ПЛІС являють собою нову елементну базу, що володіє гнучкістю замовлених ВІС і доступністю традиційної "твердої" логіки.

Головною відмітною властивістю ПЛІС, на відміну від “жорсткої” логіки, є можливість настроювання на виконання заданих функцій самим користувачем. Сучасні ПЛІС характеризуються низькою вартістю, високою швидкодією, значними функціональними можливостями, багаторазовістю перепрограмування, низкою споживаною потужністю й інше.

При цьому час розробки на основі ПЛІС навіть досить складних проектів може складати усього кілька годин. Власно кажучи, розробка пристроїв на основі ПЛІС являє собою нову технологію проектування електронних схем, включаючи їх виготовлення і супроводження. Доказом перспективності нової елементної бази служить щорічна поява нових поколінь ПЛІС, а також постійно зростаючий обсяг випуску вже розроблених ПЛІС.

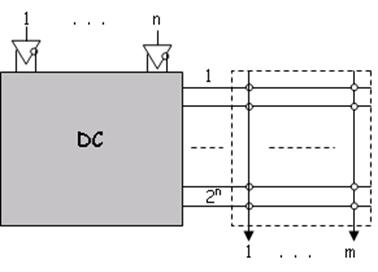

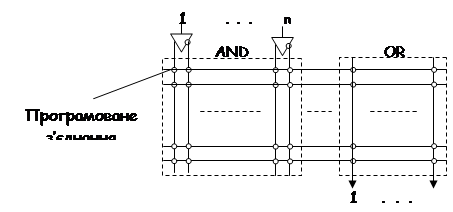

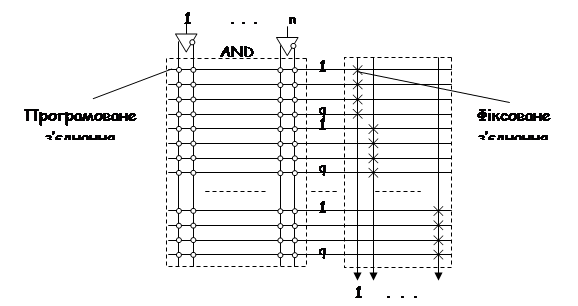

Істотною перешкодою широкого практичного використання ПЛІС є відсутність ефективних методів синтезу. Справа в тому, що в основу архітектури сучасних ПЛІС покладена структура програмувальних логічних матриць (ПЛМ — Programmable Array Logics — PALs), що являє собою пари матриць: І й АБО, у якій програмується матриця І, а матриця АБО має фіксоване положення. Методи й алгоритми синтезу на такій структурі одержали назву двухуровнего синтезу і бурхливо розвивалися в 80-х роках. З часом інтерес дослідників на багато років залучив багаторівневий синтез, використовуваний при проектуванні цифрових систем на основі FPGA (Field Programmable Gate Array).

В останні роки спостерігається явне протиріччя: архітектури ПЛІС бурхливо розвиваються й удосконалюються, а методи проектування на їх основі залишаються без зміни.

Інтегроване середовище MAX+PLUS II фірми Altera пропонує повний спектр можливостей логічного дизайну: різноманітні засоби опису проектів з ієрархічною структурою, потужний логічний синтез, компіляцію з заданими часовими параметрами, розподілення на підпрограми основного проекту, функціональне і часове тестування (симуляцію), тестування декількох взаємопов’язаних властивостей, аналіз часових параметрів системи, автоматичну локалізацію помилок, а також програмування і верифікацію помилок.

Відносно низьку популярність даного інтегрованого середовища серед вітчизняних проектувальників можливо пояснити відсутністю детальної та ємної документації українською мовою про можливості та властивості MAX+PLUS II. Ліквідацію саме такого інформаційного браку і було взято автором за стратегічну мету написання дипломної роботи.

Для спрощення розуміння читачем структурної організації і функціонального призначення додатків інтегрованого середовища в роботі наведено генезис програмувальних логічних інтегральних схем, їх класифікація, архітектура, детально розписана процедура створення нового проекту і процес його компіляції.

В дипломній роботі наведено приклади опису в інтегрованому середовищі MAX+PLUS II всіх базових пристроїв мікроелектроніки, як то:

1) JK-тригера, D-тригера, RS-тригера;

2) послідовних регістрів зсуву, паралельних кільцевих регістра зсуву;

3) лічильників з крізним переносом, асинхронних лічильників, лічильників віднімання, універсального лічильника;

4) шифраторів, дешифраторів, мультиплексорів, демультиплексорів (з використанням функцій алгебри логіки і таблиць дійсності);

5) суматорів, віднімачів.

Похожие работы

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

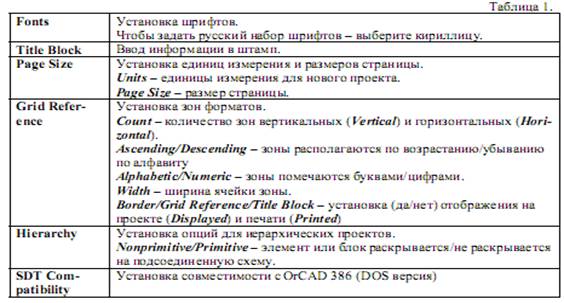

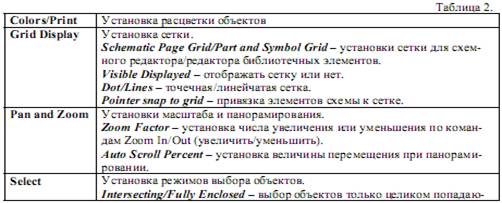

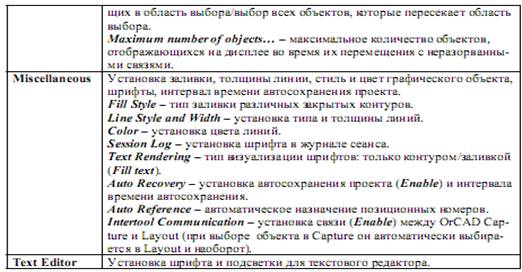

... КП, відповідно; X Offset, Y Offset – зсув точки підключення траси відносно геометричного центру КП по осях X і Y, відповідно. Таблиця апертур (Apertures) містить опис використовуваних апертур. Таблиця Layers містить список шарів, використовуваних OrCAD Layout. Шари можуть бути наступних типів: Routing – шар трасування; Plane – шар металізації; Drill – шар символів отворів; Jumper – шар ...

... результаты отчета. Они являются кульминационным пунктом отчета и должны быть разумными, хорошо определенными, перечисленными и обоснованными [11].Практика дистанционного образования с использованием Internet Шутилов Ф.В. Особенности заочного образования - в необходимости обеспечить высокий уровень знаний при значительно меньшем времени непосредственного личного общения студентов с преподавателем. ...

0 комментариев