Навигация

Способы адресации операндов

4. Способы адресации операндов

Существуют следующие способы адресации операндов-источников:

- регистровая адресация;

- прямая адресация;

- косвенно-регистровая адресация;

- непосредственная адресация;

- косвенная адресация по сумме базового и индексного регистра.

Первые три способа используются также для адресации операнда назначения. Указанные пять способов адресации, используемые в различных сочетаниях, обеспечивают 21 режим адресации. Многие команды содержат поля: "приемник", "источник", которые определяют тип данных, метод адресации и участвующие операнды.

Для команд, не выполняющих операции перезаписи, операнд назначения является и операндом-источником.

Большое количество команд включает операнды, расположенные во внутреннем ОЗУ данных ОМЭВМ. Выбор адресного пространства памяти программ или внешней памяти данных в качестве второго операнда определяется командной мнемоникой (если только второй операнд не является непосредственной величиной).

Адресуемая область внутреннего ОЗУ данных определяется способом адресации и величиной адреса. Например, обращение к регистрам специальных функций может быть выполнено только с помощью прямой адресации.

Регистровая адресация. Регистровая адресация используется для обращения к восьми регистрам выбранного банка (эти же регистры могут быть выбраны с помощью прямой адресации и косвенно-регистровой адресации как обычные ячейки внутреннего ОЗУ данных).

Регистровая адресация используется также для обращения к регистрам А, В, АВ (сдвоенному регистру), DPTR и к флагу переноса С. Использование регистровой адресации позволяет получать двухбайтовый эквивалент трехбайтовых команд прямой адресации.

ПРИМЕР: MOV A,Rn; CLR A; DEC Rn; ADD A,Rn; MOV DPTR,#data16 и др.

Прямая адресация. Прямая байтовая адресация используется для обращения к ячейкам внутренней памяти (ОЗУ) данных (0 – 127) и к регистрам специальных функций.

ПРИМЕР: MOV A,direct(MOV A,4FH); MOV direct,direct; IN direct; ADD A,direct и др.

Прямая побитовая адресация используется для обращения к отдельно адресуемым 128 битам, расположенным в ячейках с адресами 20Н–2FH и к отдельно адресуемым битам регистров специальных функций.

ПРИМЕР: SETB BIT(SETB 1FH); CLR TF0; CLR C.

Косвенно-регистровая адресация. Косвенно-регистровая адресация используется для обращения к ячейкам внутреннего ОЗУ данных. В качестве регистров-указателей используется регистры R0, R1 выбранного банка. В командах PUSH и POP используется содержимое указателя стека (SP). Косвенно-регистровая адресация используется также для обращения к внешней памяти данных. В этом случае с помощью регистров-указателей R0 и R1 (выбранного банка рабочих регистров) выбирается ячейка из блока в 256 байт внешней памяти данных. 16-разрядный указатель данных (DPTR) может быть использован для обращения к любой ячейке адресного пространства внешней памяти данных объемом до 64 Кбайт.

ПРИМЕР: MOV A,@Ri (MOV A,@R0); INC @Ri; ADD A,@Ri; XRL A,@Ri; MOVX @Ri,A; MOVX A,@DPTR.

Непосредственная адресация. Непосредственная адресация позволяет выбрать из адресного пространства памяти программ константы, явно указанные в команде.

ПРИМЕР: MOV A,#data (MOV A,#1FH); MOV DPTR,#data16 (MOV DPTR,#5B4EH); ADD A,#data; XRL A,#data.

Косвенно-регистровая адресация по сумме базового и индексного регистров. Косвенно-регистровая адресация по сумме: базовый регистр плюс индексный регистр (содержимое аккумулятора А) упрощает просмотр таблиц, зашитых в памяти программ. Любой байт из таблицы может быть выбран по адресу, определяемому суммой содержимого DPTR или PC и содержимого А.

ПРИМЕР: MOVC A,@A+DPTR; MOVC A,@A+PC; JMP @A+DPTR.

5 Программная модель битового процессора

Пригодность архитектуры каждого компьютера для конкретного класса задач определяется тем, насколько его система команд соответствует задачам, которые должны быть выполнены. Поэтому для дискретного управления в реальном масштабе времени наличие в системе команд операций непосредственно над битами приводит к созданию более производительных систем и программ обработки входной и выходной двоичной информации. С этой целью в ОМЭВМ семейства MCS-51 введены специальные средства, называемые битовым процессором, которые поддерживают прямые логические операции с отдельными битами и операции их тестирования и позволяют использовать однобитовые переменные в логических операциях.

В связи с этим в систему команд ОМЭВМ семейства MCS-51 введены специальные инструкции для выполнения операций с битовыми переменными. Имеется 17 таких команд, которые перечислены в табл. 3.

Таблица 3 – Команды битового процессора

| Мнемоническое обозначение | Описание команды | Число байтов | Число циклов |

| SETB C | Установка флага переноса | 1 | 1 |

| SETB bit | Установка бита | 2 | 1 |

| CLRC | Сброс флага переноса | 1 | 1 |

| CLR bit | Сброс бита | 2 | 1 |

| CPL C | Инверсия флага переноса | 1 | 1 |

| CPL bit | Инверсия бита | 2 | 1 |

| MOV C, bit | Пересылка бита во флаг переноса | 2 | 1 |

| MOV bit,C | Пересылка флага переноса в бит | 2 | 2 |

| ANL C, bit | "Логическое И" бита и флага переноса | 2 | 2 |

| ANL. C, /bit | "Логическое И" инверсии бита и флага переноса | 2 | 2 |

| ORL C, bit | "Логическое ИЛИ" бита и флага переноса | 2 | 2 |

| ORL C,/bit | "Логическое ИЛИ" инверсии бита и флага переноса | 2 | 2 |

| JC rel8 | Переход, если флаг переноса установлен | 2 | 2 |

| JNC rel8 | Переход, если флаг переноса сброшен | 2 | 2 |

| JB bit,rel8 | Переход, если бит установлен | 3 | 2 |

| JNB bit,rel8 | Переход, если бит сброшен | 3 | 2 |

| JBC bit,rel8 | Переход, если бит установлен, и сброс этого бита | 3 | 2 |

ОБОЗНАЧЕНИЯ:

С – флаг переноса;

bit – 128 программно-доступных битов, любой I/O вывод, бит управления или состояния;

/bit – 128 программно-доступных битов, любой I/O вывод, бит управления или состояния, взятые с инверсией;

rel8– байт относительного смещения (условный переход осуществляется в диапазоне от -128 до +127 байтов относительно адреса первого байта следующей команды).

Эти команды в зависимости от выполняемой функции могут быть одно-, двух- или трехбайтные. Те из них, которые оперируют с флагом переноса, имеют однобайтный код или код, за которым следует байт смещения, использующийся для вычисления адреса условного перехода (рис. 4.а). В более обобщенных командах битовых операций после кода добавляется байт адреса прямоадресуемого бита, образуя двух- или трехбайтные команды (рис. 4.б). На рис. 4 для справки приведены коды этих команд.

С помощью указанных команд можно обращаться непосредственно к 128 битам внутреннего ОЗУ и к 83 битам одиннадцати восьмиразрядных регистров ОМЭВМ.

| Код команды: | Код команды: | |||

| SETB С | 11010011В (D3H) | |||

| CLR С | 11000011В (С3Н) | |||

| CPL С | 10110011В(В3Н) | |||

| Код команды | Смещение | |||

| JC | <ге18> | 01000000В (40Н) | ||

| JNC | <ге18> | 01010000В (50Н) | ||

| а) Команды проверки и управления флагом переноса | ||||

| Код команды | Адрес бита | Код команды: | ||

| SETB | <bit> | 11010010B (D2H) | ||

| CLR | <bit> | 11000010В (С2Н) | ||

| CPL | <bit> | 10110010В (В2Н) | ||

| MOV С, | <bit> | 10100010В (А2Н) | ||

| MOV | <bit>, С | 10010010В (92Н) | ||

| ANL С, | <bit> | 10000010В (82Н) | ||

| ANL С, | </bit> | 10110000В (В0Н) | ||

| ORL С, | <bit> | 01110010В(72Н) | ||

| ORL С, | </bit> | 10100000В (А0Н) | ||

| Код команды | Адрес бита 1 | Смещение | ||

| JB | <bit>, | <ге18> | 00100000В (20Н) | |

| JNB | <bit>, | 00010000В (10H) | 00110000В (30Н) | |

| JBC | <bit>, | <ге18> | 00010000В (10H) | |

| б) Команды проверки и операций с битами | ||||

Рисунок 4 – Форматы команд операций над битами

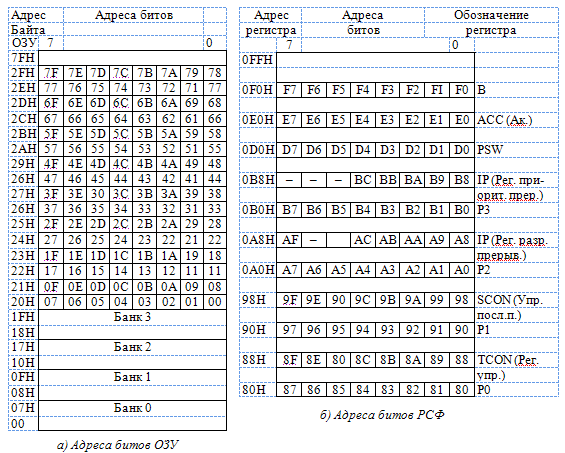

В зависимости от значения байта адреса прямо адресуемый бит выбирается из двух групп битов. Значения адреса от 0 (00Н) до 127 (7FH) определяют биты в 16-байтном блоке внутреннего ОЗУ между адресами 20Н и 2FH (см. рис.5а). Они пронумерованы последовательно от младшего бита младшего байта к старшему биту старшего байта. Адреса битов от 128 (80Н) до 255 (0FFH) соответствуют битам регистров специальных функций. Адреса этих битов вычисляются иначе, чем адреса ячеек ОЗУ: пять старших битов адреса совпадают с собственными адресами регистров, а три младших бита адреса идентифицируют позицию бита в пределах регистра (см. рис.5б).

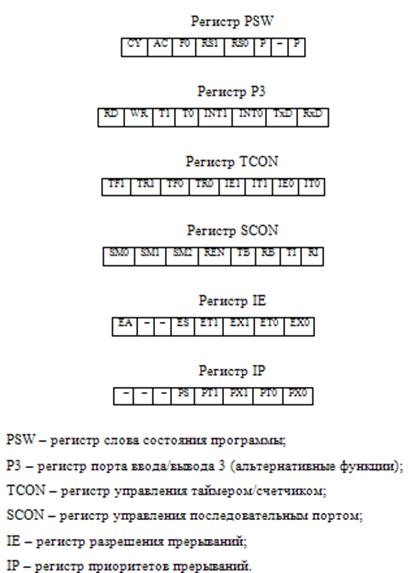

Хотя MCS-51 имеет 20 регистров специальных функций, побитовый доступ обеспечен только для 11 (PSW, АСС, В, P0, P1, P2, P3, TCON, SCON, IE, IP). У 6 из них (PSW, Р3, TCON, SCON, IE, IP) разряды имеют собственные символические имена (рис.6).

Команды общего назначения, адресующиеся непосредственно к битам, могут обращаться к ним (в том числе и к биту переноса), используя соответствующую мнемонику: CY, AC, F0 и т.д.

К битам всех 11 регистров также можно обратиться, используя соответствующее позиционное обозначение: PSW.1, АСС.2, В.З, Р0.4 и т.д.

Регистр АСС (аккумулятор) и регистр В относятся к байтовой арифметике, но их отдельные биты могут использоваться в программе в качестве произвольных 16 флагов. В сумме со 128 ячейками ОЗУ это дает 144 битовые ячейки общего назначения для хранения переменных или программных флагов.

Рисунок 5 – Адреса прямо адресуемых битов

Все 32 вывода портов Р0-РЗ могут индивидуально адресоваться как вход, выход или вход/выход в любой комбинации. Любой вывод может служить программно реализуемым стробом, тестовым входом или последовательным каналом ввода/вывода.

Для обработки битов регистров ОЗУ, не имеющих побитового доступа, могут быть использованы логические операции с байтами.

Регистр слова состояния программы PSW содержит биты флагов и состояния процессора, включая флаг переноса. Операции обработки байтов, воздействуя на регистр PSW, могут таким образом влиять и на бит переноса.

Рисунок 6 – Формат регистров специальных функций, имеющих символические имена прямо адресуемых битов

В языке ассемблера MCS-51, как показано в табл.3, адрес бита указывается одним из трех способов: числом или выражением, соответствующим прямому адресу бита; названием или адресом регистра, содержащего данный бит, и позицией бита в регистре (0-7), разделенными точкой; для определенных битов (рис.6) – указанием символического имени. Биты также могут обозначаться произвольными именами директивой ассемблера "BIT". Например, 5-й бит регистра PSW может быть очищен любой из четырех команд:

| USR_FLG | BIT PSW.5 | ; Описание символа пользователя |

| CLR 0D5H | ; Абсолютная адресация | |

| CLR PSW.5 | ; Использование точечного оператора | |

| CLR F0 | ; Использование собственного имени бита | |

| CLR USR_FLG | ; Символ пользователя. |

Похожие работы

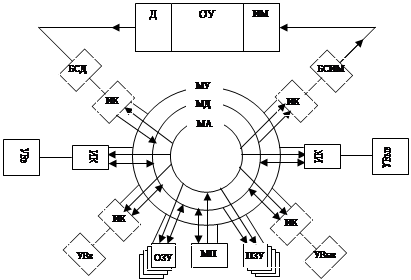

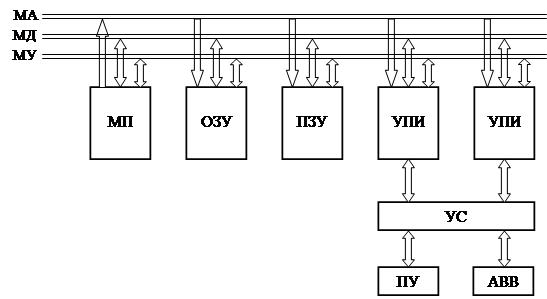

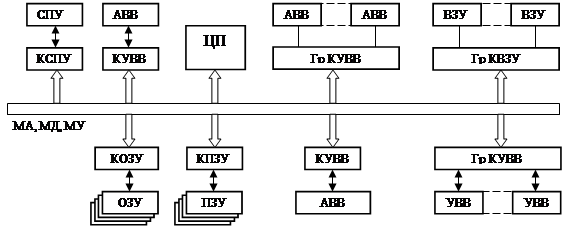

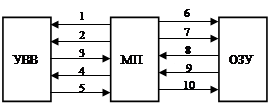

... ввести распределенную обработку во всех подсистемах вычислительной системы, что определяет новые способы организации вычислительных процессов в системах с децентрализованными управлением и обработкой информации. 2. Интерфейс микропроцессоров Для включения микропроцессора в любую микропроцессорную систему необходимо установить единые принципы и средства его сопряжения с остальными устройствами ...

... 0,1098 4.4 Выбор сторожевого таймера. Т.к. работа системы происходит в автономном режиме и не предусматривает работу оператора с ней, то для случая зависания микро-ЭВМ в схему системы сбора данных добавляется интегральная микросхема MAX690AMJA – сторожевой таймер. Выполняющая две основные функции: выведение МП из состояния зависания и сброс МП при включении питания. Основные характеристики ...

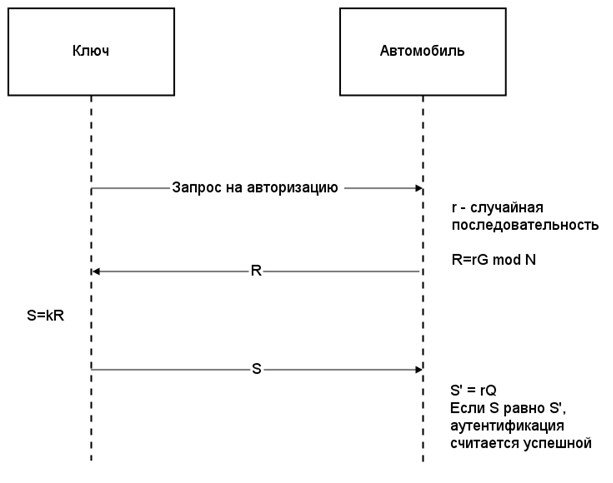

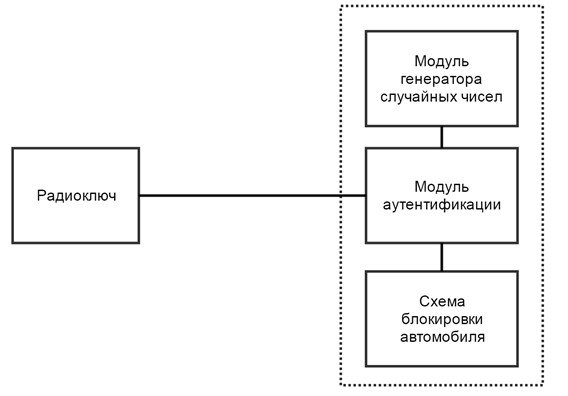

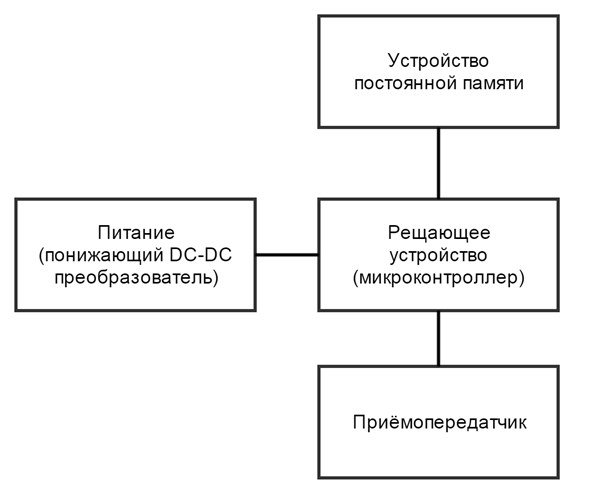

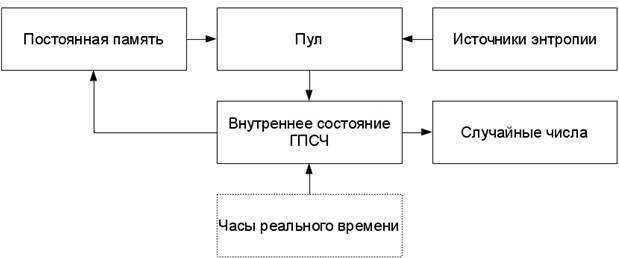

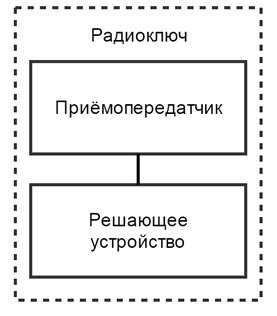

... является допустимым для устройства подобного рода. 5.3 Вывод В результате анализа параметров энергосбережения было выявлено то, что при реализации системы аутентификации пользователя транспортного средства нельзя обойтись без анализа энергопотребления системы и поиска путей уменьшения этого параметра. Изначально спроектированная система вызывала бы дискомфорт у пользователя за счёт излишне малого ...

... ввод ложного сообщения (даже ранее записанного с того же голоса) легко обнаруживается по изменению содержания. Технические требования предъявляемые к системе взаимодействия периферийных устройств при обработке данных в стандарте DES. Система взаимодействия с периферийными устройствами должна работать в режиме открытой и закрытой передачи. В открытом режиме на передаче информация не шифруется, ...

0 комментариев