Навигация

4. Используемая аппаратура

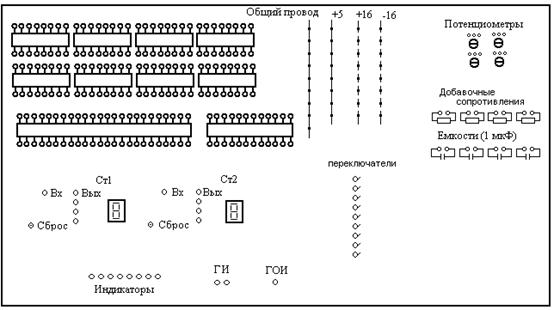

Лабораторный стенд, лицевая панель которого представлена на рисунке в прил. 1, цифровой вольтметр, приборы для измерения постоянных токов и напряжений, осциллограф типа С1–6В (или другой).

5. Подготовка к работе

Изучить параметры интегральных схем серии К155 [I].

Изучить описание лабораторной работы.

Изучить описание лабораторной установки (см. прил. 1).

Произвести синтез комбинационной схемы. Данные взять из табл. 2.

Таблица 2

| X1 | X2 | X3 | Варианты Y У | ||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | |||

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 1 1 1 0 1 0 1 | 1 1 0 0 1 0 1 0 | 0 0 1 0 0 1 1 1 | 0 0 0 1 1 1 0 0 | 1 1 1 0 0 0 1 1 | 1 1 0 1 0 0 0 1 | 0 0 0 1 1 1 1 0 | 1 0 0 0 1 1 1 1 | 1 0 1 0 1 1 1 0 | 0 1 0 1 1 0 0 1 | 0 0 0 1 0 1 1 1 | 0 1 0 1 0 1 0 1 | 0 1 0 1 1 0 1 0 |

По заданной таблице истинности написать логическое выражение в СДНФ. Произвести минимизацию, используя эвристические методы и карты Карно. По полученному выражению составить структурную схему.

6. Порядок выполнения работы

Познакомиться с лабораторным стендом и с наборным полем стенда. Найти ручки управления и необходимые приборы на наборном поле стенда.

– Определение статических характеристик.

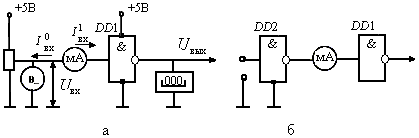

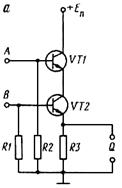

Для определения статических характеристик и параметров ИМС ТТЛ нужно собрать схему исследования согласно рис. 11, а (источник +5 В подключается к ЛЭ при включении питания стенда). Выходное напряжение измеряется цифровым вольтметром.

Изменяя напряжение на входе с помощью потенциометра В1, фиксировать входной ток, входное и выходное напряжения. Особо отметить входное напряжение, при котором Iвх = 0. Для уверенного построения характеристик следует получить 8–10 точек отсчетов, увеличивая их частоту при быстром измерении той или иной величины.

Рис. 11. Схемы для экспериментального изучения передаточной и входной характеристик

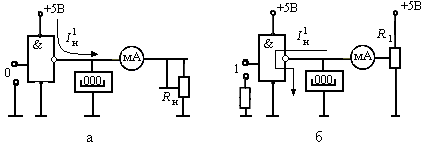

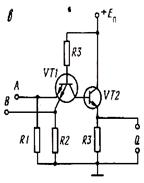

Рис. 12. Схемы для снятия выходных характеристик

Измерить входной ток I0вх и I1вх при работе ЛЭ друг на друга. Для этого собрать схему измерения согласно рис. 11 (б). Для получения на выходе DD2 низкого уровня – «0», вход ее необходимо подключить к высокому уровню – «I». Для обеспечения «I» – вход подключить к низкому уровню – «0».

– Исследование выходных характеристик

Собрать схему измерения согласно рис. 12а, подключив вход DD1 к «0». Изменяя величину Rн, регистрировать ток I1н = I1вх и U1н = U1вх

Внимание! Следите, чтобы выходной ток не превысил допустимый для данного типа ИМС. Данные свести в табл. 3.

Изменить схему, подключив вход ЛЭ к «I». В этом случае ток нагрузки «втекает» в ЛЭ. Изменяя напряжение делителя R1, регистрировать I0н и U0вых. Данные свести в табл. 3.

Таблица 3

| U0вых, В | ||||||||||

| I0н, мА |

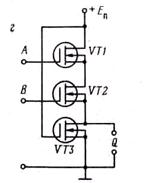

– Исследование ЛЭ с тремя состояниями выходной проводимости

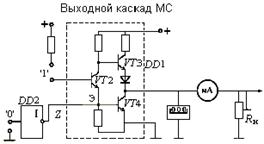

Рис. 13. Схема исследования ЛЭ в третьем состоянии

Собрать схему (см. рис. 13). На вход ЛЭ DD1 подать «1». На выходе элемента окажется низкий уровень напряжения, что и будет зафиксировано вольтметром. На вход DD2 подать «0». Убедиться, что это не повлияло на состояние выхода DD1. Подключить вход DD2 к ‘1’. При этом на выходе инвертора будет низкий потенциал и он закроет транзистор VT4 микросхемы DD1. В результате оба выходных транзистора DD1 окажутся закрытыми, что соответствует третьему состоянию с высоким выходным сопротивлением.

– Помехоустойчивость ТТЛ

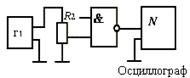

Собрать схему согласно рис. 14. Постепенно увеличивая амплитуду импульсов на входе ЛЭ, отметить момент, когда на выходе появятся заметные помехи, составляющие 0,1 от полной амплитуды выходного напряжения. Измерить осциллографом амплитуду импульсов на входе.

Рис. 14. Схема для определения помехоустойчивости ЛЭ ТТЛ

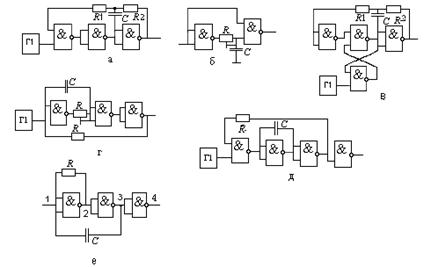

Рис. 15. Схемы формирователей и генераторов на ТТЛ элементах. Сопротивление RI может отсутствовать, сопротивление R2 выбирать в пределах к2 – 4к

– Исследование комбинационной схемы

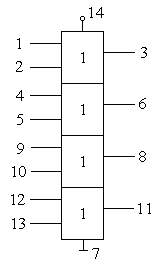

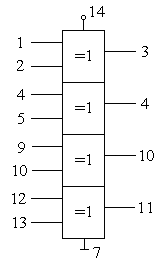

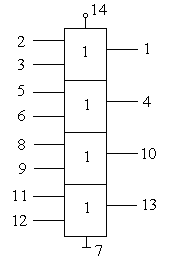

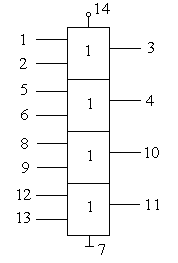

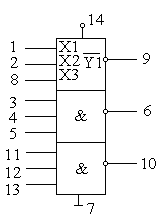

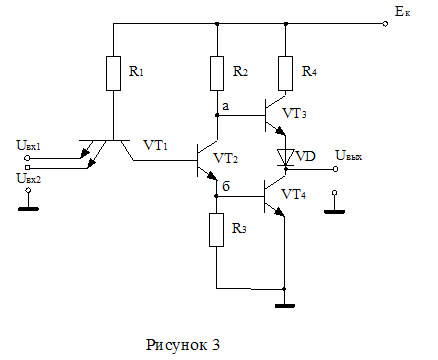

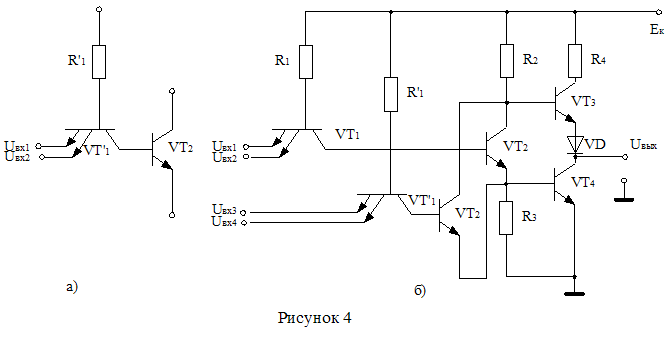

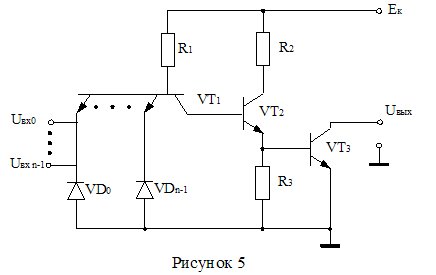

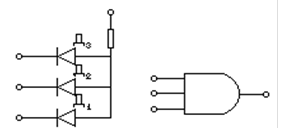

– Проверить соответствие таблице истинности преобразований, представленных на рис. 5. Для этого подавать на вход ЛЭ уровни «О» и «I», отмечая результат на выходе.

– Собрать спроектированную комбинационную схему и убедиться в правильности ее функционирования. Входные сигналы Х и Т взять с регистра кодов. Выход контролируется с помощью лампочки индикации.

– Формирователи на ЛЭ

Собрать одну из схем формирователей на ЛЭ ТТЛ и убедиться в ее работоспособности с помощью осциллографа (рис. 15). Запускающие импульсы и перепады напряжения взять с соответствующих выходов, расположенных на наборном поле.

Подать на один вход схемы И-НЕ импульс с ГИ, а на другой – импульс со спроектированного формирователя (оба импульса должны быть положительной полярности). Сравнить длительность импульса на выходе ЛЭ с длительностями на входе. Изобразить осциллограммы, объяснить результат.

7. Обработка результатов измерений

7.1 По результатам измерений построить графики передаточной Uвых = F(Uвх), входной Iвх = F(Uвх) и выходной Uвых = F(Iвых) характеристик. Из графиков определить пороговое напряжение, входное сопротивление для низкого и высокого уровня напряжения на входе (0,4 и 2,4 В), а также выходное сопротивление при низком и высоком уровнях напряжения на выходе:

Rвых = ∆ Uвых / ∆Iн(Uвх).

По полученным результатам вычислить коэффициент объединения по входу и нагрузочную способность рассмотренного ЛЭ.

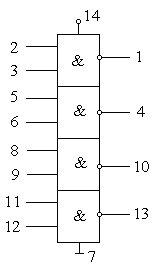

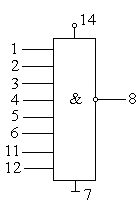

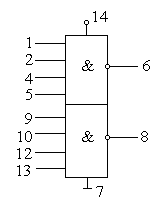

7.2 Записать логическую функцию выбранного варианта. Показать этапы ее минимизации. Составить схему соединений ЛЭ полученной функции в базисе И-НЕ (И-ИЛИ-НЕ).

Объяснить полученные результаты.

8. Содержание отчета

В отчете к лабораторной работе представить:

– схемы измерений, таблицы результатов и расчеты,

– этапы анализа логической функции и ее минимизации, схемы соединений;

– схемы для проверки таблиц истинности и результаты;

– схему формирователя с анализом ее работы;

– осциллограммы работы формирователя.

Библиографический список

1. Угрюмов Е.П. Цифровая схемотехника: учебное пособие для вузов / Е.П. Угрюмов. 2-е изд., перераб. и доп. СПб.: БХВ – Санкт-Петербург, 2004.

800 с.: ил.

2 Бабич Н.П. Компьютерная схемотехника./ Н.П. Бабич, И.А. Жуков. Киев.: «МК-Пресс», 2004. 576 с.: ил.

3 Алексенко А.Г. Основы микросхемотехники/ А.Г. Алексенко. 3‑е изд., перераб и доп. М.: ЮНИМЕДИАСТАЙЛ, 2002. 448 с.: ил.

4 Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования/ Ю.В. Новиков. М.: Мир, 2001. 379 с.: ил.

5 Прянишников В.А. Электроника: курс лекций / В.А. Прянишников. СПб.: «Корона принт», 1998. 400 с. ил.

6 Завадский В.А. Компьютерная электроника / В.А. Завадский. Киев: ТОО ВЕК, 1996. 368 с. ил.

7 Опадчий Ю.Ф. Аналоговая и цифровая электроника / Ю.Ф. Опадчий, О.П Глудкин, А.И Гуров. М.: Изд. «Горячая линия – телеком», 1999. 768 с. ил.

8 Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре/ Е.А. Зельдин. Л.: Энергоатомиздат, 1986. 280 с. ил.

9 Шило В.Л. Популярные цифровые микросхемы: справочник/ В.Л. Шило. 2-е изд. Челябинск: Металлургия, Челябинское отд-ние, 1989. 352 с. ил.

Приложение 1

Описание лабораторной установки

Измерение параметров интегральных логических схем осуществляется на универсальном лабораторном стенде.

Универсальный лабораторный стенд имеет на передней панели ряд стабилизированных источников питания. Источники питания с помощью внешних проводничков подключаются к исследуемым схемам. С помощью таких же проводничков соединяются соответствующие выводы микросхем. Измерительные приборы подключаются к схеме внешними проводами.

На рисунке представлено коммутационное поле лицевой панели лабораторного стенда. На ней имеются выводы разъемов, в которые можно устанавливать исследуемые микросхемы. На стенде имеются генераторы одиночных импульсов (ГОИ) и непрерывной последовательности импульсов (ГИ), лампочки индикации состояния ЛЭ, счетчики импульсов (СТ1 и СТ2) с цифровым индикатором, переключатели и некоторые другие элементы, необходимые для выполнения исследований.

Приложение 2

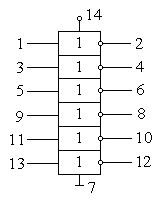

| Шесть элементов НЕ | Шесть буферных формирователей с открытым коллекторным выходом | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛН1, К155ЛН2, К155ЛН3, К155ЛН5, КP1533ЛН1, КP1533ЛН2 |

К155ЛН4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

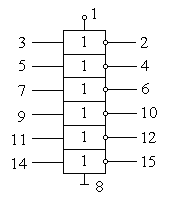

| Шесть логических элементов с буферным выходом | ||||||||||||||||||||||||||||||||||||

|

К564ЛН2 | ||||||||||||||||||||||||||||||||||||

|

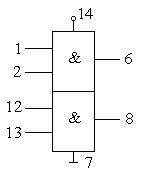

| Два логических элемента 2И | Два логических элемента 4И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

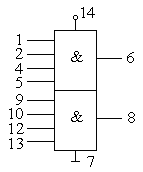

К155ЛИ5 |

К555ЛИ, КР1533ЛИ6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

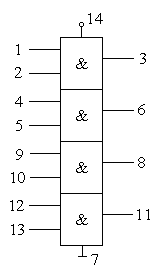

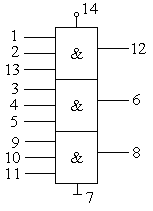

| Четыре логических элемента 2И | Три логических элемента 3И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛИ5 |

К555ЛИ1, КР1533ЛИ6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Четыре логических элемента 2ИЛИ | Четыре логических элемента исключающее ИЛИ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛЛ1, К555ЛЛ1, КР1533ЛЛ1 |

К564ЛП2, К176ЛП2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Четыре логических элемента 2ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛЕ1, К555ЛЕ1, К155ЛЕ5, К155ЛЕ6 |

К561ЛЕ5, К564ЛЕ5 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Три логических элемента 3ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛЕ4, К555ЛЕ4 |

К561ЛЕ10, К564ЛЕ10 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Два логических элемента 4ИЛИ-НЕ | ||||||||||||||||||||||||||||||||||||

|

К564ЛЕ6, К561ЛЕ6 | ||||||||||||||||||||||||||||||||||||

|

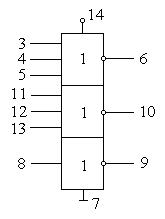

| Логический элемент 2–4И‑2ИЛИ-НЕ | Четыре логических элемента 2ИЛИ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛР4, К1533ЛР4 |

К155ЛЛ1, К555ЛЛ1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

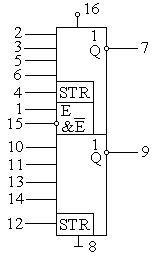

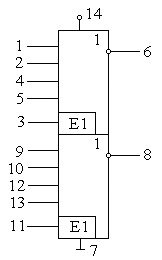

| Два логических элемента 4ИЛИ-НЕ со стробированием, один расширяемый по ИЛИ | Два логических элемента 4ИЛИ-НЕ со стробированием | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛЕ2 |

К155ЛЕ3 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Если на входе стробирования присутствует низкий уровень, вывод соответствующего элемента будет переведен в высокий уровень независимо от состояния других входов. Если на входе стробирования присутствует высокий уровень, элемент работает как обычный 4ИЛИ-НЕ. |

| Два элемента 4ИЛИ-НЕ и один инвертор | Два логических элемента 3ИЛИ-НЕ и логический элемент НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К176ЛП11 |

К176ЛП4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

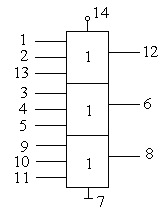

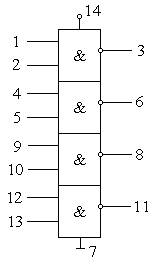

| Три логических элемента 3И-НЕ | Четыре логических элемента 2И-НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К564ЛА9 |

К155ЛА8, К555ЛА8 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

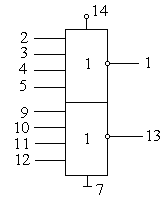

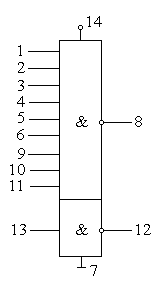

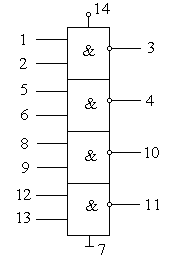

| Логический элемент 8И-НЕ | Два логических элемента 4И-НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛА2, К55ЛА2, КР1533ЛА2 |

К155ЛА1, К155ЛА6, К155ЛА7, К555ЛА1, К555ЛА7, КР1533ЛА1, КР1533ЛА7 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Элемент 9И-НЕ и один инвертор | 2 элемента 4И-НЕ и один инвертор |

|

К176ЛИ |

К176ЛП12 |

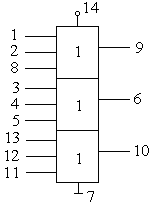

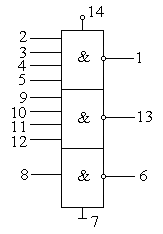

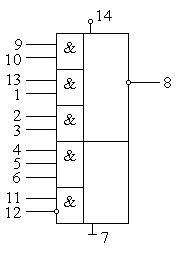

| Три логических элемента 3И-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛА4, К155ЛА10, К555ЛА10 |

К555ЛА4, КР1533ЛА4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

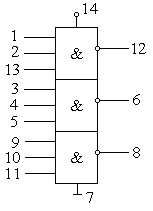

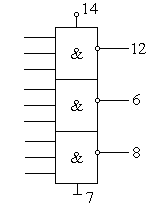

| Четыре элемента 2И-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛА3, К155ЛА9, К155ЛА12, К155ЛА13, К555ЛА3, К555ЛА9, К555ЛА12, К555ЛА13, КР1533ЛА3, КР1533ЛА9 |

К561ЛА7, К564ЛА7, К176ЛА7 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

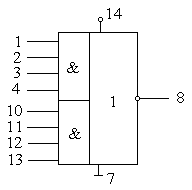

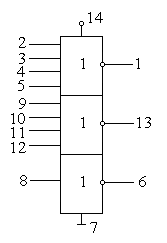

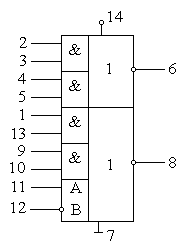

| Логический элемент 2–2И‑2ИЛИ-НЕ, один расширяемый по ИЛИ | Логический элемент 2–2–2–3И‑4ИЛИ-НЕ, с возможностью расширения по ИЛИ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

К155ЛР1 |

К155ЛР3 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Приложение 3

Основные параметры и характеристики микросхем КР155

| Входной ток, мА, не более · Низкого уровня ……………………………………………… · Высокого уровня …………………………………………… | -1,6 0,04 |

| Выходное напряжение, В · Низкого уровня, не более …………………………………. · Высокого уровня, не менее | 0,4 2,4 |

| Выходной ток, мА, не более · Низкого уровня ……………………………………………. · Высокого уровня …………………………………………… | 6 -0,4 |

| Нагрузочная способность…………………………………………… | 10 |

| Время задержки распространения сигнала, нс, при · Включении (Сн=50 пФ) ……………………………………. · Выключении (Сн=50 пФ) …………………………………… | 18,5* 18,5* |

| Средний ток потребления, мА, не более …………………………. | 15* |

| Помехоустойчивость, В, не более ………………………………… | 0,4 |

| Частота переключения, Гц, не более ……………………………… | 15 |

| Максимальное напряжение питания, В …………………………… | 6 |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В · 155 …………………………………………………………… · КР155 ………………………………………………………. | 45, – 5,5 4,75–5,25 |

| Максимальная емкость нагрузки, пФ ……………………………. | 200 |

| Диапазон рабочих температур, С · 155 …………………………………………………………… · КР155 ………………………………………………………. | -60+125 -10..+70 |

Основные параметры и характеристики микросхем КР555

| Входной ток, мА, не более · Низкого уровня ……………………………………………… · Высокого уровня …………………………………………… | -0,4 0,04 |

| Выходное напряжение, В · Низкого уровня, не более …………………………………. · Высокого уровня, не менее | 0,4 2,5 |

| Выходной ток, мА, не более · Низкого уровня ……………………………………………. · Высокого уровня …………………………………………… | 4 -0,4 |

| Нагрузочная способность…………………………………………… | 10 |

| Время задержки распространения сигнала, нс, при · Включении (Сн=50 пФ) ……………………………………. · Выключении (Сн=50 пФ) …………………………………… | 20* 20* |

| Средний ток потребления, мА, не более …………………………. | 3* |

| Помехоустойчивость, В, не более ………………………………… | 0,3 |

| Частота переключения, Гц, не более ……………………………… | 25 |

| Максимальное напряжение питания, В …………………………… | 5,5 |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В · 555 …………………………………………………………… · КР555 ………………………………………………………. | 45, – 5,5 4,75–5,25 |

| Максимальная емкость нагрузки, пФ ……………………………. | 150 |

| Диапазон рабочих температур, С · 555 …………………………………………………………… · КР555 ………………………………………………………. | -60+125 -10..+70 |

*Для микросхем типа ЛА3

Основные параметры и характеристики микросхем КР1533

| Входной ток, мА, не более · Низкого уровня ……………………………………………… · Высокого уровня …………………………………………… | -0,2 0,02 |

| Выходное напряжение, В · Низкого уровня, не более …………………………………. · Высокого уровня, не менее | 0,4 2,5 |

| Выходной ток, мА, не более · Низкого уровня ……………………………………………. · Высокого уровня …………………………………………… | 2 -0,2 |

| Нагрузочная способность…………………………………………… | 20 |

| Время задержки распространения сигнала, нс, при · Включении (Сн=50 пФ) ……………………………………. · Выключении (Сн=50 пФ) …………………………………… | 4 4 |

| Средний ток потребления, мА, не более …………………………. | 1 |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Частота переключения, Гц, не более ……………………………… | 100 |

| Максимальное напряжение питания, В …………………………… | 6 |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В……………………………………………. | 45, – 5,5 |

| Максимальная емкость нагрузки, пФ ……………………………. | 50 |

| Диапазон рабочих температур, С……………………………… | -10..+70 |

Основные параметры и характеристики микросхем КР176

| Входной ток, мкА, не более · Низкого уровня ……………………………………………… · Высокого уровня …………………………………………… | 1,0 1,0 |

| Выходное напряжение, В · Низкого уровня, не более …………………………………. · Высокого уровня, не менее | 0,3 8,2 |

| Выходной ток, мкА, не более · Низкого уровня ……………………………………………. · Высокого уровня …………………………………………… | 2 -0,2 |

| Нагрузочная способность…………………………………………… | 50 |

| Время задержки распространения сигнала, нс, при · Включении (Сн=50 пФ) ……………………………………. · Выключении (Сн=50 пФ) …………………………………… | 200 200 |

| Средний ток потребления, мА, не более …………………………. | 3 |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Частота переключения, Гц, не более ……………………………… | 100 |

| Максимальное напряжение питания, В …………………………… | 9 |

| Максимальное напряжение на входе, В …………………………. | 8,5 |

| Напряжение питания, В……………………………………………. | 9±5% |

| Максимальная емкость нагрузки, пФ ……………………………. | 50 |

| Диапазон рабочих температур, С……………………………… | -40..+70 |

Основные параметры и характеристики микросхем КР654

| Входной ток, мкА, не более · Низкого уровня ……………………………………………… · Высокого уровня …………………………………………… | -0,05 1,0 |

| Выходное напряжение, В · Низкого уровня, не более …………………………………. · Высокого уровня, не менее | 2,9 7,2 |

| Выходной ток, мкА, не более · Низкого уровня ……………………………………………. · Высокого уровня …………………………………………… | 0,5 -10 |

| Нагрузочная способность…………………………………………… | 50 |

| Время задержки распространения сигнала, нс, при · Включении (Сн=50 пФ) ……………………………………. · Выключении (Сн=50 пФ) …………………………………… | 110 160 |

| Средний ток потребления, мА, не более …………………………. | 6 |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Частота переключения, Гц, не более ……………………………… | 100 |

| Максимальное напряжение питания, В …………………………… | 10 |

| Максимальное напряжение на входе, В …………………………. | 9,5 |

| Напряжение питания, В……………………………………………. | 10±10% |

| Максимальная емкость нагрузки, пФ ……………………………. | 50 |

| Диапазон рабочих температур, С……………………………… | -60..+125 |

Похожие работы

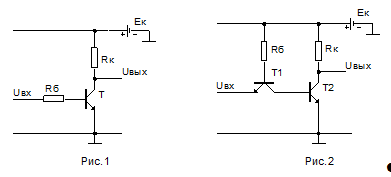

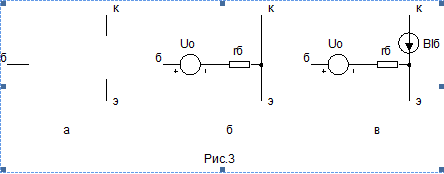

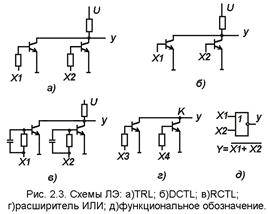

... (Cн >Cк) может быть существенно больше, чем длительность выключения тока, и составляет ( 16 ) 4. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ ТТЛ ТТЛ - обозначает получившую широкое распространение технологию изготовления интегральных схем (ИС) – транзисторно-транзисторную логику. Отличительной особенностью данной технологии является использование на входах ИС многоэмиттерных транзисторов. На ...

... первой логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения числа компонентов ЛЭ и роста площади кристалла ИМС. В существующих сериях интегральных микросхем основные логические элементы выполняются, как правило, с небольшим числом входов . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение ...

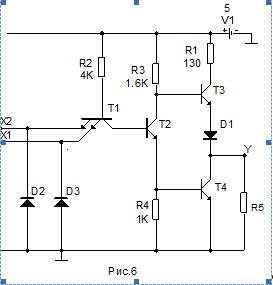

... устройства за счет исключения дополнительных элементов, реализующих операцию И; 2. Обеспечить работу нескольких выходов на общую шину, т.е. реализовать режим работы с разделением информации по времени. Базовые логические элементы эмиторно-связной логики Причиной появления БЛЭ ЭСЛ явилось желание повысить быстродействие цифровых устройств. Это желание привело к использованию в них совершенно ...

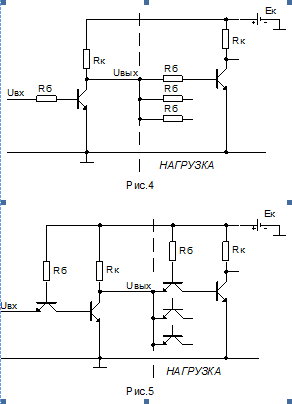

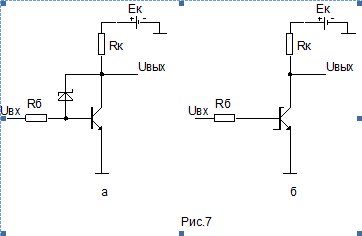

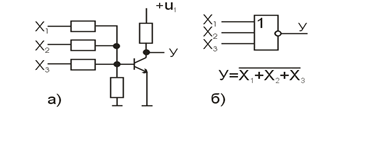

... 7. Логический элемент НЕ, выполненный на обычном биполярном транзисторе (а); многоэмиттерном транзисторе с дополнительным усилителем (б); Транзистор Шоттки и его условное графическое изображение в электронных схемах (в). Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б). Логический элемент И – ...

0 комментариев