Навигация

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

АНГАРСКАЯ ГОСУДАРСТВЕННАЯ ТЕХНИЧЕСКАЯ АКАДЕМИЯ

ФАКУЛЬТЕТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ

КАФЕДРА ПРОМЫШЛЕННОЙ ЭЛЕКТРОНИКИ И ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ ТЕХНИКИ

РЕФЕРАТ

по курсу: Импульсная техника

тема: Логические элементы

Выполнил

Студент гр. ПЭ-98-1ФИРСОВ Д.В.

Приняла:

КУРЧЕНКО О.А.

Должность: ст преподаватель

Подпись:____________

Оценка:

Ангарск 2001 г.

СодержаниеВведение.. 2

Параметры логических интегральных микросхем... 3

Диодно-транзисторная логика.. 3

Транзисторно-транзисторные логические элементы... 4

Базовые логические элементы эмиторно-связной логики.. 8

Принцип действия и функциональные возможности БЛЭ ЭСЛ. 10

СХЕМОТЕХНИКА БЛЭ КМОП-ТИПА.. 11

БЛЭ Интегрально-инжекционной логики.. 13

Список используемой литературы... 15

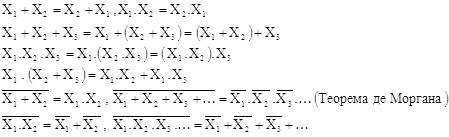

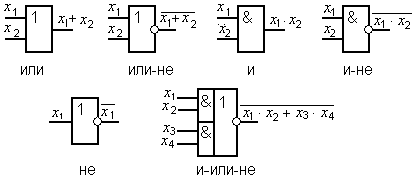

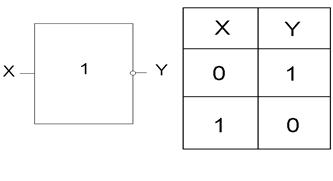

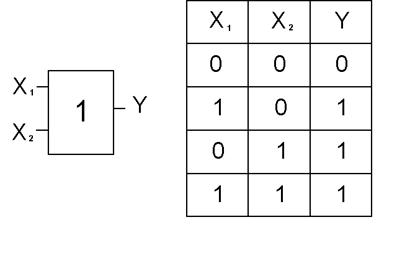

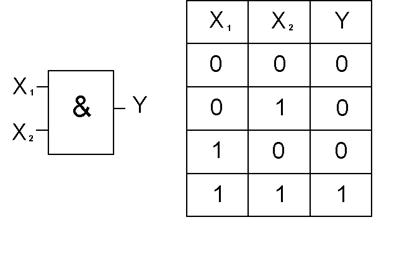

ВведениеВ большинстве современных ЭВМ и цифровых устройствах различного назначения обработка информации происходит с помощью двоичного кода, когда информационные сигналы могут принимать только два значения: 1 и 0. Операции по обработке двоичной информации выполняют логические элементы.

Используя набор логических элементов, выполняющие элементарные логические операции И, ИЛИ, НЕ, можно реализовать в двоичном коде любую сложную логическую функцию.

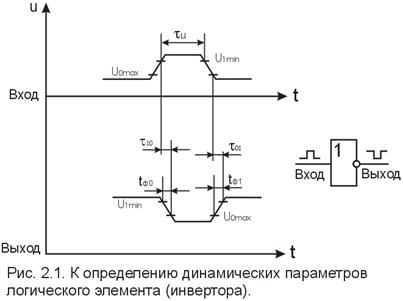

Параметры логических интегральных микросхем1 Входное U1вх и выходное U1вых напряжение логической единицы – значение высокого уровня напряжения на входе и выходе микросхемы;

2 Входное U0вх и выходное U0вых напряжение логического нуля – значение низкого уровня напряжения на входе и выходе микросхемы;

3 Входной I1вх и выходной I1вых токи логической единицы, входной I0вх и выходной I0вых токи логического нуля;

4 Логический период сигнала ![]() , пороговое напряжение Uпор вх – напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

, пороговое напряжение Uпор вх – напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

5 Входное сопротивление логической ИМС – отношение приращения входного напряжения к приращению входного тока (различают R0вх и R1вх), выходное сопротивление – отношение приращения выходного напряжения к приращения выходного тока (различают R0вых и R1вых);

6 Статическая помехоустойчивость – максимально допустимое напряжение статической помехи по высокому U1пом и низкому U0пом уровням входного напряжения, при котором еще не происходят изменения уровня выходного напряжения микросхемы;

7 Средне потребляемая мощность Pпотр ср = (P0потр + Р1потр)/2 , где P0потр и Р1потр – мощности, потребляемые микросхемой в состоянии соответственно логического нуля и единицы на выходе;

8 Коэффициент объединения по входу Коб, показывающий, какое число аналогичных логических ИМС можно подключить к входу данной схемы, и определяющий максимальное число входов логической ИМС;

Коэффициент разветвления по входу Кразв, показывающий какое количество аналогичных нагрузочных микросхем можно подключить к выходу данной ИМС, и характеризующий нагрузочную способность логической ИМС.

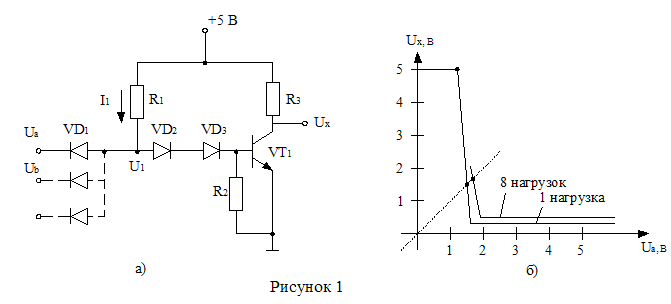

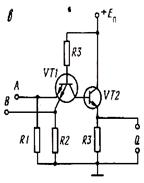

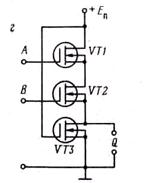

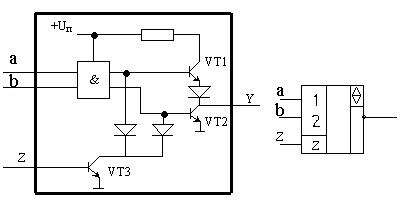

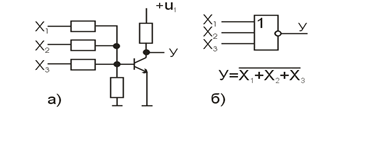

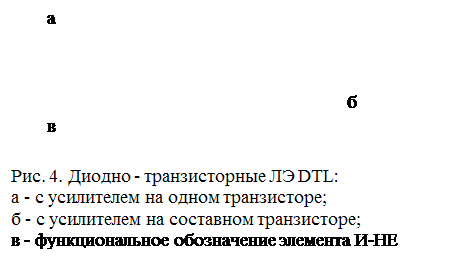

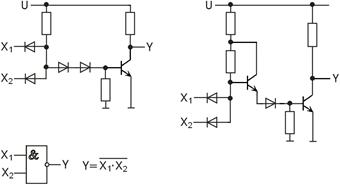

Диодно-транзисторная логика Одним из первых семейств цифровой логики мы рассмотрим диодно-транзисторную логику. Основная схема ДТЛ приведена в соответствии с рисунком 1а. Если отбросит часть схемы, изображенную пунктиром, схема превращается в инвертор, и по ней можно построить передаточную характеристику Ux от Ua. Если напряжение на входе А равно 0, то диод VD1 смещен в прямом направлении и напряжение U1 равно +0,6 В. Эта величина недостаточна для открывания диодов VD2 и VD3 и перехода база-эмиттер транзистора VТ1. Поэтому ток i1 течет через диод VD1, источник напряжения Ua и на землю. Транзистор VТ1 закрыт, при этом Ux = +5 В. Если Ua увеличивается, то U1 также растет до тех пор, пор пока не достигнет 1,2 В. При этом U1 = 1,8 В. В этот момент VD2, VD2, VТ1 открываются и ток i1 течет через транзистор VТ1 и переводит его в насыщение. Дальнейшее увеличение напряжение Ua запирает диод VD1. но не может повлиять на величину U1 или состояние транзистора VТ1. Это относительно резкое изменение величины напряжение Ux от +0,5 В до величены на насыщенном транзисторе Uкэ нас приведено, в соответствии с рисунком 1б. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны

Одним из первых семейств цифровой логики мы рассмотрим диодно-транзисторную логику. Основная схема ДТЛ приведена в соответствии с рисунком 1а. Если отбросит часть схемы, изображенную пунктиром, схема превращается в инвертор, и по ней можно построить передаточную характеристику Ux от Ua. Если напряжение на входе А равно 0, то диод VD1 смещен в прямом направлении и напряжение U1 равно +0,6 В. Эта величина недостаточна для открывания диодов VD2 и VD3 и перехода база-эмиттер транзистора VТ1. Поэтому ток i1 течет через диод VD1, источник напряжения Ua и на землю. Транзистор VТ1 закрыт, при этом Ux = +5 В. Если Ua увеличивается, то U1 также растет до тех пор, пор пока не достигнет 1,2 В. При этом U1 = 1,8 В. В этот момент VD2, VD2, VТ1 открываются и ток i1 течет через транзистор VТ1 и переводит его в насыщение. Дальнейшее увеличение напряжение Ua запирает диод VD1. но не может повлиять на величину U1 или состояние транзистора VТ1. Это относительно резкое изменение величины напряжение Ux от +0,5 В до величены на насыщенном транзисторе Uкэ нас приведено, в соответствии с рисунком 1б. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны

0≤U0≤1.2 B

1.5≤U1≤5 В

Практически U0 обычно меньше 0,4 В, а U1 очень близко к 5 В, что обеспечивает хороший шумовой запас по постоянному току.

Если на вход подано напряжение, соответствующее логической 1, то диод VD1 смещен в обратном направлении и, следовательно, потребляет минимальную мощность с выхода предыдущей схемы. Однако если на входе поддерживается напряжение логического 0, то ток i1 должен течь из входной клеммы элемента через насыщенный транзистор на землю. Это соответствует одной единичной нагрузке. Если к одному выходу подсоединено n входов, то насыщенный транзистор должен пропускать ток, в n раз больше чем i1. Если n увеличивается, то будет расти и напряжение Ua, что эквивалентно увеличению напряжения выходного транзистора. Этот эффект приведен в соответствии с рисунком 1б, где передаточная характеристика изображена для случая одной выходной единичной нагрузки и для случая восьми единичных нагрузок (максимально допустимое количество для базового элемента ДТЛ).

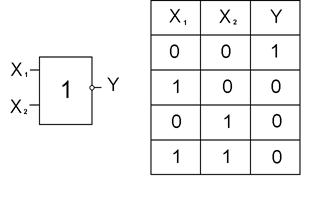

Если к схеме, в соответствии с рисунком 1а, добавить второй диод для получения входа Ub, то напряжение Ux будет соответствовать логической 1, если хотя бы один из входов будет в состоянии логического нуля. Логический нуль на выходе можно получить только в том случае, если на обоих входах присутствует напряжение логической единице, т.е. логическая операция выполняемая данной схемой имеет вид:

Х = ![]()

Что соответствует операции НЕ-И. Добавлением дополнительных диодов для расширения объема входа число входов в базовом элементе ДТЛ НЕ-И может доведено до 20.

Если выходы двух (и более) ДТЛ элементов НЕ-И соединены вместе, результирующая схема осуществляет операцию И на выходов элементов НЕ-И. Из схемы видно, что если хотя бы на одном из двух выходов присутствует напряжение логического нуля, то общий выход находится в состоянии логического нуля. Если оба выхода элемента НЕ-И в состоянии логической 1, то на выходе – тоже логическая единица. Такое соединение называется проводным И. Выходная нагрузочная способность такой схемы должна быть уменьшена на одну единичную нагрузку для каждого дополнительного выхода проводном соединении, так как следует учитывать возможность шунтирования общего выхода коллекторными сопротивлениями транзисторов, выходные напряжения которых соответствуют логической единицы.

Задержка передачи для типичного элемента ДТЛ составляет 30 нс. Это сравнительно большая величена, во многих случаях оказывается вполне приемлемой.

Семейство диодно-транзисторной логики содержит элементы И, ИЛИ, НЕ-И, НЕ-ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ. Это семейство удобно для конструктора, так как имеет большой набор различных элементов. Большинство схем содержит несколько незадействованных входных клемм, которые рекомендуется соединять с положительным полюсом источника питания или заземлять. Это увеличивает помехозащищенность и уменьшает время задержки передачи.

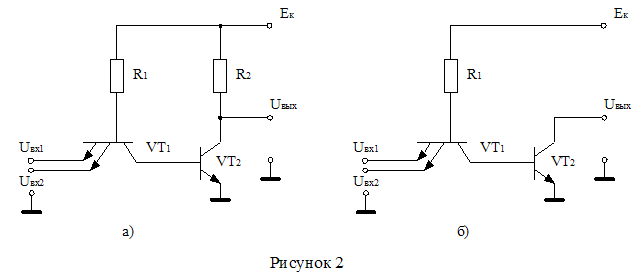

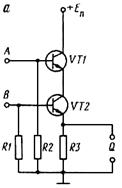

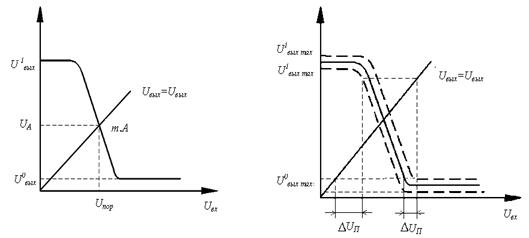

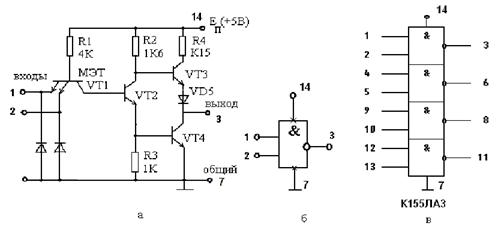

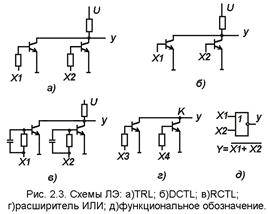

Транзисторно-транзисторные логические элементыПростейший базовый элемент ТТЛ, в соответствии с рисунком 2а, за счет использования многоэмиттерного транзистора, объединяющего свойства диода и транзисторного усилителя, позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы.

Базовый элемент ТТЛ также выполняет логическую операцию И-НЕ. При низком уровне сигнала (логический 0) хотя бы на одном из выходов многоэмиттерного транзистора VT1 последний находится в состоянии насыщения, а VT2 закрыт. На выходе схемы существует высокий уровень напряжения (логическая единица). При высоком уровне сигнала на всех входах VT1 работает в активном инверсном режиме, а VT2 находится в состоянии насыщения. Описанный здесь базовые элемент ТТЛ, несмотря на прощеную технологию изготовления, не нашел широкого применения из-за низкой помехоустойчивости, малой нагрузочной способностью и малого быстродействия при работе на емкостную нагрузку. Его целесообразно использовать лишь при разработке микросхем с открытым коллектором, в соответствии с рисунком 2б, для включения внешних элементов индикации, когда не требуется высокая помехоустойчивость и большая нагрузочная способность.

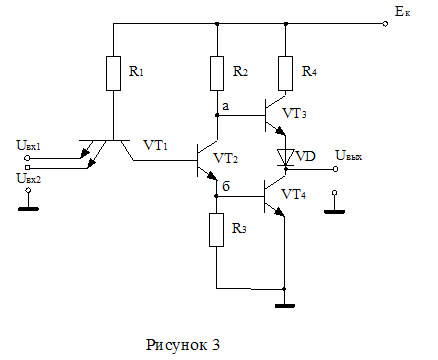

Улучшенными параметрами по сравнения с предыдущей схемой обладает базовый элемент ТТЛ, в соответствии с рисунком 3. Однако объединение выходов в схеме не допустимо.

Улучшенными параметрами по сравнения с предыдущей схемой обладает базовый элемент ТТЛ, в соответствии с рисунком 3. Однако объединение выходов в схеме не допустимо.

В статических режимах работы схемы, в соответствии с рисунком 3, VT4 повторяет состояние VT2. При запирании VT2 база транзистора VT4 через резистор R3 подключается к “земле”, чем и обеспечивается закрытое состояние VT4.

Если VT2 насыщен, то через базуVT4 протекает ток:

Iб4 = Iэ2 – IR3 = [(Eк - Uкэн2 – Uбэ4)/a2·R2] – (Uбэ4/R3)

Для транзисторов, выполненных по интегральной технологии, обычно принимают Uкэн = 0,2 В, Uбэ = 0,8 В.

Для обеспечения режима насыщения VT4 при закрытых транзисторе VT3 и диоде VD необходимо выполнить условие:

Iб4·В4 ≥ Iкн = n·I0вх нагр

Где: n – число нагрузочных ТТЛ-схем, подключенных к выходу рассматриваемой схемы;

I0вх нагр – входной ток нагрузочной ТТЛ-схемы.

Положив в данное выражение знак равенства, можно определить нагрузочную способность данной схемы, т.е. максимальное число нагрузочных схем, при котором транзистор VT4 еще работает в режиме насыщения:

nmaz = Iб4·В4 / I0вх нагр

Состояние VT3 в статических режимах работы схемы, в соответствии с рисунком 3, всегда противоположно состояниюVT4, а следовательно, VT2. При насыщенном VT4 транзистор VT3 закрыт. Диод VD повышает порог отпирания VT3, обеспечивая его закрытое состояние при насыщенном транзисторе VT4. Действительно:

Uбэ3 = Uкэн2 + Uбэ4 – Uкэн4 – Uд ≈ Uбэ4 - Uд < Uпор3

Так как типичны значения: Uбэ4 = 0,8 В; Uд = 0,7В; Uпор = 0,6В.

Помехоустойчивость ТТЛ-схем по высокому и низкому уровням входного напряжения различны, т.е. U0пом ≠ U1пом.

ТТЛ-схема более чувствительна к помехе U0пом, которая накладывается на сигнал U0вх и вызывает ложное переключение схемы (U0пом < U1пом). Схема, в соответствии с рисунком 3, считается подключенной, если под действием помехи U0пом открываются транзисторы VT2 и VT4, для отпирания которых требуется двойное пороговое напряжение Uпор2 +Uпор4 ≈ 2·Uпор. Тогда условие сохранения первоначального состояния схемы при действии помехи можно записать как:

U0вх + U0пом + Uкэн1 ≤ 2Uпор

Откуда найдем:

U0пом ≤ 2Uпор - U0вх - Uкэн1

Приняв U0вх = 0,2 В; Uпор = 0,6 В; Uкэн = 0,2 В, получим U0пом ≤ 0,6 В

При определении U1пом схема считаются переключенной, если открывается закрытый переход база – эмиттер многоэмиттерного транзистора VT1. В режиме логическое единицы на входе потенциал базы транзистора VT1 относительно “земли” равен сумме напряжений на открытых переходах база-коллектор VT1 и база-эмиттер VT2 и VT4, т.е. Uб1 = Uбк1 + Uбэ2 + Uбэ4 = 2,14 В. Тогда напряжение на закрытом переходе база-эмиттер VT1: Uбэ1 = Uб1 – U1вх. Принимая U1вх = 3,6 В, будем иметь Uбэ1 = -1,2 В.

Напряжение помехи, при котором транзистор VT1 можно считать открытым, U1пом = Uбэ1 – Uпор = -1,2 –0,6 = -1,8 В.

Помехоустойчивость ТТЛ-схемы со сложным инвертором по логическому нулю выше, а по логической единице, чем ТТЛ-схемы, в соответствии с рисунком 2а.

Быстродействие ТТЛ-схем определяется в основном переходными процессами при переключении транзисторов, а также зарядом паразитной нагрузочной емкости Сн, которая представляет собой суммарную емкость нагрузочных ТТЛ-схем. В схеме, в соответствии с рисунком 2а, заряд емкости Сн происходит с большой постоянной времени через коллекторный резистор R2, что ухудшает быстродействие схемы.

В ТТЛ-схеме со сложным инвертором постоянная заряда нагрузочной емкости существенно уменьшается, так как емкость Сн заряжается через выходное сопротивление Rвых 3 << R2 транзистора VT3, работающего в схеме эмиттерного повторителя. За счет этого ТТЛ-схема со сложным инвертором имеет большее быстродействие по сравнению с ТТЛ-схемой, в соответствии с рисунком 2а.

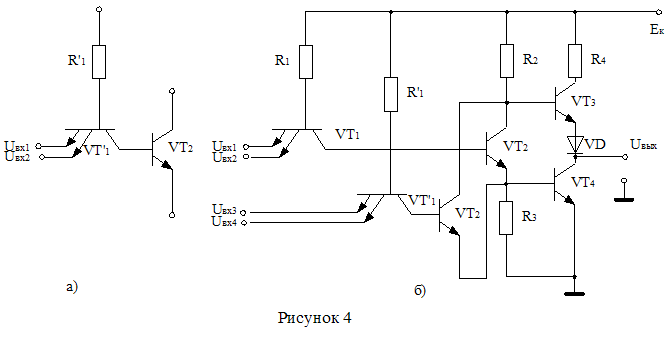

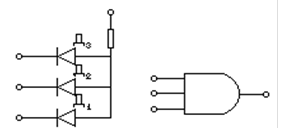

Схема базового элемента со сложным инвертором лежит в основе разработок большинства серий интегральных микросхем ТТЛ. Для расширения функциональных возможностей элемента промышленностью выпускают так называемые расширители по ИЛИ, в соответствии с рисунком 4а, которые представляют собой часть структуры ТТЛ и подключаются к точкам а и б элемента, в соответствии с рисунком 2. Полученная при этом логическая схема, в соответствии с рисунком 4б, реализует функцию И-ИЛИ-НЕ. На выходе схемы устанавливается логический нуль, если на всех выходах VT1 поступают сигналы, соответствующие логической единице. При всех остальных комбинациях сигналов на выходах схемы выходное напряжение соответствует логической единице.

Повысить быстродействие ТТЛ-схем можно, применив в схеме базового элемента, в соответствии с рисунком 3, вместо обычных транзисторов транзисторы Шотки, работающие в активном режиме. Тем самым сокращается время переключения транзисторов схемы за счет исключения времени рассасывания носителей заряда в базе транзистора при их запирании. Логические ИМС, выполненные на базе транзисторов Шотки, называются микросхемами ТТЛШ.

Недостатком ТТЛ-схем является сильная генерация токовых помех по цепи питания, обусловленных броском тока через сложный инвертор при переключении схемы из состояния логического нуля в единицу. После запирания VT2 транзистор VT3 откроется раньше, чем закроется насыщенный транзистор VT4, так как для выхода VT4 из режима насыщения потребуется некоторое время для рассасывания неосновных носителей в базе. В результате в течении некоторого промежутка времени оба транзистора VT3 и VT4 открыты и по цепи, состоящей из элементов Ек, VT3, VD и VT4, протекает ток, значение которого определяется эмитторным током VT3, находящегося в активном режиме:

Iпом max = Iэ3 = Iб3 · В + Iб3 = Iб3 (В+1)

Так как базовый ток транзистор равен:

![]()

То:

Iпом max =

Iпом max = ![]()

Для устранения влияния токовых помех, генерируемых данной микросхемой, на работу соседних микросхем рекомендуется включать высокочастотные блокировочные конденсаторы между шиной питания и землей.

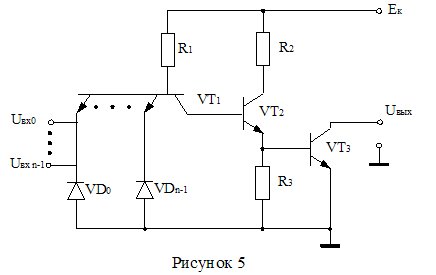

Элемент И – НЕ с открытым коллектором предназначен для согласования логических схем с внешними исполнительными и индикаторными устройствами, например светодиодными индикаторами, лампочки накаливания, обмотки реле и т.д. Его отличие от ранее рассмотренного заключается в выполнении выходного усилителя мощности по однотактной схеме без собственного резистора. Принципиальная электрическая схема такого элемента приведена в соответствии с рисунком 5.

В данном элементе также отсутствует цепь нелинейной коррекции. Это связано с тем, что элемент ставится на выходе логического устройства и к нему в меньшей степени предъявляются требования квантования сигнала. Обычно выходной транзистор VT3 схемы выполняется с большими допустимыми значениями коллекторного тока и напряжением, чем обычный элемент.

В отличии от стандартных, элементы ТТЛ с открытым коллектором допускают параллельное включение выходных выводов. При этом относительно выходных сигналов каждого элемента реализуется логическая операция И: Uвых = Uвых 1Uвых 2 ... Uвых n

Это позволяет решить две задачи:

Похожие работы

... 7. Логический элемент НЕ, выполненный на обычном биполярном транзисторе (а); многоэмиттерном транзисторе с дополнительным усилителем (б); Транзистор Шоттки и его условное графическое изображение в электронных схемах (в). Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б). Логический элемент И – ...

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

... первой логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения числа компонентов ЛЭ и роста площади кристалла ИМС. В существующих сериях интегральных микросхем основные логические элементы выполняются, как правило, с небольшим числом входов . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение ...

... V ~“ должна находиться в нажатом, а кнопка “ВСВ ВНК” в поле надписи “КВУ” - в отжатом состоянии. 4. Методические рекомендации к выполнению работы 4.1. Исследование особенностей функционирования логических элементов ДД1 ¸ ДД4 и определение их функционального назначения. 4.1.1. Задавая различные комбинации входных логических сигналов, определить значение выходного сигнала и по результатам ...

0 комментариев