Навигация

Методика исследования элементной базы ЭСППЗУ

4.1.1 Методика исследования элементной базы ЭСППЗУ

Физика работы запоминающего элемента ЭСППЗУ требует подачи на нее довольно высоких уровней напряжения при записи информации. Что накладывает ряд специфических требований на элементную базу как самой запоминающей ячейки, так и кристалла микросхемы целиком.

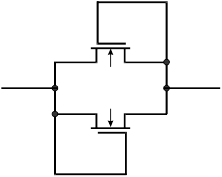

Напряжение поступающее на запоминающую ячейку в режиме программирования составляет ~ 15 ¸ 20 В и формируется встроенным на кристалле источником и подается к ячейке посредством цепочки коммутирующих п-канальных транзисторов. Типовая схема передачи напряжения от источника к запоминающей ячейке приведена на рисунке 11.

Необходимость использования для передачи напряжения программирования п-канальных транзисторов определяет потери в его величине на выводах ячейки относительно напряжения источника.

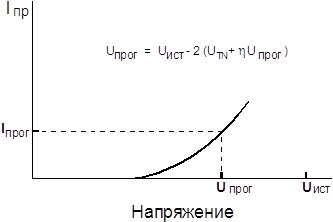

Напряжение Uпрог. поступающее на запоминающую ячейку определяется следующим образом:

Uпрог = Uист – 2 (UTN + h Uпрог) (22),

где: UTN - порог п-канального транзистора (без смещения подложки);

h - коэффициент влияния подложки;

Uист- напряжение источника вырабатывающего высокое напряжение на кристалле.

Максимально достижимое значение напряжения источника ограничивается пробивными и пороговыми напряжениями его элементов. Достижение режима работы запоминающей ячейки при записи информации с учетом соотношения емкостей управляющего и туннельного окисла иллюстрируется на рисунке 12

Схема передачи

Рисунок 11

Рабочий режим запоминающей ячейки

Рисунок 12

Основными характеристиками, которые определяют работоспособность и надежность ячейки, являются соотношение емкостей между обкладками транзистора с “плавающим” затвором (параметр отвечает за величину напряжения на “плавающем” затворе при программировании) и разность токов при чтении информации различных состояний ячейки.

Для эффективного программирования соотношение ёмкостей должно быть ³ 1,0. При соотношении 1,0 к туннельному окислу в режиме программирования прилагается напряжение, равное половине “высокого”, что достаточно для протекания туннельного тока при dox = 80 – 85 A. У анализируемого образца данное соотношение равно 1,1.

Ток ячейки, при прочих равных условиях, определяется эффективной шириной адресного и “плавающего” транзисторов и, безусловно, уровнем заряда, записанного на “плавающем” затворе.

Для элементной базы ЭСППЗУ в отличие от стандартных КМОП ИС очень важными параметрами элементной базы являются:

1. Значения и разброс пороговых напряжений рабочих транзисторов.

2. Пробивные напряжения элементов, с помощью которых формируется и подается к запоминающей ячейке программирующее напряжение.

3. Пороговые напряжения паразитных структур, прилегающих к элементам обеспечивающим формирование Uпрог.

4. Тип подложки и собственная структура транзисторов, определяющие коэффициент влияния напряжения смещения истока относительно напряжения подложки на пороговое напряжение ключевых транзисторов, осуществляющих передачу программирующего напряжения к выбранному запоминающему элементу.

5. Емкости туннельного и межслойного (между управляющим и плавающим затвором) окислов.

4.2 Результаты исследования элементной базы

Учитывая приведенные выше требования, были отобраны тестовые структуры, на которых проводились комплексные измерения параметров элементной базы ЭСППЗУ.

4.2.1 Исследование характеристик туннельного окисла запоминающего элемента

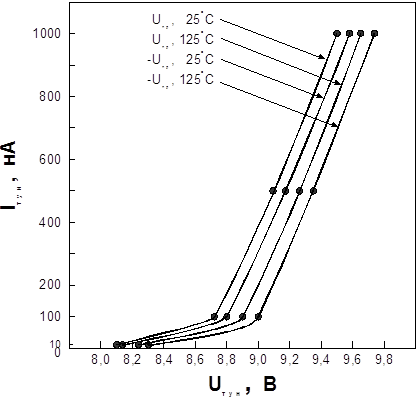

Вольтамперные характеристики туннельного окисла снимались непосредственно на структуре, входящей в состав запоминающей ячейки. Измерения проводились для напряжения обоих полярностей при температуре +20, +85 и +125°С.

Результаты измерений (представлены в форме графиков в приложении 2) были подвергнуты компьютерной математической обработке и приведены на рисунке 13.

Полученные результаты показывают симметричность вольт-амперной характеристики туннельного окисла при разной полярности приложенного напряжения и слабую зависимость от температуры, что подтверждается научными литературными источниками. Для упрощения рисунке 14, на нем не приведены кривые, полученные при температуре +85оС.

4.2.2 Эквивалентная схема замещения туннельного окисла

Важным этапом разработки микросхем ЭСППЗУ является моделирование электрической схемы. В настоящее время полное моделирование затруднено в связи с отсутствием модели запоминающей ячейки. Основным препятствием к ее созданию является отсутствие схемы замещения туннельного окисла в составе библиотек программных пакетов систем проектирования.

Однако на элементах библиотек этих систем возможно создание схем, которые позволят обеспечить электрические характеристики имитирующие поведение туннельного окисла в составе запоминающей ячейки и запоминающая ячейка в целом в режимах записи и чтения информации.

Вольтамперные характеристики туннельного окисла

Рисунок 13

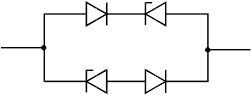

Нами предложено три варианта эквивалентной схемы замещения туннельного окисла. Туннельный окисел может быть замещен двумя встречно включенными МОП транзисторами (рисунок 14), системой диодов и стабилитронов (рисунок 15) или двумя встречно включенными источниками тока управляемыми напряжением (рисунок 16)

В данном дипломном проекте будет рассмотрена схема замещения на источниках тока управляемых напряжением.

Рисунок 14

Рисунок 15

|

Рисунок 16

0 комментариев