Навигация

Построение и расчет ячейки ЭСППЗУ

4.2.3 Построение и расчет ячейки ЭСППЗУ

Модель ячейки представлена на рисунке 16. Ее моделирование проводилось со всеми предложенными выше схемами замещения. Однако в силу сложности обеспечения параметров туннельного окисла с помощью систем параметров элементов входящих в состав этих схем замещения была найдена еще одна. В основе этой схемы замещения лежит источник тока управляемый напряжением. Причем схема состоит из двух таких источников, включенных параллельно, но с разными направлениями токов. Такое включение позволяет заменить туннельный окисел при обеих полярностях напряжения в режимах стирания и записи информации. Замещение туннельного окисла, таким образом, позволяет точно описать токовую характеристику и исключить влияние каких-либо других параметров из системы параметров других схем замещения, таких как емкость, сложность обеспечения требуемого порогового напряжения и т.д.

Результаты построения токовой характеристики источников замещающих туннельный окисел в модели, в сравнении с измеренными на образцах, приведены на рисунке 17. Как видно из рисунка обе характеристики совпадают с высокой точностью.

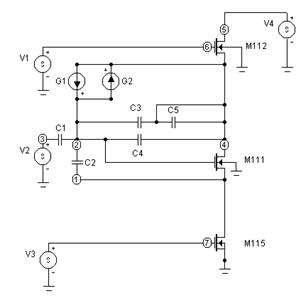

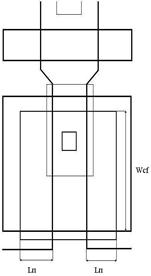

Разработанная модель представлена на рисунке 18, а на рисунке 19 представлены SPICE-параметры этой модели. В этой схеме два источника тока управляемых напряжением G1 и G2 моделируют параметры туннельного окисла, транзистор М112 является транзистором выборки, а транзистор М111 активным транзистором-транзистором с плавающим затвором. Емкость С1 между плавающим и управляющим затворами представленная на рисунке 20 и рассчитывается по формуле(22), емкость C14 рассчитывается по формуле (23) и представлена на рисунке 21

C15=(e * e0 * Wcf* Lf)/d1 (23)

C14=(e * e0 * Wcf* 2Lперекр)/d1 (24)

Где Wcf–это ширина области перекрытия. Lf и Lперекр - длина области перекрытия, а d1 –это толщина диэлектрика между затворами.

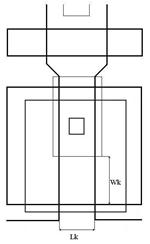

Емкость C17, показанная на рисунке 22 рассчитывается по формуле (24) и учитывается в расчете внутренних емкостей транзистора М111. Активная емкость нырка без учета емкости туннельного окисла рассчитывается по формуле (25) и показана на рисунке 23.

C17=(e * e0 * Wк * Lк)/d1 (25)

C16=(e * e0 * Wк * Lн)/d1 (26)

Где Wк ширина канала, а Lк и Lн длина канала и нырка соответственно.

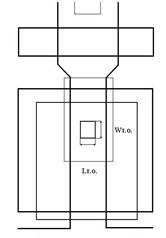

Фактическая же емкость туннельного окисла показана на рисунке 24 и рассчитывается по формуле (26).

C18=(e * e0 * Wт.о. * Lт.о.)/d1 (27)

Где Wт.о. и Lт.о ширина и длина туннельного окисла соответственно

Рисунок 17

Рисунок 18

C14 1 2 0.005P

C15 2 3 0.3P

C16 4 2 0.04P

C17 4 4 .1P

C18 4 2 0.005P

G5 4 2 TABLE {V(4,2)} =

+(0,0)(1,0)(2,0)(3,0)(4,0)(5,0)(6,0)(7,0)(8,10N)(8.5,50N)(9,200N)(9.5,600N)(9.8

+ ,1000N)(20,13U)(25,19U)

G6 2 4 TABLE {V(2,4)} =

+(0,0)(1,0)(2,0)(3,0)(4,0)(5,0)(6,0)(7,0)(8,10N)(8.5,50N)(9,200N)(9.5,600N)(9.8

+ ,1000N)(20,13U)(25,19U)

M111 4 2 1 0 12MSC L=2U W=3U

M112 5 6 4 0 12MSC L=4U W=5U

M115 1 7 0 0 12MSC L=1.4U W=6U

RG5 4 2 1G;added by G5

RG6 2 4 1G;added by G6

V1 6 0 PWL 0M 0 1M 5 9M 5 11M 5 19M 5 21M 15 29M 15 31M 5 40M 5

V2 3 0 PWL 0M 0 1M 14 9M 14 11M 0 19M 10 21M 0 29M 0 31M 0 {40M -10}

V3 7 0 PWL 0M 0 9M 0 11M 5 19M 5 21M 0 29M 0 31M 5 40M 5

V4 5 0 PWL 0M 0 9M 0 11M 5 19M 5 21M 15 29M 15 31M 5 40M 5

**** sram32k*8

.MODEL 12MSC NMOS (LEVEL=3 VTO=650M L=1.4U W=50U GAMMA=350M LAMBDA=20M RD=30

+ RS=30 IS=0 PB=750M CGSO=200P CGDO=200P CJ=360U CJSW=350P MJSW=250M TOX=25N

+ NSUB=4.000000E+016 TPG=1 XJ=350N LD=220N WD=200N UO=550 VMAX=150K DELTA=3.7

+ THETA=35M ETA=15M KAPPA=700M T_MEASURED=27)

*.OPTIONS ACCT LIST OPTS ABSTOL=1UA CHGTOL=.01pC CPTIME=1G DEFL=100u DEFW=100u

+ DIGDRVF=2 DIGDRVZ=20K DIGERRDEFAULT=20 DIGERRLIMIT=10000 DIGFREQ=10GHz

+ DIGINITSTATE=0 DIGIOLVL=2 DIGMNTYMX=2 DIGMNTYSCALE=0.4 DIGOVRDRV=3

+ DIGTYMXSCALE=1.6 GMIN=1p ITL1=100 ITL2=50 ITL4=10 ITL5=0 LIMPTS=0 PIVREL=1m

+ PIVTOL=.1p RELTOL=1m TNOM=27 TRTOL=7 VNTOL=1u WIDTH=80

.END

Рисунок 19

Рисунок 20

Рисунок 21

Рисунок 22

Рисунок 23

Рисунок 24

Для оценки возможностей модели ячейки разработана схема для расчета ее характеристик. Сигналы, обеспечивающие работу ячейки в составе ЭСППЗУ, имитируются источниками V1…V3.

Временная диаграмма построена таким образом, что сначала осуществляется стирание информации, а потом чтение – определение порогового напряжения после стирания информации, запись информации и опять чтение. При этом, изменяя амплитуды и длительность сигналов источников V1…V3 можно оценить все необходимые параметры ячейки ЭСППЗУ в реальных режимах работы устройства и определить пороговые напряжения, токи считывания информации для определения необходимого порогового напряжения на управляющем затворе для обеспечения устойчивого напряжения во всем диапазоне питающих напряжений. Модель позволяет оптимизировать соотношения геометрических размеров элементов ячейки и минимизировать ее площадь по заданным параметрам технологической структуры элементов.

Пример расчета приведен на рисунке 25, результаты же расчета в сравнении с измеренными параметрами приведены на таблице 1. Данные приведены для длительности времени программирования 1ms.

Как видно из таблицы 1 результаты лежат достаточно близко к измеренным. За тестовую ячейку преднамеренно выбирается запоминающая ячейка экспериментальных образцов микросхем, оптимизация конструкции которых проводится на основе экспериментальных данных и занимает значительный отрезок времени и требует больших финансовых затрат.

Сравнительный анализ полученных и экспериментальных результатов показывает, что ячейка требует оптимизации, т.к. при задании уровня напряжения на управляющем затворе равного 1,5 В пороговое напряжение активного транзистора с плавающим затвором превышает его только при Uпрогр³14 В.

Для принятой технологической структуры это значение напряжения программирования является граничным, т.е. область работоспособности микросхемы будет ограниченной особенно в области низких значений питающих напряжений, что подтверждается результатами измерения образцов кристаллов микросхем ЭСППЗУ.

Для улучшения ситуации необходимо либо увеличить Uпрогр , либо изменить соотношение емкостей управляющего и плавающего затворов в сторону увеличения емкости управляющего затвора, либо изменить конструкцию и схемотехнику узлов интегральной схемы с целью снижения напряжения на управляющем затворе в режиме чтения.

Таблица 4.1

| ПРОГРАММИРОВАНИЕ | ||||||||||||||||||||

| Uпрогр=12 В tпрогр=1 mS | Uпрогр=13 В tпрогр=1 mS | Uпрогр=14В tпрогр=1 mS | Uпрогр=15 tпрогр=1 mS | Uпрогр=16В tпрогр=1 mS | ||||||||||||||||

| Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=Uз, Uи=0,Uп=0В | ||||||||||||||||

| Экпери-мент | Моделиро-вание | Экпери-мент | Моделиро-вание | Экпери-мент | Моделиро-вание | Экпери-мент | Моделиро-вание | Экпери-мент | Моделиро-вание | |||||||||||

| 0,10 | 0,21 | 0,60 | 0,49 | 1,30 | 1,41 | 1,90 | 2,08 | 2,60 | 2,73 | |||||||||||

| 0,02 | 0,032 | 0,60 | 0,51 | 1,25 | 1,34 | 1,90 | 2,03 | 2,60 | 2,71 | |||||||||||

| 0,12 | 0,23 | 0,60 | 0,71 | 1,25 | 1,35 | 1,90 | 2,05 | 2,60 | 2,70 | |||||||||||

| 0,00 | 0,05 | 0,25 | 0,35 | 0,75 | 0,80 | 1,50 | 1,63 | 2,00 | 2,11 | |||||||||||

| 0,00 | 0,031 | 0,24 | 0,33 | 1,15 | 1,28 | 1,60 | 1,71 | 2,15 | 2,23 | |||||||||||

| 0,00 | 0,04 | 0,30 | 0,41 | 1,10 | 1,22 | 1,30 | 1,41 | 2,20 | 2,30 | |||||||||||

| 0,25 | 0,31 | 0,95 | 1,00 | 1,60 | 1,72 | 2,20 | 2,29 | 2,90 | 3,00 | |||||||||||

| 0,25 | 0,33 | 0,95 | 1,07 | 1,60 | 1,71 | 2,20 | 2,31 | 2,80 | 2,93 | |||||||||||

| 0,25 | 0,35 | 1,05 | 1,16 | 1,50 | 1,63 | 2,40 | 2,52 | 2,90 | 3,01 | |||||||||||

| СТИРАНИЕ | ||||||||||||||||||||

| Uстир=12 В tстир=1 mS | Uстир=13 В tстир=1 mS | Uстир=14В tстир=1 mS | Uстир=15 tстир=1 mS | Uстир=16В tстир=1 mS | ||||||||||||||||

| Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В | Uпор,В Iст=0.1 мкА, Uс=2В, Uи=0,Uп=0В | ||||||||||||||||

| Экпери-мент | Модели-рование | Экпери-мент | Модели-рование | Экпери-мент | Модели-рование | Экпери-мент | Модели-рование | Экпери-мент | Модели-рование | |||||||||||

| +0,85 | +0,9 | +1,24 | +1,3 | -1,50 | -1,4 | -2,14 | -2,03 | -3,50 | -3,41 | |||||||||||

| +0,95 | +1,0 | +0,32 | +40,41 | -1,54 | -1,49 | -2,40 | -2,34 | -3,42 | -3,31 | |||||||||||

| +1 | +1,1 | +0,4 | +0,49 | -1,40 | -1,3 | -2,70 | -2,61 | -4,00 | -3,91 | |||||||||||

| +1,1 | +1,22 | +0,4 | +0,51 | -1,37 | -1,25 | -2,32 | -2,25 | -3,30 | -3,19 | |||||||||||

| +1,1 | +1,25 | +0,4 | +0,53 | -1,28 | -1,19 | -2,30 | -2,21 | -3,34 | -3,25 | |||||||||||

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

1. Статьи из IEEE JOURNAL OF SOLID-STATE CIRCUITS:

2. “A 16kbit EEPROM Using n-Channel Si-Gate MOS Technology” June1980, number 3, vol. sc-15; TAYAAKI HAGIWARA, YUJI YANSUDA, RYUJI KONDO, SHIN-ICHI MINAMI, TOSHIRO AOTO, and YOKICHI ITOH.

3. “ A 16kbit EEPROM Employing New Array Architecture and Designed-In Reliability Features” October1982, number 5, vol. sc-17; GIORA YARON, S. JAYASIMHA PRASAD, MARK S. EBEL, and BRUCE M. K. LEONG.

4. “ A 128kbit Flash EEPROM Using Double-Polysilicon Technology” October1987, number 5, vol. sc-22; GHEORGHE SAMASHISA, CHIEN-SHENG SU, YU SHENG KAO, GEORGE SMARANDOIU, CHENG-YUAN MICHAEL WANG, TINGWONG, CHENMING HU.

5. “A 50-ns CMOS 256K EEPROM ” October 1988 number 5 vol.23; TAH-KANG J.TING, THOMAS CHANG,TIEN LIN,CHING S. JENQ,KENNETH L. C. NAIFF.

6. “An 80ns 32K EEPROM Using the FETMOS Cell”October1982 number 5, vol. sc-17 ;CLINTON KUO,JOHN R. YEARGAIN,WILLIAM J. DOWNEY,KERRY A.ILGENSTEIN,JEFFREY R.JORVIG,STEPHEN L.SMITH,ALAN R. BORMANN.

7. “An Enhanced 16K EEPROM” October 1982 number 5 vol.sc-17; LUBIN GEE, PEARL CHENG, YOGENDRA BOBRA,RUSTAM MENTA.

8. “A 5-V-ONLY one-Transistor 256K EEPRON with Rage-Mode Erase” August 1989 number 4 vol.24; TAKESHI NAKAYAMA, YOSHIKAZU MIYAWAKI, KAZUO KOBAYASHI, YASUSHI TERADA, HIDEAKI ARIMA,TAKAYUKI, MATSUKAWA,TSUTOMU YOSHIHARA.

9. “An Experimental 4-Mbit CMOS EEPROM with a NAND-structured Cell” October 1989 number 5 vol.24;MASAKI MOMODOMI,YASUO ITOH,RIICHIRO SHIROTA,YOSHIHISA IWATA,RYOZO MAKAYAMA,RYOUHEI KIRISAWA,TOMOHARU TANAKA,SEIICHI ARITOME,TETSUO ENDOH,KAZUNORI OHUCHI,FUJIO MASUOKA.

10. “120-ns 128K /8bit/64K/16bit CMOS EEPROM’S” October 1989 number 5 vol.24;YASUSHI TERADA, KAZUO KOBAYASHI,TAKESHI NAKAYAMA,MASANORI HAYASAIKOSHI,YOSHIKAZU MIYAWAKI,NATSUO AJIKA, HIDEAKI ARIMA,TAKAYUKI MATSUKAWA,TSUTOMU YOSHIHARA.

11. “Yield and Reliability of MNOS EEPROM Products” December 1989 number 6 vol.24 ; YOSHIAKI KAMIGAKI,CHIN-ICHI MINAMI,TAKAAKI HAGIWARA,KAZUNORI FURUSAWA,TAKESHI FUURUNO,KEN UCHIDA,MASAAKI TERASAWA,KOUBU YAMAZAKI.

12. “A High-Density NAND EEPROM with Block-Page Programming for Microcomputer Applications” April 1990number 2 vol.25 ;YOSHIHISA IWATA,MASAKI MOMODOMI,TOMOHARU TANAKA,HIDEKO OODAIRA,YASUO ITOH,RYOZO NAKAYAMA,RYOUHEI KIRISAWA,SEIICHI ARITOME,TETSUO ENDOH, RIICHIRO SHIROTA,KAZUNORI OHUCHI,FUJO MASUOKA.

13. “A 60-ns 16Mb Flash EEPROM with Program and Erase Sequence Controller” November 1991 number 11 vol.26;TAKESHI NAKAYAMA,SHIN-ICHI KOBAYASHI,YOSHIKAZU MIYAWAKI,YASUSHI TERADA,NATSUO AJIKA,MAKOTO OHI,HIDEAKI ARIMA,TAKAYUKI MATSUKAWA,TSUTOMU YOSHIHARA,KIMIO SUZUKI.

14. “A Dual-Mode Sensing Scheme of Capacitor-coupled EEPROM Cell” April 1992 number 4 vol.27; MASANORI HAYASUIKOSHI ,HIDETO HIDAKA,KAZUTAMI ARIMOTO, KAZUYASU FUJISHIMA.

15. “A 512-kb Flash EEPROM Embedded in a 32-b Microcontroller” April 1992 number 4 vol.24; CLINTON KUO,MARK WEIDNER,THOMAS TOMS,HENRY CHOE,KO-MIN CHANG,ANN HARWOOD,JOSEPH JELEMENSKY,PHILIP SMITH.

16. “A 5-v-Only Operation0.6 mm Flash EEPROM with Row Decoder Scheme in Triple-Well Structure” November 1998 number 11 vol.27; AKIRA UMEZAWA ,SHIGERU ATSUMI,MASAO KURIYAMA,HIRONORI BANDA,KEN-ICHI IMAMIYA,KIYOMI NARUKE,SEIJI YAMADA,ETSUSHI OBI,MASAMITSU OSHIKIRI,TOMOKO SUZUKI,SUMIO TANAKA.

17. “High-Voltage Regulation and Process Consideration for High-Density 5V-Only EEPROM’S ”October 1983 number 5 vol. sc-18; DUANE H . OTO,VINOD K. DHAM, KEITH H. GUDGER,MICHAEL J. REITSMA, GEOFFREY S. GONGWER,YAW WEN HU,JAY F. OLUND,H.STANLEY JONES,SIDNEY T. K. NIEH.

18. “A 16 kbit Smart 5V-Only EEPROM with Redundancy”. October 1983 number 5 vol.sc-18;ELROY M. LUCERO,NAGESH CHALLA ,JULIAN FIELDS,JR.

19. “A 35-ns 64K EEPROM” October 1985 number 5 vol.sc-20;CAMPBELL,DAVID L. TENNANT ,JAY F.OLUND,ROBERT B. LEFFERTS,BRENDAN T. CREMEN,PHILIP A. ANDREWS.

20. “A Temperature-and Process Tolerant 64K EEPROM .”October 1985 number 5 vol.sc-20;COLIN S.BILL,PAUL I. SUCIU, MICHAEL S. BRINER, DARRELL D. RINERSON.

21. “An Experimental 5-V-Only 256-kbit CMOS EEPROM with a High-Performance Single-Polysilicon Cell”. October 1986 number 5 vol.sc-21; JUN-ICHI MIYAMOTO, JUN-ICHI TSUJI-MOTO,NAOHIRO MATSUKAWA,SHIGERU MORITA,KAZUYOSI SHINADA,HIROSHI NOZAWA,TETSUA IIZUKA.

22. “A Four-state EEPROM using Floating-Gate Memory Cells ”June 1987 number 3 vol.sc-22; CHRISTOPH BLEIKER, HANS MELCHIOR.77

0 комментариев