Навигация

2.7.2 Мультипроцессоры

Элементы массивно-параллельного процессора связаны между собой, поскольку их работу контролирует один блок управления. Система нескольких параллельных процессоров, разделяющих общую память, называется мультипроцессором. Поскольку каждый процессор может записывать или считывать информацию из любой части памяти, их работа должна согласовываться программным обеспечением, чтобы не допустить каких-либо пересечений.

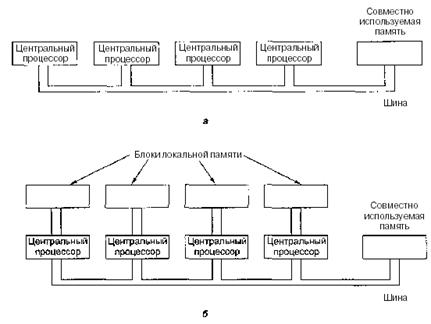

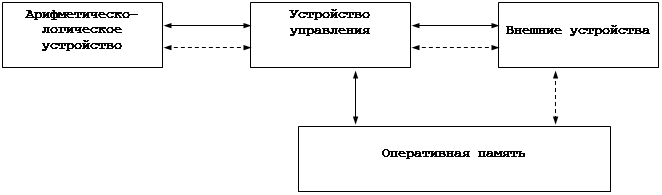

Возможны разные способы воплощения этой идеи. Самый простой из них — наличие одной шины, соединяющей несколько процессоров и одну общую память. Схема такого мультипроцессора показана на рис. 2.7а. Такие системы производят многие компании.

Нетрудно понять, что при наличии большого числа быстро работающих процессоров, которые постоянно пытаются получить доступ к памяти через одну и ту же шину, будут возникать конфликты. Чтобы разрешить эту проблему и повысить производительность компьютера, были разработаны различные модели. Одна из них изображена на рис. 2.7б. В таком компьютере каждый процессор имеет свою собственную локальную память, которая недоступна для других процессоров. Эта память используется для программ и данных, которые не нужно разделять между несколькими процессорами. При доступе к локальной памяти главная шина не используется, и, таким образом, поток информации в этой шине снижается. Возможны и другие варианты решения проблемы (например, кэш-память).

Рис. 2.7. Мультипроцессор с одной шиной и одной общей памятью (а); мультипроцессор,в котором для каждого процессора имеется собственная локальная память (б)

Мультипроцессоры имеют преимущество перед другими видами параллельных компьютеров, поскольку с единой разделенной памятью очень легко работать. Например, представим, что программа ищет раковые клетки на сделанном через микроскоп снимке ткани. Фотография в цифровом виде может храниться в общей памяти, при этом каждый процессор обследует какую-нибудь определенную область фотографии. Поскольку каждый процессор имеет доступ к общей памяти, обследование клетки, которая начинается в одной области и продолжается в другой, не представляет трудностей.

2.7.3 Мультикомпьютеры

Мультипроцессоры с небольшим числом процессоров (< 64) сконструировать довольно легко, а вот создание больших мультипроцессоров представляет некоторые трудности. Сложность заключается в том, чтобы связать все процессоры с памятью. Чтобы избежать таких проблем, многие разработчики просто отказались от идеи разделенной памяти и стали создавать системы, состоящие из большого числа взаимосвязанных компьютеров, у каждого из которых имеется своя собственная память, а общей памяти нет. Такие системы называются мультикомпьютерами.

Процессоры мультикомпьютера отправляют друг другу послания (это несколько похоже на электронную почту, но гораздо быстрее). Каждый компьютер не обязательно связывать со всеми другими, поэтому обычно в качестве топологий используются 2D, 3D, деревья и кольца. Чтобы послания могли дойти до места назначения, они должны проходить через один или несколько промежуточных компьютеров. Тем не менее время передачи занимает всего несколько микросекунд. Сейчас создаются и запускаются в работу мультикомпьютеры, содержащие около 10 000 процессоров.

Поскольку мультипроцессоры легче программировать, а мультикомпьютеры — конструировать, появилась идея создания гибридных систем, которые сочетают в себе преимущества обоих видов машин. Такие компьютеры представляют иллюзию разделенной памяти, при этом в действительности она не конструируется и не требует особых денежных затрат.

3 ЭВОЛЮЦИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ 3.1 Основные направления развития Несмотря на то, что сегодня известно множество способов повышения производительности микропроцессоров с суперскалярной архитектурой, имеется также ряд препятствий и ограничений, исключающих возможность дальнейшего наращивания быстродействия. В данной главе показаны способы повышения производительности суперскалярных микропроцессоров на примере архитектур Alpha 21364 и Power4. Разбираются вопросы перехода к принципиально новой, так называемой мультитредовой архитектуре, позволяющей существенно изменить возможности нынешних микропроцессоров.

История развития микропроцессоров в полной мере подчиняется диалектике эволюционного усовершенствования архитектуры. Начиная от машины ENIAC, содержавшей 19 тыс. ламп, производительность компьютеров росла на порядок каждые пять лет. Большое число транзисторов на современном кристалле делает возможным применить в одном микропроцессоре все известные способы повышения производительности, сообразуясь только с их совместимостью. Однако для полного использования возможностей аппаратуры уже недостаточно ограничиться только аппаратно реализованными алгоритмами управления, достаточно единообразно функционирующими во всех ситуациях. Поэтому при реализации усложненной логики управления используется программное обеспечение, для поддержки которого вводятся дополнительные команды и регистры управления микропроцессора. В свою очередь, формирование программ для потактного управления микропроцессором под силу только компилятору. Таким образом, в современных микропроцессорах возник симбиоз программных и аппаратных средств. Этот симбиоз представляет собой нечто большее, нежели эволюционный ход развития, а смену самого направления развития микропроцессоров, выражающуюся в переходе к мультитредовым и многопроцессорным архитектурам.

С позиции реализации такого симбиоза открываются следующие способы повышения производительности:

1) увеличение емкости памяти внутри кристалла;

2) увеличение количества арифметико-логических устройств;

3) введение блоков обработки мультимедийных данных, ранее использовавшихся, например, в сигнальных микропроцессорах;

4) интеграция на кристалле функций управления памятью и периферийными устройствами, для исполнения которых в традиционных микропроцессорах используются наборы микросхем («чипсеты»);

5) интеграция на кристалле интерфейсов сетевых и телекоммуникационных систем, что позволяет соединять эти микропроцессоры друг с другом и телекоммуникационными и вычислительными сетями без дополнительных адаптеров.

3.2 Увеличение объема внутрикристальной памяти3.2.1 Организация внутрикристальной памяти

Современное состояние микроэлектроники характеризуется растущим разрывом между скоростью обработки данных в микропроцессорах и быстродействием внекристальной оперативной памяти. Можно уже говорить о том, что время выполнения однотактной команды микропроцессора на порядок и более меньше времени доступа к памяти вне кристалла. В таких условиях прибегают к построению многоуровневой иерархической памяти с использованием внутрикристальной кэш-памяти и применению мультитредовой архитектуры МТА, в которой задержка доступа в память в одном процессе «скрывается» за временем выполнения других процессов.

Кроме того, для уменьшения разрыва в быстродействии между процессором и памятью существует технология встроенной памяти DRAM, позволяющая в едином производственном цикле формировать на одном кристалле логические схемы и схемы динамической памяти. Следует отметить, что идея создания однокристального компьютера всегда была популярной, и сегодня проблема размещения на одном кристалле встраиваемого блока памяти EDRAM (embedded DRAM) достаточно большой емкости и микропроцессорного ядра близка к своему решению

3.2.2 Кэш-память с несколькими уровнямиПостоянный рост емкости кэш-памяти микропроцессора сопровождался усложнением процесса управления, что вылилось в переход от кэш-памяти со сквозной записью к кэш-памяти с буферизированной и обратной записями. При этом в микропроцессорах использовалось программное управление режимом записи кэш-строк путем установки бита, переключающего режимы сквозной и обратной записи кэш-строки. Однако в случае промаха в кэш-памяти возрастающий разрыв между временем выполнения команды и временем доступа в память привел к недопустимо большим потерям производительности. Поэтому в микропроцессоры были введены команды управления кэшированием. Например, в Pentium III появились команды нового типа, обеспечивающие: запись данных из регистров в память, минуя кэш; чтение данных из памяти в регистры, минуя кэш; запись данных из памяти выборочно в кэш первого и второго уровня; запись данных из кэш-памяти и буферов записи в память.

Команды упреждающего кэширования позволяют заранее загружать в кэш нужные данные, обеспечивая возможность записи данных в кэш-память различных уровней, что уменьшает задержки, связанные с доступом к основной памяти. Команды записи данных из кэш-памяти и буферов записи позволяют поддерживать когерентность кэш-памяти и основной памяти при выполнении, например, команд упреждающего кэширования. Однако вряд ли прагматично требовать управления кэш-памятью при программировании на языках высокого уровня – распределение памяти всегда было одной из функций компилятора. Тем более логично потребовать чтобы компилятор выполнял управление кэш-памятью, сокращая простои процессора в ожидании данных.

3.2.3 Наборы регистров в мультитредовой архитектуреДругой, по сравнению с организацией кэш-памяти, метод построения внутрикристальной памяти применяется в мультитредовой архитектуре, основная особенность которой – использование совокупности регистровых файлов. Эта архитектура решает проблему разрыва между скоростью обработки в процессоре и временем доступа в основную память за счет переключения в каждом такте процессора на работу с очередным регистровым файлом. Каждый регистровый файл обслуживает один вычислительный процесс – тред (поток). Всего в каждом процессоре имеется n регистровых файлов, поэтому запрос, выданный в основную память каждым из потоков, может обслуживаться в течение n-1 такта, вплоть до момента, когда процессор снова переключится на тот же регистровый файл. Выбор значения n определяется отношением времени доступа в память ко времени выполнения команды процессором. Конечно, задача формирования потоков из последовательной программы должна, по возможности, решаться компилятором. В противном случае будущее этой архитектуры окажется ограниченным узкой проблемной ориентацией.

Компания Tera объявила о разработке проекта мультитредового микропроцессора, реализующего процессор МТА. Level One, приобретенная Intel, выпустила мультитредовый сетевой микропроцессор IXP1200, содержащий в своем составе 6 четырехтредовых процессоров. IBM анонсировала проект компьютера Blue Gene, кристалл микропроцессора которого включает 32 восьмитредовых процессора. В кристалл встроена память EDRAM, организованная в 32 блока. Каждый блок соответствует одному из 32 процессоров и имеет шину доступа 256 разрядов. Поскольку EDRAM обладает высокой пропускной способностью и малой задержкой, то при восьмитредовой структуре процессора становится возможным отказаться от кэш-памяти, вместо которой между процессором и памятью используется небольшая буферная память.

3.3 Увеличение числа и состава функциональных устройств3.3.1 Увеличение числа функциональных устройств

Память – ресурс, непосредственно не производящий вычислений. Увеличение емкости памяти на кристалле дает прирост производительности, но после достижения некоторой величины этот прирост оказывается существенно меньше, чем обеспечиваемый использованием того же ресурса транзисторов кристалла для построения дополнительной совокупности функциональных устройств. Основное препятствие на пути повышения производительности за счет увеличения числа функциональных устройств – это организация загрузки этих устройств полезной работой, которую можно проводить динамически путем исследования программного кода на стадии исполнения и статически на уровне компиляции программ. Первый подход используется в суперскалярных микропроцессорах, второй – в микропроцессорах с длинным командным словом.

Весьма привлекательно выглядит намерение возложить на компилятор выявление команд, допускающих параллельное исполнение на разных функциональных устройствах. Однако существуют проблемы, которые нельзя решить на уровне компиляции. Поэтому наряду со статическим распараллеливанием компилятором на уровне команд должны развиваться аппаратные реализации методов динамического внеочередного исполнения команд микропроцессоров.

Во время компиляции трудно, а иногда и невозможно установить длительность исполнения отдельных команд, в связи с тем, что возникают промахи при обращении к кэш-памяти, арифметические переполнения, формирование недопустимых адресов и другие исключительные ситуации. Кроме того, определение зависимости между командами записи в память и чтения из памяти может быть выполнено только после вычисления адресных выражений, что возможно лишь в ходе исполнения программы. Команды, выбранные на исполнение, могут следовать друг за другом в неизменном порядке, определяемом при их выборке из памяти, либо их порядок может изменяться, позволяя исполнять команды, для которых готовы операнды. Внеочередное исполнение команд предполагает следующие механизмы:

- переименование регистров с целью устранения ресурсных зависимостей «запись после чтения» и «запись после записи»;

- предсказание переходов;

- динамическое назначение команд на исполнительные устройства, включая изменение порядка исполнения по сравнению с порядком, в котором эти команды были извлечены.

Динамическое назначение команд на исполнительные устройства реализуется резервирующей станцией, состоящей из совокупности элементов ассоциативной памяти. Каждый из элементов содержит позиции для размещения кода операции, наименования первого операнда, его значения, признака доступности первого операнда, наименования второго операнда, его значения, признака доступности второго операнда и наименования регистра результата. Когда команда завершает исполнение и вырабатывает результат, то наименование результата сравнивается с наименованиями операндов в резервирующей станции. Если в резервирующей станции обнаруживается команда, ждущая этого результата, то данные записываются в соответствующую позицию и устанавливается признак их доступности. Когда у команды доступны все операнды, инициируется ее исполнение. Резервирующая станция следит за доступностью операндов и при получении команды все готовые операнды из регистрового файла переписываются в поля этой команды. Когда все операнды готовы, команда исполняется.

Процесс функционирования процессора с внеочередным исполнением команд иллюстрирует рис. 3.1:

Рисунок 3.1 - Процесс функционирования процессора с внеочередным исполнением команд

3.3.2 Мультимедийные расширенияМногие производители расширяют сегодня функциональные возможности выпускаемых микропроцессоров за счет введения специализированных блоков для мультимедийных приложений. Подобный блок имелся уже в микропроцессоре второго поколения Intel 80860, и на некоторых приложениях его использование давало существенный прирост производительности. Аналогичные блоки включены и в другие микропроцессоры Intel (ММХ-расширение системы команд Pentium и 70 новых SIMD-команд Pentium III), AMD (3D Now!), Sun (VIS SPARC), Compaq (Alpha MVI), HP (PA-RISC MAX2), SGI/Mips (MDMX), Motorola (PowerPC AltiVec).

Возможны различные варианты встраивания команд мультимедийной обработки в систему команд микропроцессора: на уровне функционального блока, использующего общий с другими блоками файл регистров (Pentium MMX) или на уровне отдельного процессора со своим регистровым файлом, используя разнесенную (decoupled) архитектуру. Последний вариант применен в Pentium III и PowerPC AltiVec.

Команды мультимедийной обработки задают в режиме SIMD-процессора параллельную обработку нескольких единиц данных, представленных, как правило, малоразрядными (8, 16, 32) числами в формате с фиксированной точкой. Однако это не исчерпывает всех текущих потребностей и, например, в Pentium III введена параллельная обработка в режиме SIMD-процессора четырех 32-разрядных операндов в формате с плавающей точкой.

3.4 Интеграция функций3.4.1 Системы на одном кристалле

С ростом количества транзисторов на кристалле стало возможно построение микросхем, в которых микропроцессор вместе с памятью на кристалле выступает в роли одного из составных элементов (ядер) систем на одном кристалле (SOC — system on chip). В кристалле интегрируются функции, для исполнения которых обычно используются наборы микросхем, сетевые платы и другие специализированные микросхемы. Это, с одной стороны, позволяет существенно увеличить пропускную способность между компонентами кристалла по сравнению с пропускной способностью между разными кристаллами, реализующими по отдельности каждую функцию. И, как следствие, поднять производительность систем. С другой стороны, при уменьшении количества кристаллов резко упрощается изготовление и монтаж плат, что ведет к повышению надежности и снижению стоимости систем.

В кристалл интегрируются интерфейсы сетевых и телекоммуникационных систем, что позволяет без дополнительных адаптеров соединять микропроцессоры друг с другом, с телекоммуникационными и вычислительными сетями. Интеграция коммуникационных интерфейсов в кристалл микропроцессора была впервые проделана в транспьютерах. Однако это были упрощенные интерфейсы, позволяющие связываться лишь с другими транспьютерами. В процессорах Motorola MPC8260 поддерживается уже множество телекоммуникационных протоколов, включающих, например, 10/100 Mбит/с Ethernet, 155 Mбит/с ATM, 256 каналов 64 Кбит/с HDLC. Компания Motorola предлагает два семейства кристаллов, в которых в качестве ядра используется PowerPC 603e – это семейство на основе технологий AltiVec и PowerQUICC.

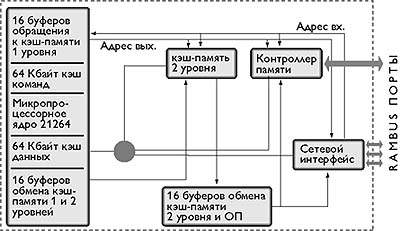

3.4.2 Системы с распределенной разделяемой памятьюОриентация разработчиков на создание систем с распределенной разделяемой памятью привела к интеграции в кристалл блока управления когерентностью многоуровневой памяти на кристалле и распределенной внешней памяти, доступ к блокам которой выполняется через интегрированную в тот же кристалл коммуникационную среду. В качестве примеров этого подхода можно назвать микропроцессоры Alpha 21364, Power4, а также Blue Gene. В качестве ядра у микропроцессора Alpha 21364 используется Alpha 21264, но на кристалле интегрированы: шестивходовый частично ассоциативный кэш второго уровня емкостью 1,5 Мбайт; контроллер памяти, поддерживающий работу с динамической памятью Direct Rambus; сетевой интерфейс.

Рисунок 3.2 - Архитектура микропроцессора Alpha 21364

Для динамического исполнения в микропроцессоре Alpha 21364 (рис.3.2) рассматриваются сразу 80 команд – больше, чем у любого другого процессора. После декодирования команда помещается в очередь к устройствам с фиксированной или плавающей точкой. Команды, получившие все операнды, конкурируют за доступ к функциональным устройствам: двум блокам операций с плавающей точкой, выполняющим сложение, умножение, деление, извлечение квадратного корня и четырем целочисленным устройствам (двум общего назначения и двум адресной арифметики). Последние наряду с простыми арифметическими и логическими операциями выполняют все команды загрузки и сохранения как целочисленных данных, так и данных в формате с плавающей точкой. Целочисленные АЛУ общего назначения выполняют арифметические и логические операции, сдвиги и переходы. Одно из целочисленных АЛУ выполняет также умножение, а другое – новый набор команд обработки видеоданных. Для динамического переименования доступны 41 из 80 целочисленных регистров и 41 из 72 регистров с плавающей точкой.

Обмен данными между кэшами первого и второго уровня, кэшем первого уровня и оперативной памятью буферизирован (по 16 буферов для каждого уровня памяти).

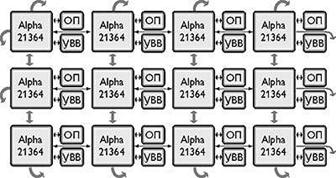

Интеграция компонентов в одном кристалле позволяет существенно упростить и удешевить системы, реализуемые на основе данного микропроцессора. Благодаря встроенному сетевому интерфейсу упрощается объединение микропроцессоров в высокопроизводительные многопроцессорные системы. Сетевой интерфейс поддерживает 4 межпроцессорных соединения типа «точка-точка» со скоростью передачи данных 10 Гбайт/с каждый при задержке 15 нс. Сетевой интерфейс обеспечивает когерентность кэшей в многопроцессорной системе и реализует асинхронный обмен данными с адаптивной маршрутизацией. Пример структуры многопроцессорной системы на основе микропроцессоров Alpha 21364 показан на рис. 3.3:

Рисунок 3.3 - Пример структуры многопроцессорной системы

Микропроцессор имеет пятый порт – ввода-вывода, работающий на скорости обмена 3 Гбайт/с.

Процессоры Alpha 21364 и Power4 объединяет общность архитектурных решений: суперскалярная микроархитектура, внеочередное исполнение команд, большая кэш-память на кристалле, специализированный порт для основной памяти, а также высокоскоростные линки для объединения микропроцессоров в системы с архитектурой NUMA с распределенной разделяемой памятью (distributed shared memory — DSM).

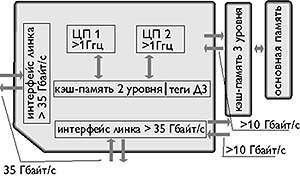

Каждый процессор Power4 (рис. 3.4) подобен Power3 и имеет два конвейерных блока для работы с 64-разрядными операндами с плавающей точкой на частоте 1 ГГц, выбирающих на исполнение по 5 команд каждый и 2 блока для работы с памятью. В процессорах реализуется внеочередное исполнение команд. Микропроцессор реализован на кристалле, содержащем 170 млн. транзисторов. Для достижения тактовой частоты 1,1 ГГц стадии конвейеров имеют задержку 8-10 вентилей.

Процессоры содержат раздельные кэш-памяти команд и данных первого уровня емкостью по 64 Кбайт каждая. Кроме того, имеется разделяемая (общая) кэш-память на кристалле второго уровня и внешняя кэш-память третьего уровня. Для образования мультипроцессорных конфигураций имеются 3 линка с суммарной пропускной способностью 45 Гбайт/с.

Рисунок 3.4 - Архитектура Power4

Наряду с параллелизмом уровня команд (ILP), процессор использует параллелизм уровня тредов (TLP). Динамическое выявление параллелизма позволяет предотвращать простои процессора при трудно выявляемых статически исключительных ситуациях, например, промахе в кэш-памяти. Power4 изготавливается по 0,18-микронной технологии SOI («кремний на изоляторе») с медными проводниками и 5 слоями металла на кристалле площадью 400 мм2.

Отличительная особенность Power4 – наличие кэш-памяти второго уровня, разделяемой двумя процессорами кристалла, а также внешними процессорами других кристаллов через линки шириной 16 байт, работающие на тактовой частоте более 500 МГц, что обеспечивает пропускную способность свыше 8 Гбайт/с. Суммарная пропускная способность 4 линков составляет более 35 Гбайт/с. При объединении 4 кристаллов и их размещении, как показано на рис. 3.5, проводники линков могут быть достаточно короткими и, что важно, прямыми.

Рисунок 3.5 - Пример объединения Power4 в фрагмент многопроцессорной системы

Физически кэш-память второго уровня емкостью около 1,5 Мбайт состоит из трех одинаковых блоков, доступ к которым выполняется через коммутатор с пропускной способностью на уровне 100 Гбайт/с. Протокол когерентности обеспечивает размещение данных, поступивших по линкам, в том блоке кэш-памяти, который использовался для размещения данных последним.

Порт кристалла Power4, предназначенный для подключения кэш-памяти третьего уровня емкостью до 32 Мбайт имеет ширину 16 байт для каждого из двух направлений пересылки данных. Порт функционирует на 1/3 от тактовой частоты процессоров кристалла, что обеспечивает пропускную способность к памяти на уровне 10 Гбайт/с. Теги кэш-памяти третьего уровня расположены внутри кристалла, что ускоряет реализацию протокола когерентности. Для работы с основной памятью может быть использована восьмипоточная программная предвыборка данных непосредственно в кэш-память первого уровня на кристалле. Пересылать можно одновременно до 20 строк кэша.

Каждый из двух процессоров Power4 имеет систему команд IBM ISA, реализованную в RS/6000 и AS/400 и полностью совместимую с системой команд Power PC. Сохранение системы команд, вызванное поддержкой двоичного кода пользователей, потребовало применения как однотактных команд, так и микропрограмм и даже прерываний для программной реализации наиболее сложных команд ISA.

3.5 Однокристальные мультитредовые и мультискалярные системыСовременные микропроцессоры, например, Alpha 21264 и Pentium III, относятся к однотредовым, использующим параллелизм уровня команд, выявляемый либо статически (компилятором), либо динамически (аппаратурой микропроцессора), либо комбинацией этих двух методов. Параллелизм уровня тредов при использовании этих микропроцессоров может быть выявлен только статически. Динамическое выявление параллелизма уровня тредов в рамках архитектур однотредовых процессоров практически невозможно, так как требует просмотра большого количества команд на предмет их одновременного исполнения – расширения окна исполнения. Это влечет за собой усложнение логических схем управления внеочередным исполнением команд, что может привести к снижению тактовой частоты микропроцессора. Для разрешения данного противоречия предлагаются мультитредовые и мультискалярные микропроцессоры.

3.5.1 Основы мультитредовой архитектурыПри всем различии подходов к созданию мультитредовых микропроцессоров, общим для них является введение множества устройств выборки команд, каждое из которых организует окно исполнения для одного треда. В рамках одного треда выполняется предсказание переходов, переименование регистров, динамическая подготовка команд к исполнению. Тем самым, общее число команд, находящихся в обработке, значительно превышает размер окна исполнения однотредового процессора, с одной стороны, и тактовая частота не лимитируется размером окна исполнения, с другой стороны.

Выявление тредов может выполняться компилятором при анализе исходного кода на языке высокого уровня или исполняемого кода программы. Однако компиляторы не всегда могут разрешить проблемы зависимостей при использовании регистров и ячеек памяти между тредами, что требуется уже в ходе исполнения тредов. Для этого в микропроцессор вводится специальная аппаратура условного исполнения тредов, предусматривающая возврат с отбрасыванием наработанных результатов при обнаружении нарушения зависимостей между тредами. Нарушением зависимости, например, может служить запись по вычисляемому адресу в одном треде в ту же ячейку памяти, из которой выполняется чтение, которое должно следовать за этой записью, в другом треде. В случае, если адреса записи и чтения не совпадают, нарушение отсутствует. При совпадении адресов фиксируется нарушение, которое должно вернуть исполнение треда к команде чтения правильного значения.

Интерфейс между аппаратурой мультитредового процессора, поддерживающей протекание каждого отдельного треда и аппаратурой, общей для исполнения всех тредов, может быть установлен как сразу после устройств выборки команд тредов, так и на уровне доступа к разделяемой памяти. В первом случае все треды используют один регистровый файл и один набор функциональных устройств. Тесная связь по ресурсам позволяет эффективно исполнять последовательные программы с сильной зависимостью между тредами. В этом случае имеет место именно реализация мультискалярного мультитредового процессора.

Во втором случае для исполнения каждого треда, фактически, выделяется функционально законченный процессор. В целом эта структура ориентирована на исполнение независимых и слабо связанных тредов, порождаемых либо одной программой, либо их совокупностью. В этом случае скорее надо говорить не о процессоре, а о системе на одном кристалле. Возможно также промежуточное расположение интерфейса, соответствующее аппаратным средствам, ориентированным на реализацию определенного типа совокупности тредов.

По оценкам, при обработке транзакций мультитредовый микропроцессор Alpha 21464 будет в десять раз производительнее, чем Alpha 21264.

Похожие работы

... программе, однако аппаратура обнаружения и устранения конфликтов между логически связанными командами обеспечивает получение результатов в соответствии с заданной программой. Соответствующая организация коммутирующих магистралей, обеспечивающая засылку результата операции непосредственно в буфер, хранящий логически зависимую команду, задержанную из-за конфликта, или непосредственно ...

... элементов, глобальное пространство имен, а также лавинообразную первоначальную загрузку сети. Таким образом ОСРВ SPOX имеет необходимые механизмы для создания отказоустойчивой распределенной операционной системы реального времени, концепция построения которой описана в главе 2. 4.3 Аппаратно-зависимые компоненты ОСРВ Модули маршрутизации, реконфигурации, голосования реализованы как аппаратно- ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

... оснащать их дополнительными устройствами сотен различных производителей. Итак, после начала широкого внедрения персональных компьютеров в повседневную жизнь, продолжилось быстрое развитие вычислительной техники. Остановимся на наиболее важном элементе: микропроцессор – это эффективный с технологической и экономической точки зрения инструмент для переработки возрастающих потоков информации. Новое ...

0 комментариев