Навигация

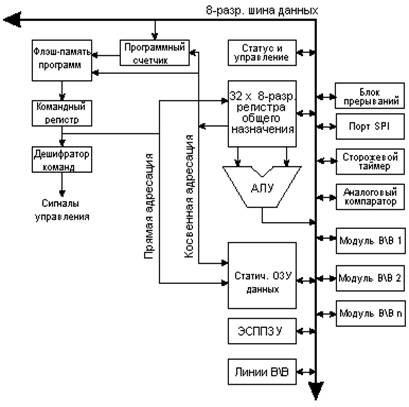

Базова архітектура CISC МК

2. Базова архітектура CISC МК.

В дійсний час, серед усіх 8-розрядних МК, сімейство MCS51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що випускають його модифікації. Воно одержало свою назву від першого представника цього сімейства -- МК і8051, випущеного в 1980. Вдалий набір периферійних пристроїв, можливість гнучкого вибору зовнішньої або внутрішньої програмної пам'яті і невисока вартість забезпечили цьому МК успіх на ринку. З погляду технології МК і8051 був для свого часу дуже складним виробом -- у кристалі було використано 128 тис. транзисторів, що в 4 рази перевищувало кількість транзисторів у 16-розрядному мікропроцесорі 8086.

Важливу роль у досягненні такої високої популярності сімейства 8051 зіграла відкрита політика фірми Intel, спрямована на широке поширення ліцензій на ядро 8051 серед великої кількості провідних компаній - виробників світу.

У результаті на сьогоднішній день існує більш 200 модифікацій МК сімейства 8051, що випускаються майже 20-ю компаніями. Ці модифікації містять у собі кристали з найширшим спектром периферії: від простих 20-вивідних пристроїв з одним таймером до 100-вивідних кристалів з 10-розрядними АЦП, масивами таймерів-лічильників, апаратними 16-розрядними помножувачами і 64 Кб програмної пам'яті на кристалі. Основними напрямками розвитку є: збільшення швидкодії (підвищення тактової частоти і вдосконалення архітектури), збільшення обсягу ОЗП і FLASH- пам'яті на кристалі з можливістю внутрісхемного програмування, використання складних периферійних пристроїв.

Усі МК із сімейства MCS-51 мають загальну систему команд. Наявність додаткового устаткування впливає тільки на кількість регістрів спеціального призначення.

Склад та основні характеристики базової моделі сімейства МК MCS-51

Базовою моделлю сімейства МК MCS51 і основою для всіх наступних модифікацій є МК і8051. Це -- восьмирозрядний ОМК, що має:

- вбудований тактовий генератор;

- адресний простір пам'яті програм -- 64 КБ;

- адресний простір пам'яті даних -- 64 КБ;

- внутрішню (резидентну) пам'ять програм ПЗП -- 4 КБ;

- внутрішню (резидентну) пам'ять даних ОЗП -- 128 байт;

- додаткові можливості по виконанню операцій булевої алгебри (побітових операції);

- 32 двонапрямлені й індивідуально адресовані лінії введення/виведення (порти Р0-Р3);

- послідовний порт (Serial Port);

- 2 шістнадцатирозрядні багатофункціональні таймери/лічильники (Т/С 0, Т/С 1);

- повнодуплексний асинхронний прийомопередавач;

- векторну систему переривань із двома рівнями пріоритету і шістьма джерелами подій.

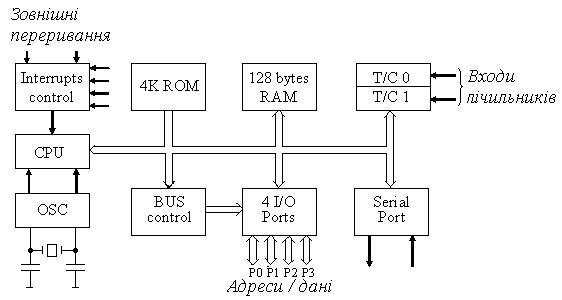

Спрощена структурна схема і8051 подана на рис. 2, призначення виводів мікросхеми -- на рис. 3.

Рис. 2. Структурна схема і8051

Bus control –блок керування; Interrupts control – система переривань; CPU – центральний процесор; OSC – генератор; ROM –ПЗП; RAM – ОЗП; I/O ports – порти введення-виведення.

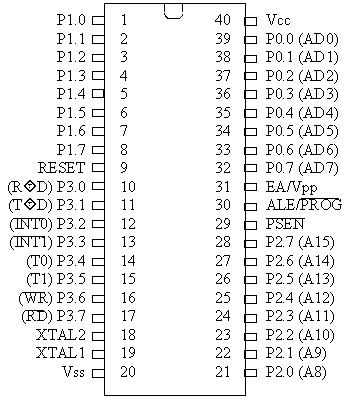

Рис. 3. Призначення виводів I-8051.

Позначення сигналів на рис. 3:

· Uss -- потенціал загального проводу ("землі");

· Ucc -- основна напруга живлення +5 В;

· XTAL1, XTAL2 -- виводи для підключення кварцового резонатора;

· RESET -- вхід загального скидання МК;

· PSEN -- дозвіл зовнішньої пам'яті програм;

· ALE -- строб адреси зовнішньої пам'яті;

· ЕА -- відключення внутрішньої програмної пам'яті;

· P1 -- восьмибітний квазідвонапрямлений порт введення/виведення (кожен розряд порту може бути запрограмований як на введення, так і на виведення інформації);

· P2 -- порт, аналогічний Р1; крім того, виводи цього порту використовуються для видачі адресної інформації при звертанні до зовнішньої пам'яті програм або даних;

· РЗ -- аналогічний Р1; крім того, виводи цього порту можуть виконувати ряд альтернативних функцій, що використовуються при роботі таймерів, порту послідовного введення/виведення, контролера переривань, і зовнішньої пам'яті програм і даних;

· P0 — восьмибітний двонапрямлений порт введення/виведення інформації.

2.2. Організація пам’яті базової моделі сімейства МК MCS-51

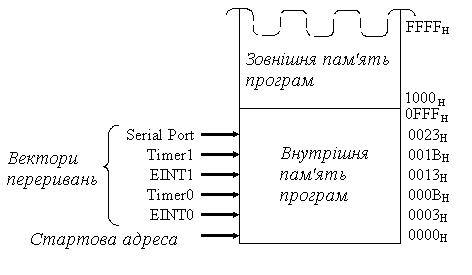

Вся серія MCS51 має гарвардську архітектуру (пам'ять даних відділена від пам'яті програм). Організація резидентної пам'яті програм (РПП) зображена на рис. 4.

Область нижніх адрес РПП використовується системою переривань, забезпечена підтримка п'яти джерел переривань -- двох зовнішніх (EINT1 та EINT1), двох переривань від таймерів та одного від послідовного порту. Молодша адреса ПЗП використовується для початку роботи ОМК після скидання сигналом RESET.

Пам'ять програм може бути розширена до 64 кБайт через приєднання зовнішніх ВІС ПЗП.

Рис. 4. Організація РПП

ОЗП або резидентна пам'ять даних (РПД) складається з двох областей. Перша область – ОЗП даних із інформаційній ємністю 128*8 біт з адресами 0 -- 7FH. Друга область – регістри спеціальних функцій SFR (Special Function Register) з адресами 80Н – FFH. РПД.

Похожие работы

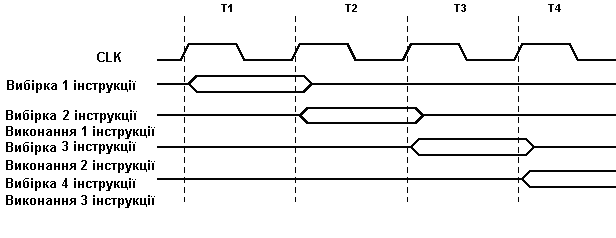

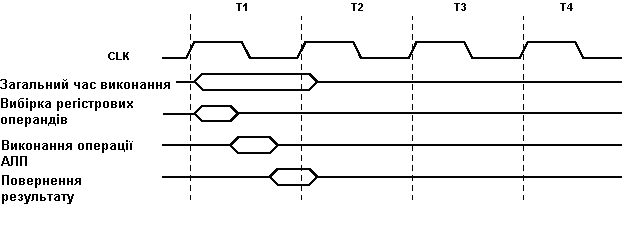

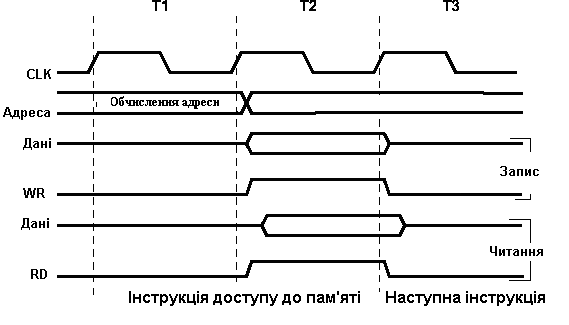

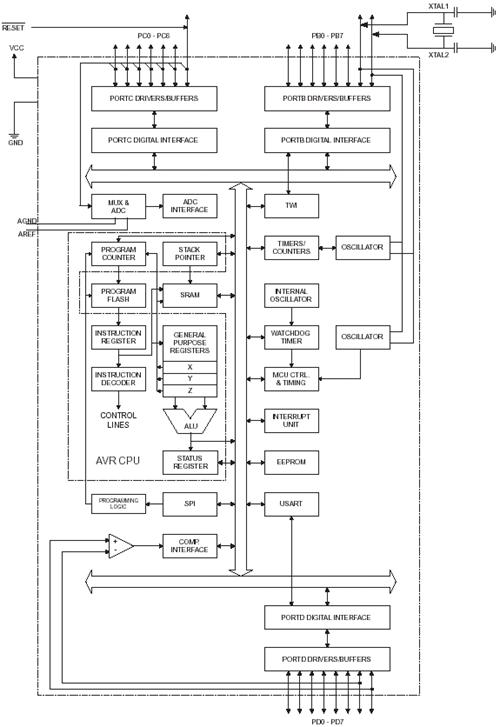

... повинно бути прийняте в розрахунок при порівнянні продуктивності різних моделей контролерів. 2. Однокристальні AVR-мікроконтролери Архітектуру RISC МК розглянемо на прикладі AT90S 2313. Це малопотужний восьмирозрядний КМОП МК, заснований на розширеній AVR RISC-архітектурі. Він належить до сім’ї AVR-МК загального призначення і створений дослідницьким центром фірми Atmel Corp. (Норвег ...

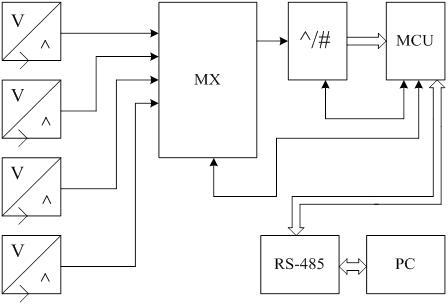

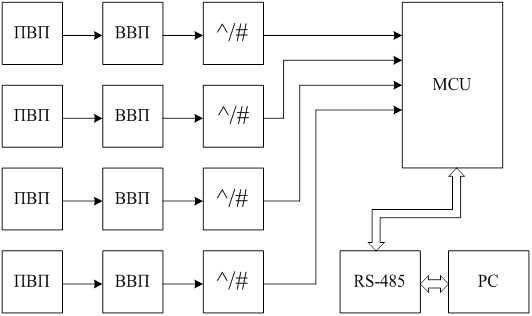

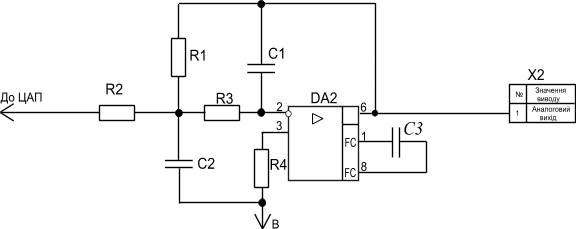

... габаритність та точність. Розглянемо першу структурну схему, яка приведена на рисунку 2.1. Рисунок 2.1 – Перший варіант реалізації структурної схеми системи для визначення складу вихлопних газів автомобілів Позначення на схемі: V/ – датчик концентрації, який використовується для визначення концентрації вихлопних газів автомобілів; МХ – мультиплексор; – аналого-цифровий перетворювач; ...

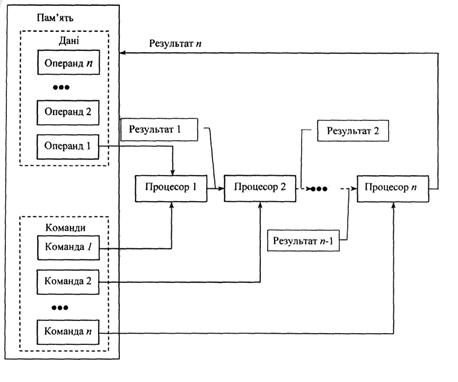

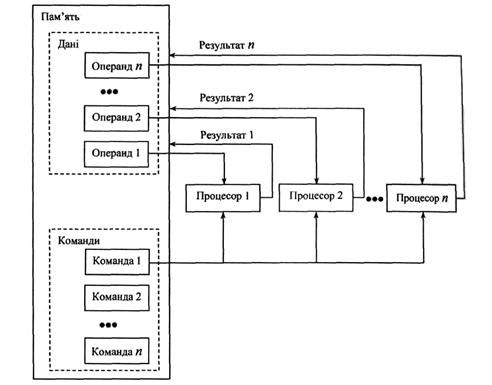

... для розв'язання особливо складних науково-технічних задач, оброблення великих обсягів даних у реальному масштабі часу, моделювання складних систем, автоматизованого проектування складних об'єктів, а також у системах керування (промислових і військових). Макет найпотужнішого суперкомп'ютера ES (Earth Simulator) Центра моделювання Землі (Earth Simulator Center) у Йокогамі (Японія) показаний рис. ...

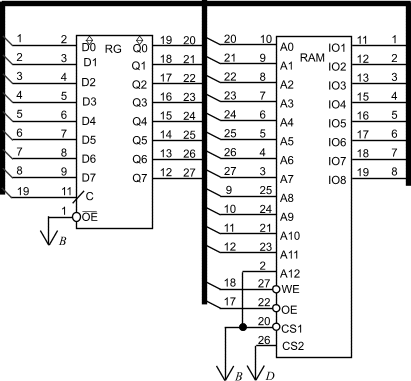

... вводу-виводу, блок спряження із ПЕОМ та інші пристрої, що забезпечують роботу того чи іншого модулю. 1. Розробка структурної схеми МПС В даній курсовій роботі розробляється система управління та керування об’єктом на базі одно кристального RISK AVR-мікроконтролера (МК) ATMega1281V-8AU , що складається з: - Системи аналогового вводу інформації; - Системи аналогового виводу інформації; - ...

0 комментариев