Навигация

ТЕСТИРОВАНИЕ ПРОЦЕССОРА И ПОДТВЕРЖДЕНИЕ ПРАВИЛЬНОСТИ ЕГО РАБОТЫ С ПОМОЩЬЮ ВРЕМЕННЫХ ДИАГРАММ

7 ТЕСТИРОВАНИЕ ПРОЦЕССОРА И ПОДТВЕРЖДЕНИЕ ПРАВИЛЬНОСТИ ЕГО РАБОТЫ С ПОМОЩЬЮ ВРЕМЕННЫХ ДИАГРАММ

Описание процессора:

library ieee;

use ieee.std_logic_1164.all;

entity CPU is

generic(file_name: string:=".\src\MEM.DAT");

port(RST: in std_logic;

Clk: in std_logic);

end entity;

architecture CPU of CPU is

-----------------------------------------------------------

component MAR is

port(D: in std_logic_vector(7 downto 0);

Q: out std_logic_vector(7 downto 0);

RST: in std_logic;

Clk: in std_logic);

end component;

-----------------------------------------------------------

component REGI is

port(D: in std_logic_vector(7 downto 0);

Q: out std_logic_vector(7 downto 0);

EI: in std_logic;

RST: in std_logic;

Clk: in std_logic);

end component;

------------------------------------------------------------

component MBR is

port(D: in std_logic_vector(7 downto 0);

Q: out std_logic_vector(7 downto 0);

EO: in std_logic;

RST: in std_logic;

Clk: in std_logic);

end component;

-------------------------------------------------------------

component PC is

port(D: in std_logic_vector(7 downto 0);

Q: out std_logic_vector(7 downto 0);

EI: in std_logic;

Inc: in std_logic;

RST: in std_logic;

Clk: in std_logic);

end component;

--------------------------------------------------------------

component ALU is

port(In1: in std_logic_vector(7 downto 0);

OP: in std_logic;

Res: out std_logic_vector(7 downto 0);

RST: in std_logic;

Clk: in std_logic);

end component;

---------------------------------------------------------------

component BlockRG is

port(D: in std_logic_vector(7 downto 0);

Addr: in std_logic_vector(1 downto 0);

EI: in std_logic;

RST: in std_logic;

Clk: in std_logic);

end component;

----------------------------------------------------------------

component Memory is

generic(file_name: string:= "MEM.DAT");

port (addr: in std_logic_vector(7 downto 0);

data: out std_logic_vector(7 downto 0);

rd: in std_logic;

ld: in std_logic);

end component;

-----------------------------------------------------------------

component CU is

port(Instr: in std_logic_vector(1 downto 0);

AccIn: out std_logic;

ALURL: out std_logic;

RegIn: out std_logic;

PCIn: out std_logic;

PCInc: out std_logic;

MBROut: out std_logic;

IRIn: out std_logic;

MEMRd: out std_logic;

Reset: inout std_logic;

RST: in std_logic;

Clk: in std_logic);

end component;

signal AccIn,ALURL,RegIn,PCIn,PCInc,MBROut,IRIn,MEMRd,Reset:std_logic;

signal Inst_Addr:std_logic_vector(7 downto 0);

signal mem_mbr,BUS1,pc_mar,mar_mem,acc_alu:std_logic_vector(7 downto 0);

begin

DD0: CU port map(Instr=> Inst_Addr(7 downto 6),AccIn=> AccIn,ALURL=> ALURL,

RegIn=> RegIn,PCIn=> PCIn,PCInc=> PCInc,MBROut=> MBROut,IRIn=> IRIn,

MEMRd=> MEMRd,Reset =>Reset,RST => RST, Clk => Clk);

DD1: ALU port map(In1=> acc_alu,OP=> ALURL,Res=> BUS1,RST=> RST,Clk => Clk);

DD2: Memory generic map(file_name)port map(addr => mar_mem,data => mem_mbr,rd=> MEMRd,ld=> RST);

DD3: BlockRG port map(D => BUS1,Addr=> Inst_Addr(5 downto 4),EI => RegIn,RST=> RST,Clk=> Clk);

IR: REGI port map(D => BUS1,Q=> Inst_Addr,EI=> IRIn,RST => RST, Clk => Clk);

DD4: MBR port map(D=> mem_mbr,Q=> BUS1,EO=> MBROut,RST => RST, Clk => Clk);

DD5: MAR port map(D => pc_mar,Q => mar_mem,RST => RST, Clk => Clk);

DD6: PC port map(D=> BUS1,Q => pc_mar,EI=> PCIn,Inc => PCInc,RST=> RST,Clk=> Clk);

ACC: REGI port map(D=> BUS1,Q=> acc_alu,EI=> AccIn,RST=> RST,Clk=> Clk);

end CPU;

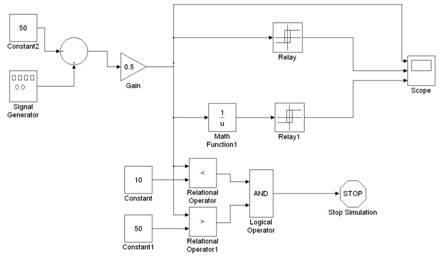

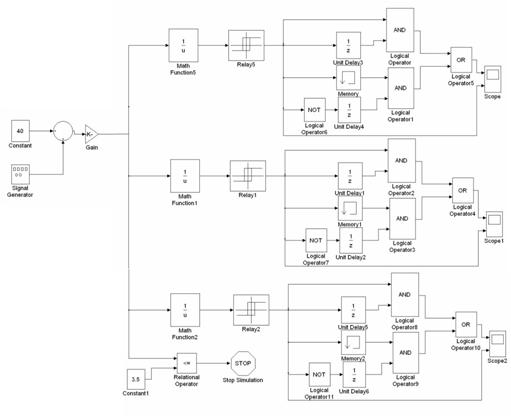

Программа для проверки работоспособности процессора написана в отдельном файле Mem.dat, хранящемся на диске, и подгружается в память прямо в процессе работы средствами языка VHDL. Приведем пример тестовой программы и покажем результаты ее работы.

01.00.0000 11111111 ;mov a,#

10.00.0000 00000001 ;mov ro,#

10.01.0000 00000010 ;mov rl,#

10.10.0000 00000100 ;mov r2,#

10.11.0000 00001000 ;mov r3,#

01.00.0000 00000001 ;mov a,#

11.00.0000 00000000 ;rl a

00.00.0000 00001100 ;jmp #

Обработчик файла построен таким образом, что игнорируются все символы, не входящие в тип std_logic. Первый столбец, первые 2 бита – код команды, вторые 2 бита - номер РОН), второй столбец – операнды. В случае с командой сдвига содержимое поля операнда не имеет значения.

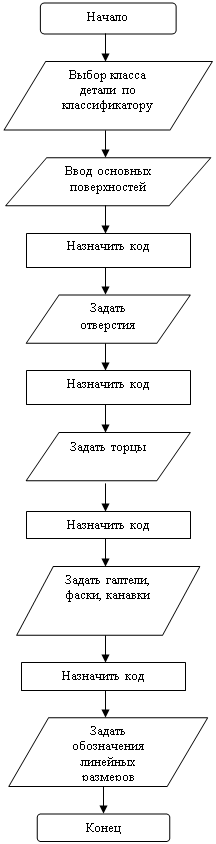

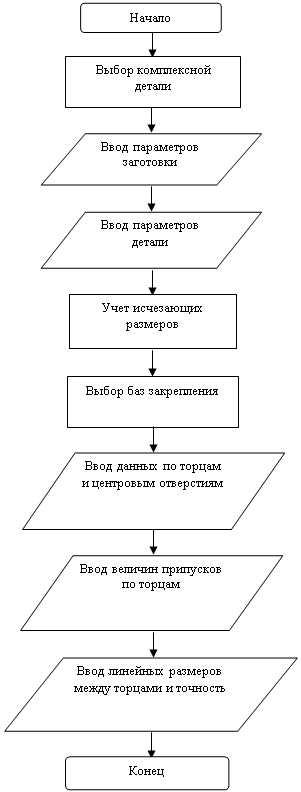

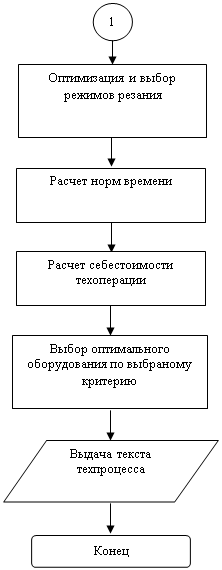

Загружается число в аккумулятор, затем в каждый из РОН, после чего производится очередная запись в аккумулятор и сдвиг его содержимого, искусственно зацикленный командой JMP.

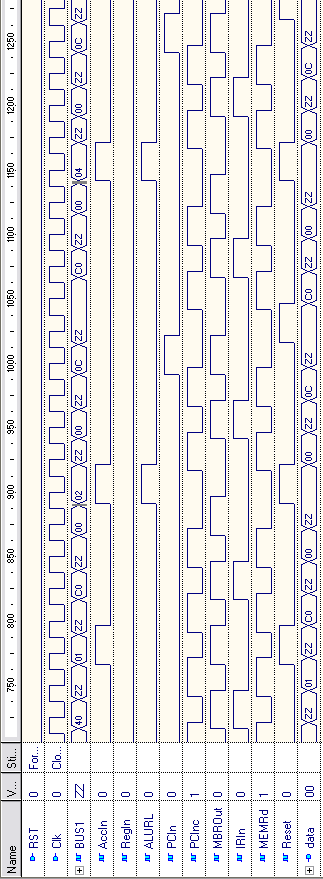

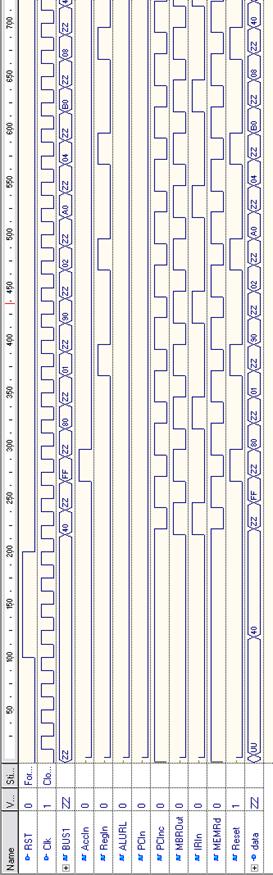

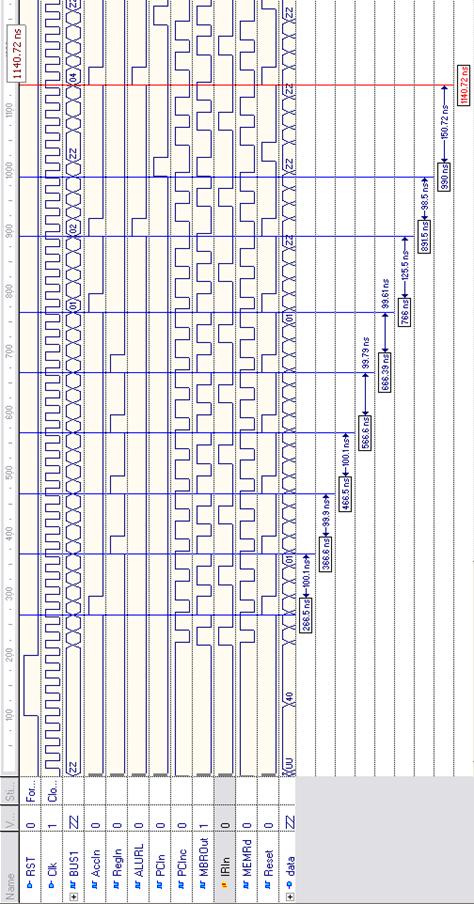

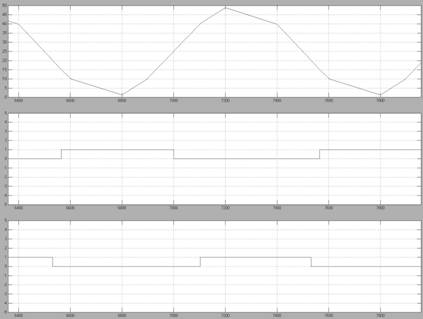

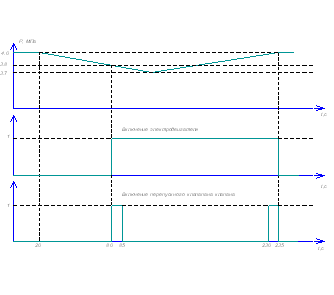

Временная диаграмма работы процессора при заданной программе приведена на рис. 3, где data – данные из памяти. На рис. 4. можно увидеть задержки и определить временные характеристики работы процессора.

Рис. 3. Временная диаграмма работы процессора

Рис. 4. Временная диаграмма работы процессора

ВЫВОДЫ

При выполнении курсовой работы было произведено моделирование процессора с устройством управления на жёсткой логике, имеющего ряд специальных регистров, а также четыре регистра общего назначения. Тестовая программа была успешно выполнена, что вполне свидетельствует о его корректной работе.

Структурная схема, разработанная в этой работе, естественно, не является единственно возможной. Но на ее примере можно усвоить основные принципы построения цифровых вычислительных систем, такие как микропрограммное управление, совместное использование шин процессора различными устройствами со всеми вытекающими отсюда требованиями к организации работы этих устройств: синхронизации, сингулярности передач информации и другими.

Данная схема обладает одной магистралью, она достаточно проста в исполнении, хотя одномагистральная система не всегда позволяет просто реализовать некоторые операции, а именно такая система занимает намного меньше места на печатной плате чем двухмагистральная (и тем более трехмагистральная), что и дает ей преимущества при конструировании небольших устройств.

По диаграмме работы процессора видно, что выполнение команды пересылки занимает в среднем 100 ns, команда сдвига немного больше 125 ns. Полное выполнение всех команд производится за 1050 ns.

Похожие работы

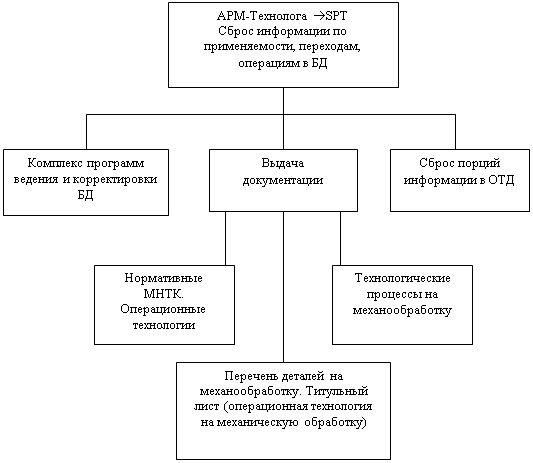

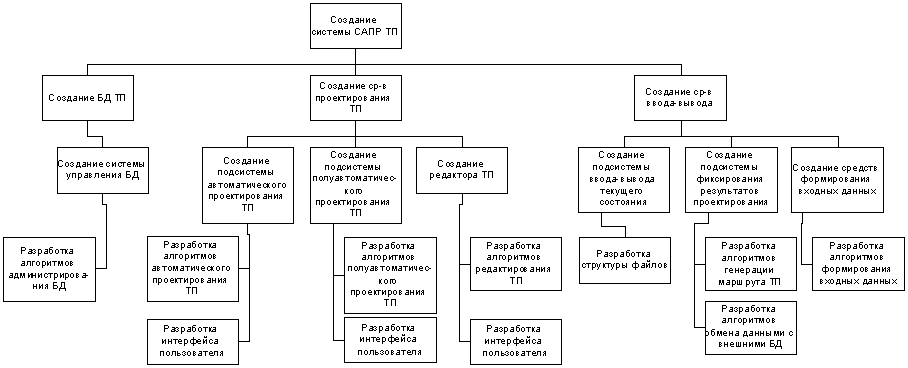

... недостаточно). Возможно включение комплекса в план учебного процесса, для обучения студентов. 2. Специальная часть разработка программного обеспечения для организации интерфейса программно-методического комплекса 2.1 Разработка технического задания на реализацию специальной части дипломного проекта Наименование программного изделия - "Интерфейс программно - методического комплекса для ...

... ребрами) изображают конструктивные и потоковые функциональные структуры [14]. Принципы построения функциональных структур технических объектов рассматриваются в последующих главах курса "Основы проектирования им конструирования" не включенных в настоящее пособие. Для систем управления существуют характеристики, которые можно использовать в качестве критериев для оценки структур. Одна из них - ...

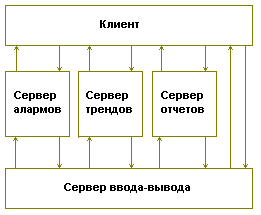

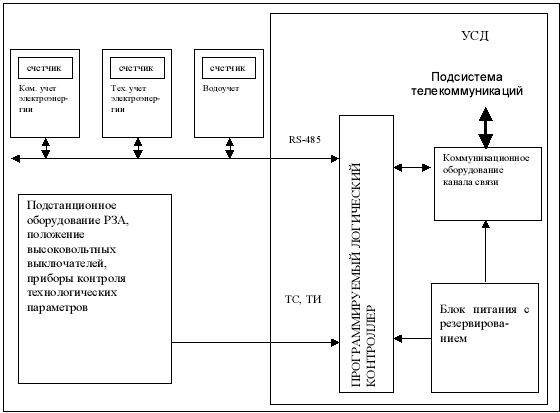

... К. Сатпаева» для просмотра и ввода информации системы оперативно-диспетчерского контроля и управления, создаваемые на Visual Basic. Специфика используемого в системе оперативно-диспетчерского контроля и управления РГП «Канал им. К. Сатпаева» ПО такая, что разработка ПО, как таковая, может производиться только при создании самой системы. Применяемое ПО является полуфабрикатом. Основная задача ...

... ). Подпрограмма завершена, управление передается назад вызывавшему модулю. 6. Технико-экономическое обоснование 6.1 Пути снижения затрат за счет внедрения системы Внедрение автоматической системы управления маслонапорной установкой гидроэлектростанции решает следующие задачи - Полностью автоматическая система управления маслонапорной установкой не требует участия человека ...

0 комментариев