Навигация

Головним недоліком RS-тригерів є наявність заборонених комбінацій сигналів

2. Головним недоліком RS-тригерів є наявність заборонених комбінацій сигналів.

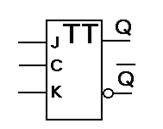

3. JK-тригери

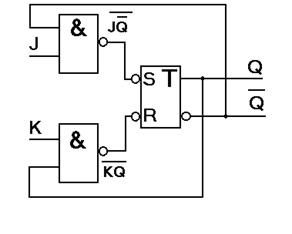

Універсальний JK-тригер функціонує майже так само, як і звичайний RS-тригер. При цьому вхід J виконує роль входу S, а вхід K- входу R. Таким чином активний сигнал (рівень логічної 1), поданий на вхід J, переводить тригер у стан 1, а поданий на вхід К – у стан 0. Різниця полягає лише у тому, що при J=K=1 тригер змінює свій стан на протилежний. JK-тригер не має заборонених комбінацій вхідних сигналів, наявність яких була головною вадою RS-тригерів.

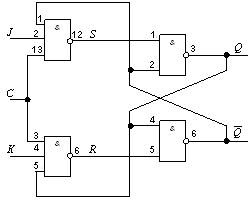

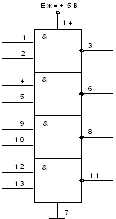

Найпростіший JK-тригер у базисі ТА-НІ можна побудувати на тому ж наборі елементів, що й розглянутий вище синхронний RS-тригер. Схема такого тригера подана на рис. 4. Алгоритм його функціонування поданий у таблиці переходів 4.

Таблиця 4

| J | K | Qt+1 |

| 0 | 0 | Qt |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

|

Нехай тригер знаходиться у стані 0 (Q=0, ![]() =1), а на його входах діють сигнали J=K=0. При цьому на виходах обох елементів ТА-НІ – рівні логічної 1. У відповідності до рядка 4 з таблиці 2, така комбінація вхідних сигналів (R=S=1) у асинхронному RS-тригері з інверсними входами забезпечує режим зберігання інформації (стан тригера лишається незмінним). Якщо ж подати на входи тригера сигнали J=K=1, то вихідний сигнал елементу В не зміниться, а на виході елементу А з’явиться сигнал логічного 0. При такій комбінації вхідних сигналів (R=1 S=0) асинхронний RS-тригер з інверсними входами переходить до стану 1 (рядок 2 таблиці 2). Аналогічні міркування можна провести стосовно одиничного початкового стану тригера. Таким чином, JK-тригер при надходженні на його входи сигналів J=K=1 дійсно переходить до протилежного стану.

=1), а на його входах діють сигнали J=K=0. При цьому на виходах обох елементів ТА-НІ – рівні логічної 1. У відповідності до рядка 4 з таблиці 2, така комбінація вхідних сигналів (R=S=1) у асинхронному RS-тригері з інверсними входами забезпечує режим зберігання інформації (стан тригера лишається незмінним). Якщо ж подати на входи тригера сигнали J=K=1, то вихідний сигнал елементу В не зміниться, а на виході елементу А з’явиться сигнал логічного 0. При такій комбінації вхідних сигналів (R=1 S=0) асинхронний RS-тригер з інверсними входами переходить до стану 1 (рядок 2 таблиці 2). Аналогічні міркування можна провести стосовно одиничного початкового стану тригера. Таким чином, JK-тригер при надходженні на його входи сигналів J=K=1 дійсно переходить до протилежного стану.

Треба зазначити, що на практиці застосовуються значно складніші схеми JK-тригерів ніж та, яку ми щойно розглянули.

По-перше, реальні JK-тригери завжди мають вхід синхронізації для розширення їх функціональних можливостей.

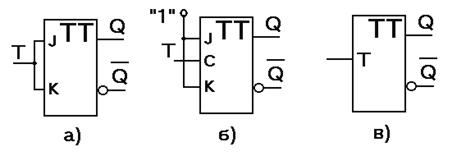

По-друге, синхронні JK-тригери завжди мають двохступеневе запам’ятовування інформації. У цьому випадку вони мають у своєму складі два RS-тригери, один з яких називають керованим, а другий – керуючим. Часто такі тригери називають MS-тригерами (від ангел. Master-Slave). Така побудова синхронних тригерів (не тільки JK, але й будь-яких типів) дозволяє усунути можливість встановлення тригера у невизначений стан через перехідні процеси при перемиканні або при короткочасних змінах вхідних сигналів. Графічне позначення двохступеневого синхронного JK-тригера наведено на рис.5.

|

Рис. 4 Рис. 5

4. D і T тригери

4.1. Тригер з лічильним входом (Т-тригер).

Як було розглянуто раніше, при надходженні на обидва інформаційні входи JK-тригера рівней логічної 1 (J=K=1), він переходить до протилежного стану. З цієї точки зору найбільш доцільним способом перетворення JK-тригера на Т-тригер є просте об’єднання його J і K-входів для отримання лічильного Т-входу, як це зображено на рис.6а.

На практиці частіше за все використовують схему Т-тригера, у якій у якості Т-входу використовують вхід С синхронного -тригера, а на J,K входи подають рівень логічної 1, як це зображено на рис.6б. Алгоритм функціонування Т-тригера (однаковий для схем на рис.7а та 6б подано у вигляді таблиці переходів (табл.5). Умовне графічне зображення тригера показано на рис.6в.

|

Рис. 6

4.2.Тригер затримки (D-тригер)

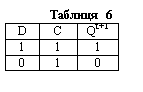

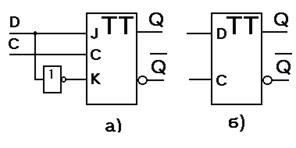

D-тригер має один інформаційний вхід (D- вхід) і вхід синхронізації С. Цей тригер завжди побудовано як синхронний та двохступеневий. Головне призначення D-тригера – затримка сигналу, який подано на вхід D. D-тригер може бути отриманий з JK-тригера після об’єднання входу K з входом J через інвертор так, як це зображено на рис.7а.  Отриманий таким чином вхід називають D-входом. Функціонування D-тригера відображено у таблиці переходів табл.6, у якій виключені рядки для С=0. При С=0 тригер може необмежений час зберігати раніше встановлений стан. При С=1, інформація, що надходить на вхід D, потрапляє до тригера, але на виході його вона з’явиться з затримкою на один такт. Графічне позначення D-тригера зображено на рис.7б.

Отриманий таким чином вхід називають D-входом. Функціонування D-тригера відображено у таблиці переходів табл.6, у якій виключені рядки для С=0. При С=0 тригер може необмежений час зберігати раніше встановлений стан. При С=1, інформація, що надходить на вхід D, потрапляє до тригера, але на виході його вона з’явиться з затримкою на один такт. Графічне позначення D-тригера зображено на рис.7б.

Рис.8

В И С Н О В К И

Найпростішими елементами з пам’яттю є тригери – логічні елементи, яки можуть знаходитись у одному з двох стійких станів і переходити до іншого стану під впливом зовнішніх сигналів (через це тригер інколи називають бістабільним елементом). Перехід у інший стан частіше за все залежить не тільки від поточних значень вхідних сигналів, але й від попереднього стану тригера.

За функціональними можливостями розрізняють:

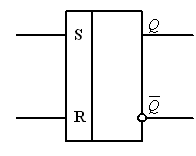

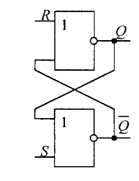

6. Тригер з окремим встановленням станів 0 та 1 (RS-тригер). R(від англійського RESET) – окремий вхід 0. S(від англійського SET) – окремий вхід встановлення тригера у стан 1.

7. Універсальний тригер з інформаційними входами J та K(JK-тригер). Тут J- вхід для встановлення універсального тригера у стан 1. K - вхід для встановлення універсального тригера у стан 0.

8. Тригер, який отримує інформацію лише через один вхід D (тригер затримки або D – тригер, від англійського DELAY – затримка). Тут вхід D – це інформаційний вхід для встановлення тригера у стан, який відповідає логічному рівню на цьому вході.

9. Тригер із лічильним входом (Т-тригер). Тут вхід Т – це лічильний вхід.

Тригери на логічних елементах, є основою побудови складних функціональних пристроїв.

У апаратурі військового зв’язку та АСУ тригери застосовують для:

- побудови лічильників імпульсів;

- ділення частот надходження імпульсів;

- побудови регістрів;

- побудови розподілювачів імпульсів;

- побудови запам'ятовуючих пристроїв.

Похожие работы

... RS-тригер є складовою частиною всіх інших тригерів, розглянемо більш детально основні структурні схеми RS-тригерів. Асинхронний RS- тригер є найпростішим за структурою. Він має тільки два логічних елементи (мінімальну кількість). Рис. 1. Схема та умовне графічне позначення асинхронного RS-тригера з прямими входами на елементах 2"АБО-НІ". Таблиця 1. Стани асинхронного RS-тригера на основі мі ...

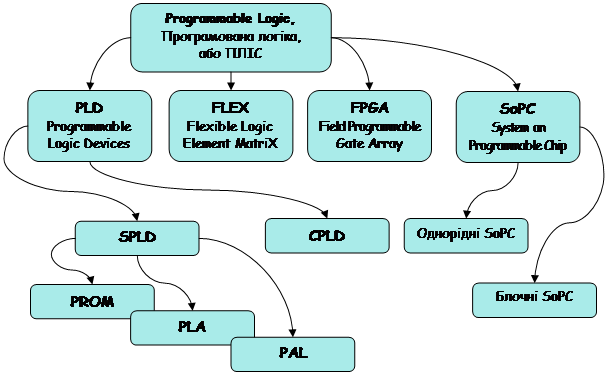

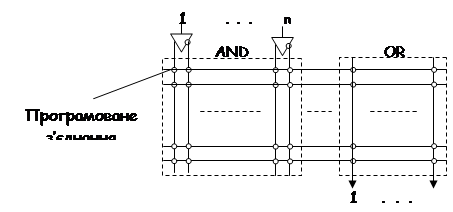

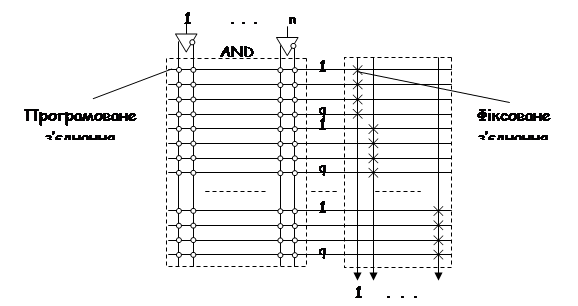

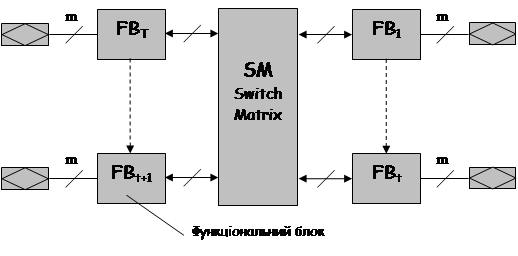

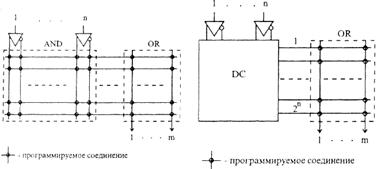

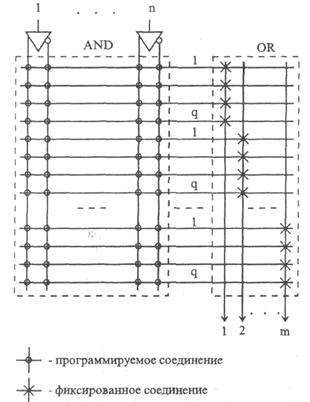

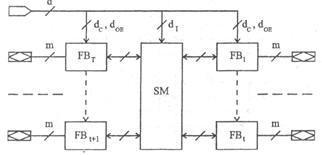

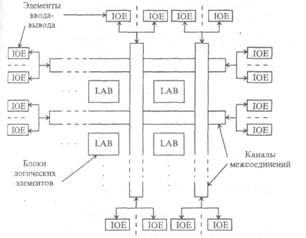

... цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС. Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності бі ...

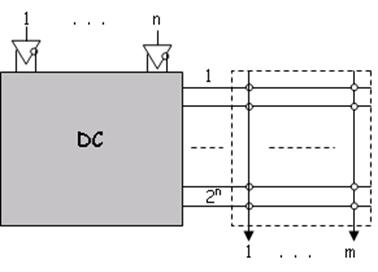

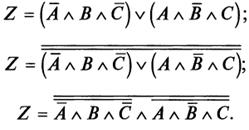

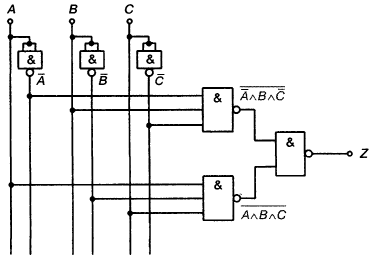

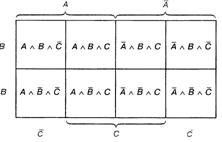

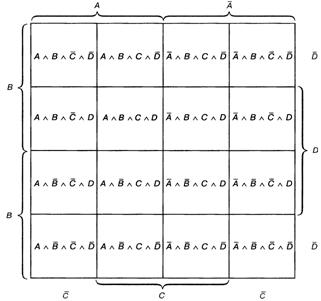

... стовпця відповідає повна кон’юнкція. Якщо в таблиці істинності змінна приймає значення 0, у відповідній повній кон’юнкції вона інвертується. Нормальна кон’юнктивна форма (нормальна форма І) - форма запису рівнянь алгебри логіки, в якій повні диз’юнкції пов’язані між собою логічним множенням. Повна диз’юнкція-операція логічного додавання, в якій беруть участь всі наявні вхідні змінні або їх ...

... ім часом компанії-виробники PLD звернули увагу на розробку саме таких програмних пакетів. 2. Призначення та структура системи автоматизованого проектування MAX+PLUS II Система автоматизованого проектування MAX+PLUS II являє собою інтегроване середовище для розробки цифрових пристроїв на базі програмувальних логічних інтегральних схем фірми Altera. Він забезпечує виконання всіх етапів, необхі ...

0 комментариев