Навигация

Основные понятия и определения

1.1. Основные понятия и определения

Микроэлектроника - основное направление электроники, которое изучает проблемы конструирования, исследования, создания и применения электронных устройств с высокой степенью функциональной и конструктивной интеграции.Микроэлектронное изделие, реализованное средствами интегральной технологии и выполняющее определённую функцию по преобразованию и обработке сигналов, называется интегральной микросхемой (ИМС) или просто интегральной схемой (ИС).

Микроэлектронное устройство - совокупность взаимосвязанных ИС, выполняющая законченную достаточно сложную функцию (либо несколько функций) по обработке и преобразованию сигналов. Микроэлектронное устройство может быть конструктивно оформлено в виде одной микросхемы либо на нескольких ИМС.

Под функциональной интеграцией понимают увеличение числа реализуемых (выполняемых) некоторым устройством функций. При этом устройство рассматривается как единое целое, неделимое. А конструктивная интеграция - это увеличение количества компонентов в устройстве, рассматриваемом как единое целое. Примером микроэлектронного устройства с высокой степенью конструктивной и функциональной интеграции, является микропроцессор (см. выше), который, как правило, выполняется в виде одной «большой» ИМС.

Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС.

Особенностью цифровой схемотехники является широкое применение для описания процессов функционирования устройств формальных либо формально-естественных языков и основанных на них формализованных методов проектирования. Формальными языками являются булева алгебра (алгебра логики, алгебра Буля) и язык «автоматных» логических функций - алгебра состояний и событий. Благодаря использованию формализованных методов, достигается многовариантность в решении прикладных задач, появляется возможность оптимального выбора схемотехнических решений по тем или иным критериям.

Формальные методы характеризуются высоким уровнем абстракции - отвлечения, пренебрежения частными свойствами описываемого объекта. Акцентируется внимание только на общих закономерностях во взаимных связях между компонентами объекта - его составными частями. К таким “закономерностям”, например, относятся правила арифметических действий в алгебре чисел (правила сложения, вычитания, умножения, деления). При этом отвлекаются от смысла чисел (количество ли это яблок, либо столов и т.д.). Эти правила строго формализованы, формализованы и правила получения сложных арифметических выражений, а также процедуры вычислений по таким выражениям. В таких случаях говорят, формальными являются и синтаксис и грамматика языка описания.

У формально-естественных языков синтаксис формализован, а грамматика (правила построения сложных выражений) подчиняется грамматике естественного языка, например русского либо английского. Примерами таких языков являются различные табличные языки описания. В частности, теоретической базой описания цифровых устройств является «Теория конечных автоматов» [1] или «Теория релейных устройств и конечных автоматов» [2].

1.2. Классификация микроэлектронных устройств

Всё многообразие микроэлектронных устройств (МЭУ) можно классифицировать по различным признакам:

· по принципу и характеру действия;

· по функциональному назначению и выполняемым функциям;

· по технологии изготовления;

· по области применения;

· по конструктивному исполнению и техническим характеристикам и так далее.

Рассмотрим теперь более детально разделение МЭУ по классификационным признакам.

По принципу (характеру) действия все МЭУ подразделяются на аналоговые и цифровые. Выше уже были даны понятия аналоговых и дискретных устройств и, в том числе цифровых. Здесь же отметим, если в дискретных устройствах все сигналы принимают только два условных значения - логического нуля (лог.0) и логической единицы (лог.1), то устройства называют логическими. Как правило, все цифровые устройства относятся к логическим устройствам.

В зависимости от выполняемых функций (функционального назначения) различают следующие микроэлектронные устройства:

I. Аналоговые

1.1. Усилительные устройства (усилители).

1.2. Функциональные преобразователи, выполняющие математические операции с аналоговыми сигналами (например, интегрирование, дифференцирование и т.д.).

1.3. Измерительные преобразователи и датчики физических величин.

1.4. Модуляторы и демодуляторы, фильтры, смесители и генераторы гармонических колебаний.

1.5. Запоминающие устройства.

1.6. Стабилизаторы напряжений и токов.

1.7. Интегральные микросхемы специального назначения (например, для обработки радио- и видеосигналов, компараторы, коммутаторы и т.д.).

II. Цифровые МЭУ

2.1. Логические элементы.

2.2. Шифраторы, дешифраторы кодов и кодопреобразователи.

2.3. Запоминающие элементы (триггеры).

2.4. Запоминающие устройства (ОЗУ, ПЗУ, ППЗУ, ПЛМ и др.).

2.5. Арифметико-логические устройства.

2.6. Селекторы, формирователи и генераторы импульсов.

2.7. Счётные устройства (счётчики импульсов).

2.8. Цифровые компараторы, коммутаторы дискретных сигналов.

2.9. Регистры.

2.10. Микросхемы специального назначения (например, таймерные, микропроцессорные комплекты ИС и т.д.).

Приведённая классификация далеко не исчерпывающая, но позволяет сделать вывод, что номенклатура цифровых устройств значительно шире номенклатуры аналоговых МЭУ.

Кроме перечисленных, существуют микросхемы преобразователей уровней сигналов, например триггеры Шмита, у которых входные сигналы являются аналоговыми, а выходные - дискретными, двоичными. Такие микросхемы занимают промежуточное положение. Аналогично, микросхемы аналого-цифровых и цифро-аналоговых преобразователей (АЦП и ЦАП), коммутаторы аналоговых сигналов, управляющиеся дискретными сигналами, следует отнести к «промежуточным» МЭУ.

В зависимости от количества реализуемых функций различают однофункциональные (простые) и многофункциональные (сложные) МЭУ. В многофункциональных устройствах функции могут выполняться одновременно либо последовательно во времени. В зависимости от этого, в первом случае, устройства называют устройствами «параллельного» действия, а во втором случае - устройствами последовательного действия или «последовательностными». Если настройка многофункционального устройства на выполнение той или иной функции осуществляется путём коммутации входов (физической перекоммутацией электрических цепей), то такое устройство называют устройством с «жёсткой логикой» работы. А если изменение выполняемых функций производится с помощью дополнительных внешних сигналов (на так называемых управляющих входах), то такие МЭУ следует отнести к «программно-управляемым». Например, ИМС арифметико-логических устройств (АЛУ) могут реализовать арифметические либо логические операции с двумя многоразрядными двоичными числами. А настройка на выполнение арифметических (либо логических) операций осуществляется одним дополнительным внешним сигналом, в зависимости от значения которого будут выполняться желаемые действия. Поэтому АЛУ следует отнести к программно-управляемым МЭУ.

По технологии изготовления все ИМС делятся на:

1. Полупроводниковые;

2. Плёночные;

3. Гибридные.

В полупроводниковых ИС все компоненты и соединения выполнены в объёме и на поверхности кристалла полупроводника. Эти ИС делятся на биполярные микросхемы (с фиксированной полярностью питающих напряжений) и на униполярные - с возможностью смены полярности питающего напряжения. В зависимости от схемотехнического исполнения «внутреннего содержания» биполярные микросхемы делятся на следующие виды:

· ТТЛ - транзисторно-транзисторной логики;

· ТТЛш - транзисторно-транзисторной логики с транзисторами и диодами Шотки;

· ЭСЛ - эмиттерно-связанной логики;

· И2Л - инжекционной логики и другие.

Микросхемы униполярной технологии выполняются на МДП-транзисторах («металл–диэлектрик–полупроводник»), либо на МОП-транзисторах («металл–окисел–полупроводник»), либо на КМОП-транзисторах (комплиментарные «металл – окисел – полупроводник»).

В плёночных ИС все компоненты и связи выполняются только на поверхности кристалла полупроводника. Различают тонкоплёночные (с толщиной слоя менее 1 микрона) и толстоплёночные с толщиной плёнки более микрона. Тонкоплёночные ИС изготавливаются методом термовакуумного осаждения и катодного распыления, а толстоплёночные - методом шелкографии с последующим вжиганием присадок.

Гибридные ИС состоят из «простых» и «сложных» компонентов, расположенных на одной подложке. В качестве сложных компонентов обычно используются кристаллы полупроводниковых либо плёночных ИС. К простым относятся дискретные компоненты электронной техники (транзисторы, диоды, конденсаторы, индуктивности и т.д.). Все эти компоненты конструктивно располагаются на одной подложке и на ней также выполняются электрические соединения между ними. Причём одна подложка с расположенными на ней компонентами образуют один «слой» гибридной ИС. Различают однослойные и многослойные гибридные ИС. Многослойная гибридная ИС способна выполнять достаточно сложные функции по обработке сигналов. Такая микросхема равносильна по действию «микроблоку» устройств, либо, если она предназначена для самостоятельного применения, действию «целого» блока.

Кроме того, любые микросхемы оцениваются количественным показателем их сложности. В качестве такого показателя используется «степень интеграции» - k, равная десятичному логарифму от общего количества N компонентов, размещённых на одном кристалле полупроводника, то есть

k = lq N. (1)

В соответствии с формулой (1) все микросхемы делятся на микросхемы 1-й, 2-й, третьей и так далее степеней интеграции. Степень интеграции лишь косвенно характеризует сложность микросхем, поскольку принимается во внимание только конструктивная интеграция. Фактически же сложность микросхемы зависит и от количества взаимных связей между компонентами.

В инженерной практике используется качественная характеристика сложности микросхем в понятиях «малая», «средняя», «большая» и «сверхбольшая» ИС.

В табл.1.1 приведены сведения о взаимном соответствии качественных и количественных мер сложности ИС по их видам.

Таблица 1.1

| Наименование ИС | Вид ИС | Технология изготовления | Количество компонентов на кристалле | Степень интеграции k |

| Малая (МИС) | Цифровая | Биполярная | 1…100 | 1-я и 2-я |

| Униполярная | ||||

| Аналоговая | Биполярная | 1…30 | ||

| Средняя (СИС) | Цифровая | Биполярная | 101…500 | 3-я |

| Униполярная | 101…1000 | |||

| Аналоговая | Биполярная | 31…100 | ||

| Униполярная | ||||

| Большая (БИС) | Цифровая | Биполярная | 501…2000 | 4-я |

| Униполярная | 1001…10000 | |||

| Аналоговая | Биполярная | 101…300 | ||

| Униполярная | ||||

| Сверхбольшая (СБИС) | Цифровая | Биполярная | Более 2000 | 5-я |

| Униполярная | Более 10000 | |||

| Аналоговая | Биполярная | Более 300 | ||

| Униполярная |

Из анализа табл.1.1 следует, что в сравнении с цифровыми ИС аналоговые микросхемы при одинаковых степенях интеграции имеют в своём составе (на кристалле полупроводника) более чем в три раза, меньшее число компонентов. Это объясняется тем, что активные компоненты (транзисторы) аналоговой микросхемы работают в линейном режиме и рассеивают большее количество энергии. Необходимость отвода тепла, выделяющегося при рассеянии энергии, ограничивает количество компонентов, размещаемых на одном кристалле. У цифровых микросхем активные компоненты работают в ключевом режиме (транзисторы либо заперты, либо открыты и находятся в режиме насыщения). В этом случае рассеиваемая мощность незначительна, и количество выделяемого тепла также незначительно и следовательно число компонентов на кристалле может быть размещено больше. (Размеры кристаллов стандартизованы и ограничены.) При униполярной технологии объём кристалла, занимаемый под полевой транзистор приблизительно в три раза меньше объёма, занимаемого биполярным транзистором (n-p-n или p-n-p типа). Этим объясняется тот факт, что активных компонентов на кристалле стандартных размеров в униполярной микросхеме можно разместить больше.

По конструктивному исполнению в зависимости от функциональной сложности микроэлектронные устройства подразделяются:

- на простые микросхемы (ИМС);

- на микросборки;

- на микроблоки.

ИМС - микроэлектронное изделие, изготавливаемое в едином технологическом цикле, пригодное для самостоятельного применения или в составе более сложных изделий (в том числе, микросборок и микроблоков). Микросхемы могут быть бескорпусными и иметь индивидуальный корпус, защищающий кристалл от внешних воздействий.

Микросборка - микроэлектронное изделие, выполняющее достаточно сложную функцию (функции) и состоящее из электрорадиокомпонентов и микросхем, изготавливаемое с целью миниатюризации радиоэлектронной аппаратуры. По существу гибридные микросхемы являются микросборками. Самой простой микросборкой может быть, например, набор микрорезисторов, выполненных на кристалле полупроводника и оформленных в едином корпусе (как микросхема).

Микроблок также является микроэлектронным изделием, состоит из электрорадиокомпонентов и интегральных схем и выполняет сложную функцию (функции).

Как правило, микросборки и микроблоки изготавливаются в различных технологических циклах, и, может быть, на разных заводах-изготовителях.

В качестве классификационных технических характеристик обычно используются потребляемая мощность (одной микросхемой) и быстродействие.

По потребляемой мощности все ИМС можно разделить на: а) микромощные (менее 10 мВт); б) маломощные (не более 100 мВт); в) средней мощности (до 500 мВт) и г) мощные (более или = 0,5 Вт).

По быстродействию (максимальным задержкам времени распространения сигналов через ИС) микросхемы делятся условно на: а) сверхбыстродействующие с граничной частотой fгр переключений свыше 100 МГц; б) быстродействующие (fгр от 50 МГц до 100 МГц); в) нормального быстродействия (fгр от 10 МГц до 50 МГц). При этом задержки распространения составляют порядка от единиц наносекунд (10-9с.) до 0,1 микросекунды (1ms =10-6с.).

Цифровые микроэлектронные устройства, в том числе микросхемы и другие устройства дискретного действия, удобно классифицировать по характеру зависимости выходных сигналов от входных. Как это принято в теории конечных автоматов. В соответствии с этим признаком все устройства принято разделять на комбинационные и последовательностные.

В комбинационных устройствах значения выходных сигналов в какой-либо момент времени однозначно определяются значениями входных сигналов в этот же момент времени. Поэтому можно считать, что работа таких устройств не зависит от времени. Их ещё называют устройствами «без памяти», однотактными устройствами или устройствами однотактного действия. В теории конечных автоматов комбинационные устройства называют «примитивными конечными автоматами».

В последовательностных устройствах значения выходных сигналов (выходные сигналы) зависят от значений входных сигналов не только в рассматриваемый момент времени, но и от значений входных сигналов в предыдущие моменты времени. Поэтому такие устройства называют устройствами с «памятью», многотактными устройствами, а в теории конечных автоматов, просто − конечным автоматом (не тривиальным).

При рассмотрении учебного материала, в дальнейшем, за основную примем именно эту классификацию, так как методы построения (синтеза) и процессы функционирования названных устройств существенно различаются.

Заканчивая изложение вопросов классификации, отметим, что приведённый перечень классификационных признаков и перечень наименований микроэлектронных изделий (микросхем) далеко не исчерпывающий. В дальнейшем, по мере необходимости, этот перечень мы дополним.

1.3. Логические элементыЛогические элементы относятся к простейшим комбинационным «устройствам», имеющим один выход и один-два входа. Своё название они получили по той причине, что их функционирование полностью можно описать логическими функциями и в частности булевыми функциями.

Как и в формальной логике, все высказывания могут быть истинными либо ложными, так и логические функции могут принимать только два условных значения: логической единицы (лог.1) - «истина» и логического нуля (лог.0) - «ложь».

При описании работы логических элементов выходным сигналам ставят в однозначное соответствие функции, а входным сигналам - аргументы этих функций. Таким образом, и функции, и аргументы функций, а также входные и выходные сигналы логических элементов являются двоичными. Если пренебречь реальным временем перехода логического элемента из одного состояния (состояния лог.1) в другое (состояние лог.0), то ни аргументы и ни функции не будут зависеть от фактора времени - переменной времени. Правила получения и преобразования логических выражений рассматривает алгебра логики или булева алгебра.

Основными логическими функциями в алгебре логики принято считать функции от двух аргументов. Им даны названия, введены логические символы для обозначения соответствующих логических операций при их записи в алгебраической форме, а также эти символы используются в условных графических обозначениях (УГО) логических элементов в схемной документации.

Прежде чем рассматривать непосредственно виды логических элементов, рассмотрим вначале общий вопрос о системе обозначений микросхем, содержащих логические элементы. Такие микросхемы относятся к микросхемам малой степени интеграции.

1.3.1. Система условных цифробуквенных обозначений ИМС логических элементовВ отечественной технической литературе, а также при маркировке ИМС отечественного производства, при их изготовлении на заводах-изготовителях, принята 4-х элементная форма обозначений микросхем (рис.1.1).

Первым элементом в обозначении является цифра, которой указывается группа конструктивно-технологического исполнения ИС. Эта цифра может принимать следующие значения:

1, 5, 6, 7 - соответствуют полупроводниковым ИС. Причём цифра 7 используется для обозначения только бескорпусных ИМС;

2, 4, 8 - это гибридные микросхемы;

3 - прочие микросхемы, в том числе, и плёночные.

Перед первым элементом обозначения может стоять буква или две буквы (русского алфавита), они не обязательны, но ими обозначают тип и материал корпуса микросхемы и возможности её применения. Например, буквой К обозначают микросхемы широкого применения в пластмассовом корпусе первого типа. Есть микросхемы специального применения, например, для устройств, эксплуатируемых в условиях тропического климата.

Второй элемент - 2 или 3 цифры, ими обозначают порядковый номер серии микросхем. Всё множество выпускаемых отечественной промышленностью микросхем делится на серии. Серия ИМС - это совокупность ИС единого конструктивно-технологического исполнения, выполняющих различные функции и предназначенных для совместного применения.

Третьим элементом в обозначении являются две русские буквы, первая из которых обозначает подгруппу ИС по функциональному назначению, а вторая буква соответствует виду ИС также по функциональному назначению микросхемы. Например, первая буква Л «говорит», что это ИС логических элементов (подгруппа логика), вторая буква А соответствует логическим элементам вида И-НЕ. В табл.1.2 приведены наиболее употребительные буквенные коды видов ИС по выполняемым функциям.

![]()

И, наконец, 4-м элементом в обозначениях микросхем являются одна или две цифры, обозначающие условный номер микросхемы в рассматриваемой серии. Так, приведённый на рис.1.1 пример обозначения соответствует обозначению полупроводниковой микросхемы серии К155, широкого применения, в пластмассовом корпусе 1-го типа. В её состав входят 4 двухвходовых логических элементов вида И-НЕ (2И-НЕ).

И, наконец, 4-м элементом в обозначениях микросхем являются одна или две цифры, обозначающие условный номер микросхемы в рассматриваемой серии. Так, приведённый на рис.1.1 пример обозначения соответствует обозначению полупроводниковой микросхемы серии К155, широкого применения, в пластмассовом корпусе 1-го типа. В её состав входят 4 двухвходовых логических элементов вида И-НЕ (2И-НЕ).

Обычно четвёртым элементом в обозначении ИМС «зашифровывается» порядковый номер модификации элементов одного вида, различающихся числом входов и способом «организации» выхода.

Кроме названных обозначений, согласно ГОСТ 2.743-91 «Условные графические обозначения в электрических схемах. Элементы цифровой техники», используются другие двухбуквенные коды для обозначения функционального назначения микросхем, например: ИД - декодеры- демультиплексоры, дешифраторы, ИР - регистры, КП - коммутаторы дискретных сигналов и так далее. В частности, буква И соответствует подгруппе микросхем, используемых для построения вычислительных цифровых устройств.

Различные серии ИС отличаются количеством микросхем и их номенклатурой (типономиналами). Типономинал ИС - конкретное условное обозначение, содержащее основные сведения о микросхеме. В процессе развития технологии количество типономиналов ИМС конкретной серии может увеличиваться.

Среди серий микросхем наиболее функционально развиты ИМС транзисторно-транзисторной логики (ТТЛ и ТТЛш). Эти серии характеризуются широкой номенклатурой ИС, поэтому изложение учебного материала будем в основном иллюстрировать примерами этих микросхем.

В указанном выше ГОСТе содержатся также условные графические обозначения логических элементов и приведены правила формирования УГО более сложных логических элементов и модулей. Поэтому следует, прежде всего, ознакомиться с указанным ГОСТом.

Таблица 1.2

| Вид ИС | Обозначение |

| Элементы И-НЕ | ЛА |

| Элементы И-НЕ /ИЛИ-НЕ | ЛБ |

| Расширители по ИЛИ | ЛД |

| Элементы ИЛИ-НЕ | ЛЕ |

| Элементы И | ЛИ |

| Элем. И-ИЛИ-НЕ/И-ИЛИ | ЛК |

| Элементы ИЛИ | ЛЛ |

| Элементы ИЛИ-НЕ/ИЛИ | ЛМ |

| Элементы НЕ | ЛН |

| Прочие элементы | ЛП |

| Элементы И-ИЛИ-НЕ | ЛР |

| Элементы И-ИЛИ | ЛС |

логических элементов и устройств

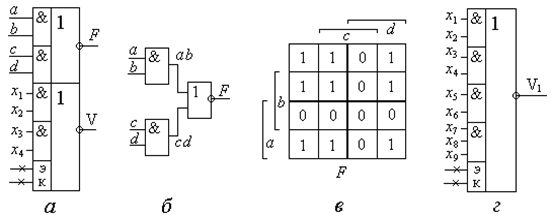

Как уже было отмечено выше, функционирование логических элементов можно описать логическими (булевыми) функциями. В свою очередь логические функции можно определить (задать), перечислив все условия, при которых функция принимает значение лог.1, т.е. по условиям истинности, так и по условиям ложности (значения лог.0). Аналогично, рассматривая работу логического (какого-либо) элемента, можно перечислить все условия, при которых на выходе появляется сигнал лог.1, либо условия, когда на выходе элемента будет присутствовать сигнал лог.0. В этом заключается принцип дуальности (двойственности) в описании логических устройств.

В технике, при описании работы различных устройств, широко используется понятие «активного», в противоположность ему, «неактивного» значения какого-либо сигнала. При этом под активным значением (уровнем) сигнала понимается такое действие, которое вызывает на выходе устройства желаемое действие или, по-другому, устройство оказывает активные действия на внешние устройства. Наоборот, неактивные действия оказывают пассивное действие на внешние устройства. Так, в логике обычно акцентируют внимание на истинности высказываний, поэтому истинность высказываний следует считать по умолчанию их активным значением. Аналогично, при описании технических устройств можно акцентировать внимание на условиях их «срабатывания» либо на условиях «несрабатывания».

Соглашения, при которых сигнал лог.1 считается активным, называют соглашениями «положительной» логики. Наоборот, когда за активное значение принимается уровень лог.0, такие соглашения называют соглашениями «отрицательной» логики. Как правило, за сигнал лог.1 принимается более «высокий» уровень, а за сигнал лог.0 «низкий» уровень сигналов. Например, при использовании ИМС ТТЛ сигналом лог.1 считается напряжение не менее +2,4 В, а сигналом лог.0 - напряжение больше нуля, но не больше 0,4 В. Это - стандартные уровни сигналов в устройствах на ИМС ТТЛ.

Описания, составленные при соглашениях положительной логики и при соглашениях отрицательной логики, логически эквивалентны, так как описывают одно и тоже устройство. Однако сложность технической реализации логических устройств в зависимости от выбранного соглашения может оказаться существенно различной. Поэтому всегда возникает проблема выбора способа описания с целью получения наиболее простого технического решения.

Как уже было сказано, основными функциями алгебры логики являются функции двух переменных. Можно составить эти функции чисто формально, придавая аргументам всевозможные значения (комбинации их значений), и затем придать функциям так же всевозможные значения. Поскольку и аргументы и функции могут принимать только два значения, то нетрудно определить число комбинаций, составленных из аргументов, и число всех возможных функций. Пусть число аргументов будет n, а количество их комбинаций N, тогда

N = 2n. (1.1)

Число же всевозможных логических функций тогда можно рассчитать по формуле

M = 2N = ![]() . (1.2)

. (1.2)

Как видно из формулы (1.2), число булевых (логических) функций быстро растёт с увеличением числа аргументов n. Так, при n =2 получим N=22=4, а М=24=16, т.е. шестнадцать логических функций от двух аргументов.

В табл. 1.3 приведены названия и обозначения функций, их значения на том или ином наборе значений аргументов a и b, а также алгебраические выражения этих функций в дизъюнктивной совершенной нормальной форме (ДСНФ) и конъюнктивной совершенной нормальной форме (КСНФ).

Из анализа этой таблицы следует, что среди множества приведённых функций есть функции-константы «нулевая» и «единичная», функции «повторения» и «инверсии» (функции НЕ) входных переменных a и b, фактически являющиеся функциями одного аргумента, и есть функции, которые существенно зависят от двух аргументов.

В приведённых алгебраических выражениях знаком + (плюс) обозначена операция логического сложения (дизъюнкции), чертой над переменной или над логическим выражением обозначена операция инверсии, а символы логического умножения (произведения) пропущены.

Таблица 1.3

Логические функции двух аргументов

| № п/п | Название функции | Значения функции при значениях аргументов | Обозначение | Алгебраические формы функций | |||||

| а b | 0 | 0 | 1 | 1 | ДСНФ | КСНФ | |||

| 0 | 1 | 1 | 0 | ||||||

| V0 | Нулевая | 0 | 0 | 0 | 0 | 0 | - |

| |

| V1 | Запрет b | 0 | 0 | 0 | 1 |

a¬b |

|

| |

| V2 | Конъюнкция (И) | 0 | 0 | 1 | 0 | a&b или ab |

ab |

| |

| V3 | Повторение а | 0 | 0 | 1 | 1 | а |

|

| |

| V4 | Запрет а | 0 | 1 | 0 | 0 |

b¬a |

|

| |

| V5 | Неравнозначность | 0 | 1 | 0 | 1 |

aÅb |

|

| |

| V6 | Повторение b | 0 | 1 | 1 | 0 | b |

|

| |

| V7 | Дизъюнкция (функция ИЛИ) | 0 | 1 | 1 | 1 | a+b |

| a+b | |

| V8 | Пирса (ИЛИ-НЕ) | 1 | 0 | 0 | 0 |

|

|

| |

| V9 | Инверсия b (НЕ ) | 1 | 0 | 0 | 1 |

|

| ||

| V10 | Равнозначность | 1 | 0 | 1 | 0 |

|

|

| |

| V11 | Импликация b | 1 | 0 | 1 | 1 | b®a |

|

| |

| V12 | Инверсия а | 1 | 1 | 0 | 0 |

|

| ||

| V13 | Шеффера (И-НЕ) | 1 | 1 | 0 | 1 |

|

|

| |

| V14 | Импликация а | 1 | 1 | 1 | 0 | a®b |

|

| |

| V15 | Единичная | 1 | 1 | 1 | 1 | 1 |

| - | |

Функции-константы фактически выражают независимость от аргументов и, в то же самое время, их можно считать «функциями» от большого числа аргументов. Обратите внимание, нулевая функция не имеет ДСНФ, поскольку она никогда не принимает значение лог.1, а единичная функция не имеет КСНФ, так как она никогда не принимает значение лог.0. Отсюда следует вывод, что ДСНФ соответствует описанию (заданию) логических функций по условиям истинности (по лог.1), а КСНФ - по условиям ложности (по лог.0). Любая логическая функция, кроме функций-констант, имеет как ДСНФ, так и КСНФ. Это соответствует тому, что любое логическое устройство (сколь сложно оно ни было бы) можно описать по условиям срабатывания и по условиям несрабатывания.

Значения функций «повторения» и «инверсии» (V3, V6, V9, V12) либо повторяют значения одного из аргументов, либо принимают противоположные (инверсные) ему значения. Поэтому они и получили такие названия.

Функции инверсии чаще всего называют функциями НЕ. Эти функции реализуются логическими элементами НЕ (или инверторами). Функции повторения реализуются повторителями. Принято говорить, что функции инверсии и повторения «несущественно» зависят от второго аргумента, хотя их можно представить как функции двух, трёх и большего числа аргументов.

В технике функции «Неравнозначности» и «Равнозначности» более известны под названиями «сумма по модулю два (по mod 2)» и «инверсия суммы по mod 2» соответственно. Функции Шеффера и Пирса, соответственно, известны под названиями «инверсия логического произведения» (функции И-НЕ) и «инверсии логической суммы» (ИЛИ-НЕ). Эти функции реализуются одноимёнными по названию логическими элементами.

В булевой алгебре и в дальнейшем в логических выражениях принято обозначать функции прописными буквами латинского алфавита, а аргументы функций - строчными (малыми) буквами того же алфавита.

1.3.3. Способы и формы задания логических функцийПри описании логических устройств оказывается, что способ задания (определения) логических функций и форма их представления существенно влияют на трудность достижения конечного результата. В зависимости от поставленной цели способы задания и формы представления функций могут быть различными. Например, при построении логических устройств на программируемых постоянных запоминающих устройствах (ППЗУ) алгебраические формы логических функций нежелательны и не целесообразны. Однако при построении устройств на микросхемах малой степени интеграции, на ИМС логических элементов, требуются минимальные алгебраические формы логических функций, так как в противном случае не обеспечить минимальные аппаратурные затраты. Таким образом, выбор способа задания зависит от поставленной цели описания устройств.

Различают табличный, матричный, графический и аналитический способы задания.

При табличном задании используются так называемые «таблицы истинности» логических функций, в которых указываются значения функций на всём множестве комбинаций их аргументов. Таким образом число столбцов в таблице истинности определяется числом аргументов и числом функций, а количество строк - по формуле (1.1). Таблицы истинности используются для общего ознакомления с работой комбинационных устройств, когда число входов (аргументов функций) и число выходов (число функций) не превышает 4-х. Таблицы истинности становятся громоздкими при большем числе аргументов, а поэтому они мало пригодны для анализа. По таблицам истинности достаточно просто отыскиваются алгебраические формы функций в ДСНФ либо в КСНФ, а для поиска минимальных алгебраических форм они непригодны.

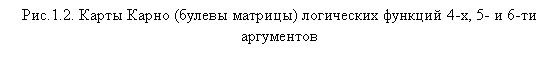

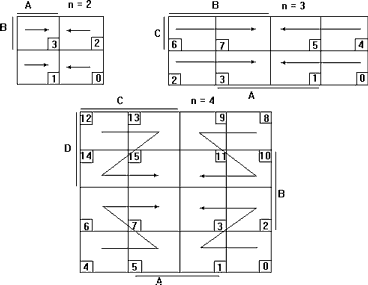

Матричный способ задания (или задание функций с помощью булевых матриц) основан на графическом отображении всего множества комбинаций аргументов функции на «плоскости» (в двумерном пространстве). Понятие «булевы матрицы» было введено А.Д. Закревским, им же был предложен визуально-матричный метод минимизации логических функций [3]. В зарубежной литературе этот способ задания и минимизации логических функций известен под названием «метода задания и минимизации с помощью карт Карно». (Не следует путать понятие «матриц», используемое в математике, с понятием «булевы матрицы»). Наряду с понятием булева матрица в дальнейшем будет употребляться понятие карта Карно, как понятия синонимы.

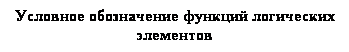

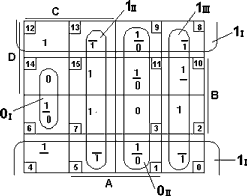

Булева матрица представляет собой прямоугольник с соотношением сторон 1:2 (при нечётном числе аргументов функции) или квадрат (при чётном числе аргументов), разделённые на элементарные квадраты (клетки). Число клеток в матрице всегда кратно степени двойки и определяется формулой (1.1). Таким образом, количество элементарных квадратов равно полному множеству комбинаций, составленных из аргументов функции. Сверху справа и слева сбоку матрицы прямоугольными скобками либо сплошной прямой линией размечаются области единичных значений аргументов (рис.1.2). Причём эти скобки помечают идентификаторами аргументов, которые размещают под скобкой либо справа (внизу) скобок. Условно считают, что область, ограниченная скобкой, является областью единичных значений аргумента, а вне этой области аргумент имеет нулевое значение. Таким образом, помеченная карта Карно, как бы «кодируется» комбинациями аргументов. При этом каждой клетке будет соответствовать одна вполне конкретная комбинация аргументов функции. Сама карта помечается идентификатором функции внизу либо справа.

Чтобы задать картой какую-либо функцию, необходимо поставить в соответствующие клетки значения этой функции (0 или 1, либо ~).

|

Так, на рис.1.2 приведены карты Карно для функций 4-х, 5-ти и 6-ти аргументов.

В частности, функции X и Y полностью определены, а функция Z недоопределена, так как наряду с фиксированными значениями 1 и 0 в клетках показаны «условные» значения, помеченные символом ~ (типографский символ - тильда). Условные значения логических функций используют в тех случаях, когда конкретные значения (0 либо 1) нельзя определить заранее. Такие случаи возникают, например, при синтезе устройств по неполностью заданным условиям, либо когда комбинации аргументов, соответствующих клеткам с символом ~ не могут возникнуть по каким-либо причинам. В процессе отыскания минимальных логических выражений недоопределённых функций, эти условные значения доопределяют значениями 1 либо 0, стараясь получить наиболее простые алгебраические выражения.

В принципе матричная форма задания логических функций более удобна для поиска минимальных алгебраических форм функций вплоть до 10 (и более) аргументов. Последовательность построения карты Карно для функций от большого числа аргументов можно уяснить, сопоставляя рис.1.2,а с рисунками 1.2,б и в.

Графический способ задания логических функций основан на использовании n-мерных кубов. Размерность куба определяется числом n аргументов функции, например, функцию от трёх аргументов можно задать 3-мерным кубом, каждая вершина которого соответствует определённой комбинации аргументов. Чтобы задать функцию с помощью 3-мерного куба, вершины куба соответствующим образом помечают. Этот способ не нашел широкого применения, и мы им пользоваться не будем.

Аналитический способ задания функций используется наиболее широко для отыскания функциональных схем синтезируемых устройств. Благодаря условным графическим обозначениям (УГО) логических элементов, существует возможность непосредственно от алгебраического выражения адекватно перейти к функциональной схеме и, наоборот, по функциональной схеме получить алгебраическое выражение функции, описывающей выходной сигнал устройства. Кроме того, пользуясь законами и следствиями алгебры логики можно выполнять эквивалентные преобразования логических выражений и, тем самым, получать новые варианты функциональных схем.

В булевой алгебре различают несколько видов алгебраических форм функций, в частности, в табл.1.3 были приведены две формы ДСНФ и КСНФ. Первая получается, когда функция определяется условиями истинности (по 1), а вторая - когда функция определяется по «нулям».

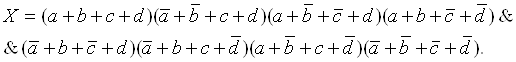

Например, функция Х, заданная картой рис.1.2,а, будет иметь следующие совершенные формы:

ДСНФ:

![]() (1.3)

(1.3)

КСНФ:

(1.4)

(1.4)

Как видно по рис.1.2,а, так и из выражений (1.3) и (1.4), следует, что функция принимает значение «1», если нечётное число аргументов принимают значение лог.1, в противном же случае она принимает значение «0». Такие функции реализуются схемами «контроля чётности/нечётности» или логическими элементами «сумма по mod2». Если использовать условное обозначение суммы по mod2 (функция неравнозначности V5 в табл.1.3), то можно записать

X = a Å b Å c Å d. (1.5)

Это выражение более короткое и оно эквивалентно выражению (1.3). Обратите внимание (рис.1.2,а), функции сумма по mod2 и её инверсии соответствует «шахматный узор» на карте Карно. Этим можно будет пользоваться в дальнейшем при поиске иных алгебраических форм логических функций. Кстати, эти функции не имеют нормальных минимальных дизъюнктивных и конъюнктивных форм - МДНФ и МКНФ.

Рассмотрим часто применяемые ИМС логических элементов, при этом будем использовать различные формы описания логических функций, реализуемых этими элементами.

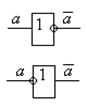

1.3.4. Логические элементы НЕЭто - наиболее простые элементы, имеющие один вход и один выход. Такие элементы описываются логической функцией отрицания, инверсии и называются просто функциями НЕ. На рис.1.3 приведены УГО элементов НЕ, рекомендуемые ГОСТом. Как видно, указатель инверсии допускается ставить либо по выходу, либо по входу логического элемента. Согласно ГОСТ можно не ставить метку основной функции «1» в основном поле УГО.

Алгебраическое выражение функции инверсии имеет вид

Х =

Х = ![]()

и читается «не а». Выходной сигнал элемента НЕ принимает всегда противоположное значение по отношению к значениям входного сигнала. Есть несколько разновидностей ИМС логических элементов, отличающихся способом организации выхода. Например, в ИМС серии К155 есть микросхемы К155ЛН1, содержащих в своём составе 4 логических элемента НЕ со стандартной нагрузочной способностью. Есть элементы НЕ с повышенной нагрузочной способностью, однако все они описываются одним и тем же логическим выражением.

и читается «не а». Выходной сигнал элемента НЕ принимает всегда противоположное значение по отношению к значениям входного сигнала. Есть несколько разновидностей ИМС логических элементов, отличающихся способом организации выхода. Например, в ИМС серии К155 есть микросхемы К155ЛН1, содержащих в своём составе 4 логических элемента НЕ со стандартной нагрузочной способностью. Есть элементы НЕ с повышенной нагрузочной способностью, однако все они описываются одним и тем же логическим выражением.

Логические элементы «повторители» так же имеют один вход и один выход, но выходной сигнал повторяет значение входного сигнала. Такие элементы используются для «развязки» выходов логических элементов и для повышения их нагрузочной способности.

1.3.5. Логические элементы ИЭти элементы реализуют функцию логического умножения (конъюнкции). Функции являются как минимум двухместными либо многоместными и описываются следующими логическими выражениями:

X = a&b = a Ù b = a·b = ab. (1.6)

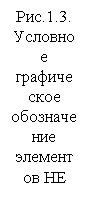

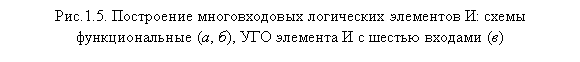

Символы конъюнкции & и Ù допускается заменять точкой, либо совсем не ставить. Выходной сигнал элемента И принимает значение лог.1 только в том случае, если все входные сигналы принимают значение лог.1. На рис.1.4 приведены условные графические обозначения и карты Карно для двухвходового (рис.1.4,а и б) и трёхвходового (рис.1.4,в и г) логического элемента И.

Рис.1.4. Условные графические обозначения элементов И: двухвходового (а),

трёхвходового (в), карты Карно логических функций 2И (б) и 3И (г)

Как видно из приведённых булевых матриц, конъюнкция равна лог.1 только в единственном случае, когда все аргументы - и первый, и второй, и третий и т.д. - одновременно принимают значение лог.1. Поэтому такие элементы называют схемами совпадения, реже встречается название «конъюнкторы», а описывающие их функции, иногда - функциями И. В сериях ИМС выпускаются различные логические элементы И, например, микросхема К155ЛИ1 содержит 4 элемента 2И (двухвходовых). Отличие заключается в разном числе входов у различных элементов.

Приведёнными на рис.1.4,б и рис.1.4,г матрицами иллюстрируются правила логического умножения, а показанные УГО соответствуют соглашениям положительной логики.

|

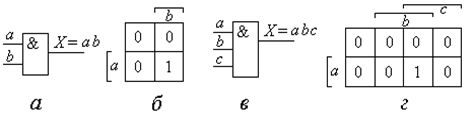

Благодаря справедливым в булевой алгебре переместительному и сочетательному законам, входы логических многовходовых элементов И являются логически равнозначными, а многовходовой логический элемент И можно получить из нескольких двухвходовых элементов И. Так, на рис.1.5 приведе

ны два варианта построения логического элемента И с шестью входами (6И) на двухвходовых элементах И (2И).

Все приведённые на рис.1.5 схемы логически эквивалентны и, в свою очередь, они эквивалентны условному графическому обозначению 6-тивходового логического элемента И (рис.1.5,в). Вместе с тем, схемы описываются различными по форме записи логическими выражениями:

X = ((((a·b)·c)·d)·k)·m ― схема рис. 1.5,а; (1.7)

Y = ((ab)·(cd))·(km) ― схема рис. 1.5,б; (1.8)

а условному обозначению элемента 6И соответствует следующее выражение:

Z = abcdkm. (1.9)

Хотя в соответствии с упомянутыми законами булевой алгебры от перемены мест сомножителей логическое произведение не меняется и скобки в выражениях логического произведения можно не ставить, тем не менее, выражения (1.7), (1.8) и (1.9) несут информацию о способах построения схем. Таким образом, указанные выражения можно считать «логико-математическими моделями» приведённых схем и в том числе УГО элемента 6И.

Следует заметить, что при описании логических комбинационных устройств с помощью булевых выражений, как правило, абстрагируются от фактора времени. Такое описание соответствует описанию устройств в статике - при установившихся значениях входных сигналов (и переменных). Считается, что изменение входных и выходных сигналов происходят мгновенно, аналогично меняются значения аргументов и значения самих логических функций. В то же самое время реальные элементы имеют конечное время перехода из одного состояния в другое или, как принято говорить, обладают конечным (не равным нулю) временем распространения сигналов от входов к выходу элемента либо устройства. С учётом сказанного, следует отдать предпочтение схеме рис.1.5,б, в которой время распространения сигналов от входов, помеченных аргументами функций, к выходу схемы в среднем меньше. В источнике [5] содержатся сведения о временных логических функциях, которые можно применять для описания схем с временными задержками.

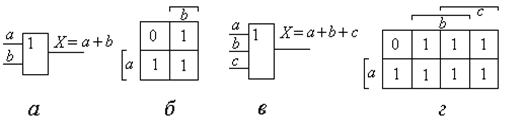

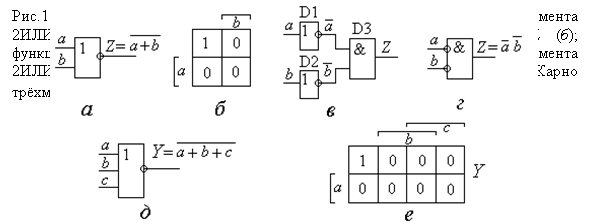

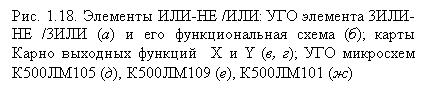

1.3.6. Логические элементы ИЛИЛогическими элементами ИЛИ реализуется логическая сумма нескольких двоичных сигналов (и входных переменных). Функция, описывающая такие элементы, называется дизъюнкцией или функцией логического сложения. На рис.1.6 приведены условные обозначения (УГО) элементов ИЛИ и карты Карно описывающих их функций.

Алгебраическое выражение логической суммы двух переменных a и b записывается следующим образом

X = a Ú b = a + b. (1.10)

В булевой алгебре для обозначения дизъюнкции используется символ Ú. В технических же её приложениях обычно применяется знак + (арифметического сложения), но только тогда, когда это не приводит к некорректности при записи формул и логических выражений. (Преимущественно этот знак будет использоваться в дальнейшем для обозначения дизъюнкции.)

Как видно из карт рис.1.6,б и рис.1.6,г, функция логического сложения принимает значение лог.0 только в единственном случае, когда все аргументы принимают значение лог.0. Значение же лог.1 она имеет, если первый аргумент или второй, или третий и т.д., или все вместе аргументы принимают значение лог.1. Поэтому эту функцию называют функцией ИЛИ.

Так же, как и к конъюнкции многих переменных, к дизъюнкции применимы переместительный и сочетательный законы булевой алгебры. И следствием этого является логическая равнозначность входов у логических элементов ИЛИ, а также возможность построения многовходовых элементов ИЛИ из аналогичных элементов, но с меньшим числом входов. Если на рис.1.5 все элементы И заменить двухвходовыми элементами ИЛИ (2ИЛИ), то все выводы, сделанные относительно схем рис.1.5, будут справедливыми для схем, полученных такой заменой. Можно так же записать логико-математические модели для полученных схем и УГО элемента 6ИЛИ, заменив в выражениях (1.7), (1.8) и (1.9) все символы логического умножения знаками + (дизъюнкции).

В различных сериях ИМС имеются логические элементы ИЛИ. Например, в серии ТТЛ это микросхема К155ЛЛ1, она содержит 4 элемента 2ИЛИ.

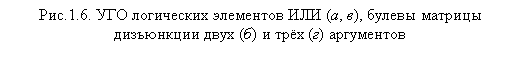

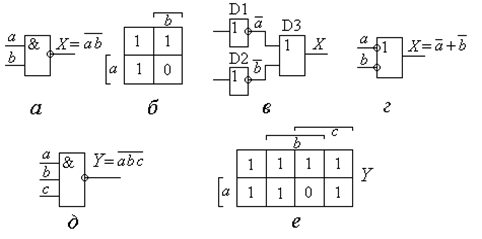

1.3.7. Логические элементы И-НЕЭти элементы реализуют инверсию логического произведения входных сигналов. Другими словами, элементы И-НЕ описываются функцией «отрицания конъюнкции». В булевой алгебре такие функции называются функциями Шеффера, для их обозначения введён специальный символ « ∕ », называемый штрихом Шеффера. Для простоты чтения мы будем использовать для обозначения функций Шеффера символ инверсии (черта вверху) над выражением конъюнкции переменных. Например, алгебраическая форма записи функции Шеффера от двух аргументов будет иметь следующий вид:

X = a / b = ![]() =

= ![]() . (1.11)

. (1.11)

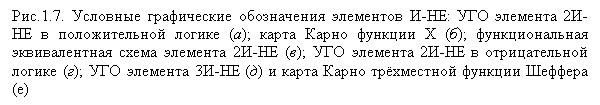

В выражении (1.11) знаки равенства соответствуют логической тождественности выражений, причём правая часть выражения соответствует КСНФ функции И-НЕ (функция V13 в табл.1.3). А в целом выражение читается так: «инверсия логического произведения равна логической сумме инверсий аргументов». Это высказывание известно в булевой алгебре как закон де Моргана относительно инверсии логического произведения (инверсии конъюнкции). На рис.1.7 приведены условные графические обозначения элемента 2И-НЕ, его функциональная эквивалентная схема и карта Карно для рассматриваемой функции. Сравнивая карты Карно функций И и функций И-НЕ, нетрудно заметить, что в клетках стоят противоположные значения названных функций. Сопоставляя карты с алгебраическими выражениями функции И и функции И-НЕ, можно сделать следующие выводы:

1. Каждой единице, стоящей в клетке матрицы, соответствует логическое произведение (конъюнкция) всех аргументов функции; взятых один раз со знаком либо без знака инверсии. Если клетка с единицей располагается на области единичных значений аргумента, то этот аргумент входит в конъюнкцию без инверсии. Если же клетка располагается на области нулевых значений аргумента, то этот аргумент входит со знаком инверсии.

2. Каждому нулю, стоящему в клетке матрицы, соответствует логическая сумма (дизъюнкция) всех аргументов функции, взятых один раз со знаком либо без знака инверсии. Если клетка с нулём располагается на области единичных значений аргумента, то этот аргумент входит в дизъюнкцию со знаком инверсии. Если же клетка располагается на области нулевых значений аргумента, то этот аргумент входит без знака инверсии.

Эти выводы носят характер правил отыскания ДСНФ (первый вывод) и КСНФ (второй вывод) по булевым матрицам логических функций. Следует только добавить, что для отыскания ДСНФ функции необходимо эти элементарные конъюнкции «соединять» символами дизъюнкции (плюс), а при отыскании КСНФ функции элементарных дизъюнкций следует соединять символами конъюнкции.

|

Под элементарной конъюнкцией логических функций понимают логическое произведение всех аргументов функции, взятых один раз со знаком либо без знака инверсии.

|

Под элементарной дизъюнкцией логических функций понимают логическую сумму всех аргументов функции, взятых один раз со знаком либо без знака инверсии.

В сериях микросхем есть элементы И-НЕ, различающиеся числом входов, количеством элементов в одной микросхеме, а также способом организации выхода. Например, микросхема К155ЛА3 содержит 4 элемента 2И-НЕ со стандартной нагрузочной способностью. Микросхема К155ЛА8 содержит один элемент 8И-НЕ с повышенной нагрузочной способностью (она равна 30, а стандартная нагрузочная способность равна 10).

Элемент 2И-НЕ является базовым для микросхем транзисторно-транзисторной логики (ТТЛ), т.е. этот элемент положен в основу построения всех названных микросхем и в том числе микросхем ТТЛш.

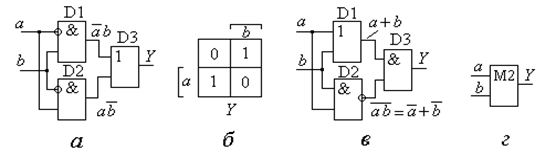

1.3.8. Элементы ИЛИ-НЕФункции, описывающие элемент 2ИЛИ-НЕ, в булевой алгебре называют функциями Пирса, для них введён специальный символ ¯ (стрелка Пирса). В технических приложениях эти функции называют «инверсией логической суммы (дизъюнкции)» или просто функциями ИЛИ-НЕ. В частности, двухместная функция Пирса, функция 2ИЛИ-НЕ имеет следующие алгебраические выражения:

Z = a ¯ b = ![]() =

= ![]() . (1.12)

. (1.12)

|

В дальнейшем эти функции будем обозначать символом инверсии над выражением логической суммы. Правая часть выражения (1.12) соответствует утверждению, что «инверсия логической суммы есть в то же самое время логическое произведение слагаемых, взятых с противоположными символами инверсии». Это утверждение является вторым законом де Моргана относительно инверсии дизъюнкции. Согласно выражению (1.12), элемент 2ИЛИ-НЕ можно представить условными графическими обозначениями при соглашениях положительной логики, при соглашениях отрицательной логики и функциональной эквивалентной схемой (рис.1.8).

В интегральном исполнении выпускаются логические элементы ИЛИ-НЕ с различным числом входов. Примером может служить микросхема К155ЛЕ1, содержащая 4 логических элементов 2ИЛИ-НЕ, или К155ЛЕ3 с двумя элементами 4ИЛИ-НЕ. Как и у элементов ИЛИ, так и у элементов ИЛИ-НЕ все входы логически равнозначны.

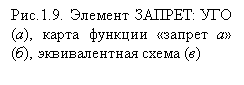

1.3.9. Элементы «ЗАПРЕТ»Эти двухвходовые элементы получили такое название потому, что сигнал по одному из входов «запрещает» либо «разрешает» прохождение на выход элемента сигнала, поданного на второй вход. Поэтому один вход называется входом запрета - он инверсный, а второй вход называют «информационным». Значения выходного сигнала совпадают со значениями входного информационного сигнала в состоянии разрешения, а в состоянии запрета выходной сигнал имеет значение лог.0 независимо от значения сигнала по информационному входу. В табл.1.3 показаны две функции запрета V1 (запрет b) и функция V4 (запрет а). На рис. 1.9 приведены УГО элемента «запрет а» (запрет по а), алгебраическое выражение и карта Карно функции с аналогичным названием и функциональная эквивалентная схема элемента.

При а = 0 значения функции Z совпадают со значением аргумента b.

Если а = 1 (состояние запрета) на выходе элемента будет постоянно сигнал лог.0. Таким образом, вход а является входом запрета, а вход b - информационным. Очевидно, такое же УГО будет соответствовать элементу «запрет b» только вход b будет инверсным, а вход а будет прямым. Аналогично в алгебраическом выражении такой функции аргумент b будет со знаком инверсии, аргумент же а войдёт без знака инверсии.

Следует отметить, что у элементов ЗАПРЕТ входы логически неравнозначны. Это в свою очередь означает, что сигналы по входам нельзя менять «местами».

Логические элементы ЗАПРЕТ выпускаются в интегральном исполнении, но не во всех сериях. Например, в серии К161 (на МОП-транзисторах с р-каналом) есть микросхема К161ЛП2, содержащая 4 элемента ЗАПРЕТ с общим входом запрета. На рис.1.9,а приведено условное графическое обозначение (УГО), соответствующее соглашениям положительной логики. Можно составить УГО при соглашениях отрицательной логики. Для этого над правой частью алгебраического выражения функции надо «взять» двойной знак инверсии, затем один знак раскрыть по закону де Моргана:

![]() =

= ![]() . (1.13)

. (1.13)

Таким образом, при соглашениях отрицательной логики аналог УГО элемента ЗАПРЕТ будет представлять собой УГО элемента 2ИЛИ-НЕ, только по одному из входов следует поставить указатель инверсии.

1.3.10. Логические элементы «сумматоры по mod2» исхемы контроля чётности /нечётности

Логическая функция V5 «неравнозначность» (табл.1.3) принимает значение лог.1 только тогда, когда нечётное число аргументов принимают значение лог.1. Поскольку функции и аргументы могут принимать только два значения, то эта функция равносильна операции сложения по модулю два (mod2) над двоичными числами, отображающими двоичные наборы значений аргументов. Для обозначения этой операции используется символ Å между аргументами. Эти функции, как минимум двухместные, однако, могут быть многоместными, т.е. зависеть от большего числа аргументов.

Алгебраические формы записи функции сложения по mod2 от двух аргументов имеют следующий вид:

Y = a Å b = ![]() . (1.14)

. (1.14)

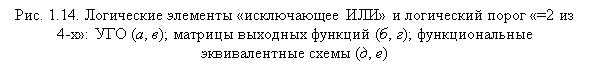

Правые части выражения (1.14) представляют собой ДСНФ и КСНФ, соответственно. В соответствии с этими формами можно построить функциональные эквивалентные схемы сумматора по mod2 с двумя входами. Эти схемы, а также УГО, рекомендованное ГОСТом, и булева матрица этой функции приведены на рис.1.10.

|

Обратите внимание, в схеме рис.1.10,а использованы УГО элементов запрета и элемент 2ИЛИ. В схеме рис.1.10,в для реализации дизъюнкции инверсий аргументов применён элемент 2И-НЕ и, кроме того, элементы 2ИЛИ и 2И. Приведённые схемы лишний раз показывают, что функциональных схем для двухвходового сумматора по mod2 можно составить несколько!

Выше, на рис.1.2,а, в качестве примера была приведена карта Карно 4-местной функции сложения по mod2. Она может быть реализована 4-входовым сумматором по mod2 с условным графическим обозначением, аналогичным рис.1.10,г (должно быть 4 входа). Так как от перемены мест слагаемых сумма по mod2 не меняется, то все входы у сумматоров по mod2 логически равнозначны. Заметим ещё раз! Что если число входных сигналов, принявших значение лог.1, чётное, то выходной сигнал сумматора по mod2 будет равен лог.0, т.е. имеет неактивное значение, - чётность «не нарушена». Поэтому такие элементы получили название «схем контроля чётности».

Обратите теперь внимание на функцию V10 - функцию логической равнозначности, (табл.1.3). Она принимает противоположные значения по сравнению с суммой по mod2, то есть является её инверсией. Поэтому условное графическое обозначение элемента, её реализующего, будет отличаться от рис.1.10,г лишь наличием указателя инверсии на выходе элемента.

Используя алгебраические выражения двухместной функции равнозначности (1.15), можно получить функциональные эквивалентные схемы двухвходового сумматора по mod2 с инверсным выходом (2Å-НЕ).

X = ![]() =

= ![]() =

= ![]() . (1.15)

. (1.15)

Карта Карно этой функции будет отличаться от карты рис.1.10,б тем, что в клетки следует ставить противоположные значения (нули заменить единицами, а единицы − нулями). Нетрудно установить смысловое значение этой функции, поскольку она принимает значение лог.1 при чётном числе и значение лог.0 при нечётном числе единичных значений её аргументов. Схемы же её реализующие получили название «схем контроля нечётности».

![]()

В интегральном исполнении выпускаются логические элементы 2Å, например, микросхема К155ЛП5 содержит 4 таких элемента.

В интегральном исполнении выпускаются логические элементы 2Å, например, микросхема К155ЛП5 содержит 4 таких элемента.

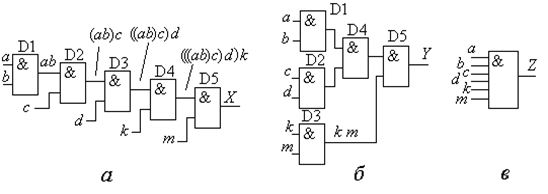

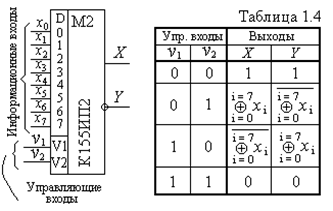

Есть микросхемы, выполняющие функцию многовходового сумматора по mod2 с прямым и инверсным выходом. Например, микросхема К155ИП2 является 8-разрядной схемой контроля чётности/ нечётности с прямым и инверсным выходом и с двумя управляющими входами. Такой микросхемой реализуются одновременно функция 8Å и функция 8Å-НЕ. Условное графическое обозначение этой микросхемы и таблица, описывающая режимы работы ИМС, приведены на рис.1.11.

В табл.1.4, в столбцах значений выходных сигналов X и Y, приведены сокращённые алгебраические выражения одноимённых выходных функций. Из этих выражений следует, что при комбинации сигналов на управляющих входах v1 =0 и v2 =1 на выходе X будет реализована сумма по mod2 всех восьми информационных сигналов. В то же самое время на выходе Y будет реализована инверсия этой суммы. Кроме того, из таблицы видно, что при комбинациях сигналов на управляющих входах 0-0 либо 1-1 микросхема оказывается в «нерабочем» состоянии, когда на обоих выходах сигналы принимают одинаковые значения независимо от значений входных информационных сигналов.

1.3.11. Мажоритарные логические элементыЭти элементы описываются логическими функциями, у которых число аргументов больше двух и является нечётным. Соответственно у любого мажоритарного элемента число входов всегда нечётное. Выходной сигнал принимает активное значение, когда большинство входных сигналов принимают активные значения. Поэтому такими элементами реализуется «принцип большинства» в обработке или в приёме сигналов.

Допустим, что за активное значение входных и выходного сигналов принят уровень лог.1. Тогда у мажоритарного элемента «³ 2 из 3-х» (с тремя входами) сигнал на выходе будет равен лог.1, если два (любых) либо все три входных сигнала принимают значение лог.1.

На рис.1.12 приведены УГО такого элемента, карта Карно выходной функции и функциональная его эквивалентная схема.

По карте функции F можно найти её минимальную дизъюнктивную нормальную форму (МДНФ):

F = ab + bc + ac. (1.16)

Этой формулой непосредственно описывается схема рис.1.12,б. Как видно по карте Карно (рис.1.12,в), единицы стоят в клетках, расположенных на областях единичных значений двух и всех трёх аргументов. По аналогии можно построить карту Карно для мажоритарного элемента «³3 из 5-ти», найти минимальное алгебраическое выражение его выходной функции, а затем построить функциональную схему.

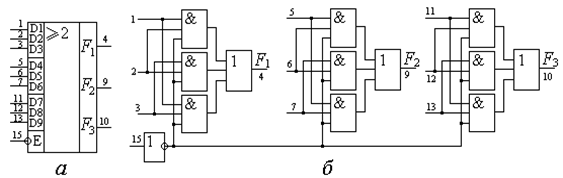

В интегральном исполнении мажоритарные элементы есть, но не во всех сериях. Например, в серии КР1533 есть микросхема КР1533ЛП3, представляющая собой три мажоритарных элемента «³2 из 3-х» с инверсным общим входом управления. Сигнал лог.0 по входу управления разрешает выполнение функций мажоритарности, а сигнал лог.1 запрещает их реализацию. Функциональная схема этой микросхемы и её УГО приведены на рис.1.13. Сопоставляя функциональную схему рис.1.13,б со схемой мажоритарного элемента рис.1.12,б, можно понять, как организовано управление, и какие значения принимают выходные сигналы при подаче на управляющий вход (он помечен на УГО меткой «Е») сигнала лог.1. (На УГО и соответственно на схеме рис.1.13,б цифры означают номера выводов микросхемы.)

![]()

Есть мажоритарные элементы с инверсным выходом, например, микросхемы 533ЛП3 и КР134ЛП3 содержат по три таких элемента. В этом случае принцип «большинства» будет реализован относительно сигналов низкого уровня (сигналов лог.0). Следует также заметить, у мажоритарных элементов, как и у элементов И-НЕ и ИЛИ-НЕ, все входы логически равнозначны, т.е. порядок подачи входных сигналов не имеет существенного значения.

1.3.12. Элементы «логического порога» и элементы«исключающее ИЛИ»

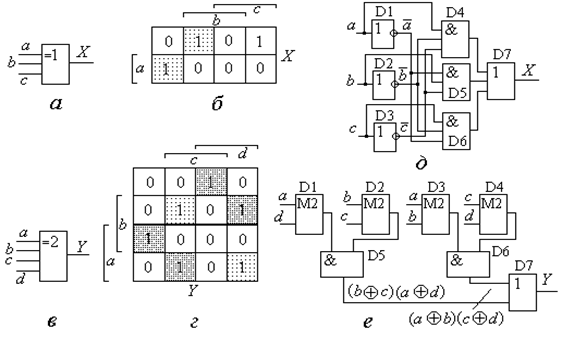

Среди многовходовых логических элементов можно выделить группу элементов, у которых выходной сигнал принимает активное значение только в тех случаях, когда определённое заданное число входных сигналов также принимают активное значение. Такие элементы принято называть элементами «логического порога». В частности, если выходной сигнал принимает значение лог.1, когда только один и только один из входных сигналов принимает значение лог.1, то такие элементы называют элементами «исключающее ИЛИ». Это тоже элементы логического порога, только «порог» равен единице. Для них ГОСТами также регламентировано УГО, в основное поле которого помещается метка «=1» (для элементов исключающее ИЛИ), либо метка вида «=n», где n целое число меньше числа входов у логического элемента.

Так, на рис.1.14 приведены УГО элемента исключающее ИЛИ с тремя входами, УГО элемента логического порога «=2 из 4-х», карты Карно их выходных функций и функциональные эквивалентные схемы.

Анализируя приведённые карты Карно функций X и Y, замечаем, что

|

минимальных дизъюнктивных алгебраических форм у этих функций нет (о визуально-матричном способе минимизации логических функций будет сказано ниже). Поэтому функциональные схемы названных элементов можно построить, найдя алгебраические выражения в ДСНФ либо в других формах.

Так, схема рис.1.14,д получена по следующему выражению:

|

X =

Это ДСНФ функции «исключающее ИЛИ». Если бы аналогично находить выражение функции Y, то оно состояло бы из 6 дизъюнктивных членов (слагаемых), каждый из которых представлял бы произведение всех 4-х аргументов. Тогда функциональная схема элемента логического порога «=2 из 4-х» состояла бы из элемента 6ИЛИ, шести логических элементов 4И и из 4-х элементов НЕ. Схема же на рис.1.14,е получена по следующему логическому выражению:

Y = (aÅd)(bÅc) + (aÅb)(cÅd). (1.18)

О правилах получения подобного рода алгебраических выражений по булевым матрицам логических функций речь будет идти ниже. Сейчас же уместно напомнить, что сумма по mod2 отображается на картах Карно шахматным узором расположения единиц и нулей. Так, выражение (1.18) получено по выделенным различной заливкой «частным шахматным узорам» (рис.1.14,г) для функции Y с применением операции выноса за скобки общих сомножителей. Аналогичное выражение можно было бы получить и для функции «исключающее ИЛИ» по карте рис.1.14,б.

Следует отметить, что в частном случае, когда число входов у элемента «исключающее ИЛИ» равно двум, то эта функция тожественно равна функции сложения по mod2 от двух аргументов (2Å). К сожалению, в интегральном исполнении логические элементы «исключающее ИЛИ» и «логического порога» при числе входов более двух не выпускаются.

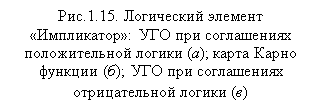

1.3.13. Логические элементы «ИМПЛИКАТОРЫ»Эти логические элементы описываются функцией «импликация» (табл.1.3 функции V11 и V14).

![]() V11 = b ® a =

V11 = b ® a = ![]() ,

,

V14 = a ® b = ![]() . (1.19)

. (1.19)

Первая из функций называется «импликация b», а вторая - «импликация а». На рис.1.15 приведены условные графические обозначения логического элемента ИМПЛИКАТОР а и карта Карно его выходной функции. Правые части выражений (1.19) свидетельствуют о том, что функция импликации в то же самое время является инверсией функции ЗАПРЕТ.

Из карты рис.1.15,в следует, что функция импликации ложна только в том случае, когда один из аргументов принимает ложное значение, а другой - истинное.

В интегральном исполнении ИМПЛИКАТОРЫ в сериях ИМС широкого применения практически не выпускаются. Вместе с тем, согласно УГО рис.1.15,а и в, функцию импликации можно реализовать элементом 2ИЛИ, подав сигнал на его один из входов через инвертор, либо - на элементе ЗАПРЕТ, включив на его выход инвертор. Эти функциональные эквивалентные схемы мы не приводим, из-за их тривиальности.

В интегральном исполнении ИМПЛИКАТОРЫ в сериях ИМС широкого применения практически не выпускаются. Вместе с тем, согласно УГО рис.1.15,а и в, функцию импликации можно реализовать элементом 2ИЛИ, подав сигнал на его один из входов через инвертор, либо - на элементе ЗАПРЕТ, включив на его выход инвертор. Эти функциональные эквивалентные схемы мы не приводим, из-за их тривиальности.

Следует отметить, что входы у логических элементов импликаторов логически неравнозначны, поэтому порядок подачи входных сигналов строго фиксирован.

1.3.14. Многофункциональные логические элементыВыше были рассмотрены «простые» логические элементы, которые реализуют простые либо достаточно простые логические операции. Вместе с тем, в интегральном исполнении выпускаются более сложные логические элементы (ЛЭ), которые способны реализовать (одновременно, либо путём перекоммутации входов к шинам лог.0 или лог.1) несколько простых функций. По сути, эти элементы допускают возможность реализации многоместных логических функций по фрагментам их нормальных дизъюнктивных, либо нормальных конъюнктивных алгебраических форм. В табл.1.2 уже были приведены названия интегральных схем по функциональному назначению и их условные обозначения. Рассмотрим только наиболее широко применяемые многофункциональные ЛЭ.

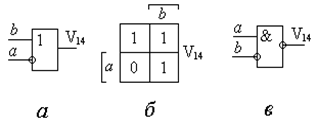

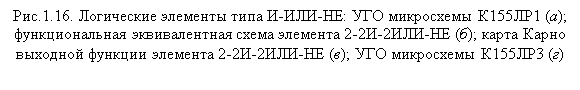

Логические элементы И-ИЛИ-НЕ |

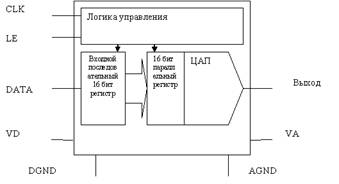

Такие элементы реализуют инверсию дизъюнктивных нормальных форм (ДНФ) алгебраических выражений функций, что эквивалентно реализации конъюнктивных нормальных форм (КНФ) этих функций. Так, на рис.1.16 приведены УГО микросхем К155ЛР1 и К155ЛР3. В микросхеме К155ЛР1 содержится два элемента 2-2И-2ИЛИ-НЕ, а микросхема К155ЛР3 представляет собой один элемент 2-2-2-3И-4ИЛИ-НЕ, расширяемый по ИЛИ.

|

По функциональной схеме (рис.1.16,б) одного из элементов микросхемы К155ЛР1 можно составить следующее алгебраическое выражение его выходной функции:

F = ![]() =

= ![]() . (1.20)

. (1.20)

Таким образом, эта функция от 4-х аргументов, причём правая часть выражения (1.20) соответствует минимальной конъюнктивной нормальной форме функции F (МКНФ). Левая часть этого выражения непосредственно соответствует УГО элемента 2-2И-2ИЛИ-НЕ. Второй такой же элемент этой микросхемы имеет «нелогические» входы расширения по ИЛИ. Они помечены в левом дополнительном поле УГО метками «э» - эмиттера вывод и «к» - коллектора вывод. Нелогическими выводами (входы либо выходы) принято называть такие, на которых сигналы могут принимать значения нестандартных уровней напряжения. Такие выводы помечаются на УГО логических элементов (либо микросхем) специальным указателем в виде «крестика» ´. В частности, у рассматриваемых ИМС эти выводы выполнены от коллектора и эмиттера транзистора фазорасщепляющего каскада базового логического элемента серий ИМС ТТЛ. Подключая к ним выходы соответствующих ИМС «расширителей по ИЛИ», можно наращивать число входов элемента ИЛИ-НЕ, входящего в состав многофункционального элемента. Например, для рассматриваемых микросхем коэффициент объединения по входу равен 8, а расширители по ИЛИ реализуют логическое произведение нескольких входных сигналов. По существу расширители по ИЛИ являются многовходовыми элементами И с той лишь разницей, что выходные сигналы не имеют стандартных уровней лог.0 и лог.1. Отмеченное позволяет записать по аналогии с выражением (1.20) алгебраическое выражение выходной функции V для второго элемента:

V = ![]() . (1.21)

. (1.21)

Максимальное число последующих слагаемых в выражении (1.21) может быть равным 8 (в соответствии с коэффициентом объединения по входам), а каждое слагаемое может быть отображено конъюнкцией максимально от восьми аргументов. Таким образом, выражения (1.20) и (1.21) определяют логико-математическую модель микросхемы К155ЛР1.

Предлагаем Вам самостоятельно найти логико-математическую модель микросхемы К155ЛР3, используя для этого показанное на рис.1.16,г её условное графическое обозначение.

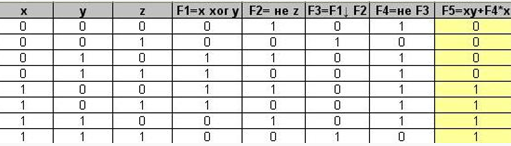

Логические элементы ИЛИ-ИЭти логические элементы реализуют фрагменты конъюнктивных нормальных форм (КНФ) булевых функций, то есть логическое произведение логических сумм от нескольких аргументов. Например, самым простым будет элемент 2-2ИЛИ-2И. Такой элемент описывается функцией вида

X = (a + b)(c + d). (1.22)

На рис.1.17 приведено УГО этого элемента, карта Карно его выходной функции X и функциональная эквивалентная схема.

В интегральном исполнении выпускаются подобные ЛЭ, например, в серии ИМС ЭСЛ есть микросхема К500ЛС118, представляющая собой два логических элемента 2-3ИЛИ-2И с одним общим входом. На рис.1.17,г показано УГО этой микросхемы. По условному её графическому обозначению можно составить следующие логические выражения выходных функций Y и Z:

![]() Y = (x1 + x2 + x3)(x4 + x5 + x6), (1.23)

Y = (x1 + x2 + x3)(x4 + x5 + x6), (1.23)

Z = (x6 + x7 + x8)(x9 + x10 +x11).

Выражения (1.23) являются логико-математической моделью рассматриваемой микросхемы. Наличие общего входа x6 даёт возможность использовать микросхему К500ЛС118 в качестве двух независимых элементов вида 2-3ИЛИ-2И (при x6=0),

либо в качестве двух независимых элементов 3ИЛИ (при x6 =1). В этом легко убедиться, подставив соответствующие значения x6 в выражения (1.23).

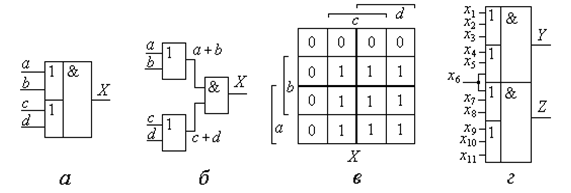

Логические элементы ИЛИ-НЕ / ИЛИПо существу, эти элементы являются элементами ИЛИ с двумя выходами - прямым и инверсным. Поэтому они реализуют одновременно дизъюнкцию и инверсию дизъюнкции от одного и того же множества входных сигналов и описываются одноимёнными логическими функциями. Так на рис.1.18,а показано УГО элемента 3ИЛИ-НЕ / 3ИЛИ и условные графические обозначения микросхем серии К500, содержащих подобные логические элементы. На рисунке также приведены карты Карно выходных функций указанного элемента, функциональная эквивалентная его схема (рис.1.18,б) и УГО микросхем К500ЛМ105 (рис.18,д), К500ЛМ109 (рис.1.18,е) и К500ЛМ101 (рис.1.18,ж). Следует отметить, приведённый вариант функциональной схемы не единственный - вместо элемента 3ИЛИ-НЕ может быть использован элемент 3ИЛИ и также элемент НЕ. По условным графическим обозначениям перечисленных микросхем нетрудно уяснить, что ИМС К500ЛМ105 содержит три независимых элемента: два элемента 2ИЛИ-НЕ/ 2ИЛИ и один элемент 3ИЛИ-НЕ /3ИЛИ.

Аналогично можно уяснить состав микросхемы К500ЛМ109

Аналогично можно уяснить состав микросхемы К500ЛМ109

(рис.1.18,е).

Обратите внимание на УГО микросхемы К500ЛМ101(рис.1.18,ж). Микросхема содержит 4 однотипных элементов типа 2ИЛИ-НЕ /2ИЛИ с раздельными выходами и с одним общим входом х5. Если сигнал по этому входу х5 = 0, то микросхему можно рассматривать как набор из 4-х элементов НЕ и, в то же самое время, как набор из четырёх повторителей сигналов по входам х1, х2, х3 и х4. Если же х5 = 1, то независимо от значений других входных сигналов на прямых выходах установятся сигналы лог.1, а на инверсных выходах сигналы лог.0. Таким образом, каждый элемент в микросхеме играет роль управляемого инвертора-повторителя.

Дополнительно отметим, что в серии К500 имеются логические элементы вида ИЛИ-И-НЕ/ИЛИ-И, например микросхема К500ЛК117. Это - практически, аналог микросхемы К500ЛС118 (рис.1.17,г) с тем отличием, что каждый элемент 2-2ИЛИ-2И имеет прямой и инверсный выходы.

Мы рассмотрели практически все широко используемые при построении цифровых устройств логические элементы. Анализируя изложенный материал, можно придти к следующим выводам:

1. Существует возможность однозначного перехода от аналитического описания ЛЭ к его условному графическому обозначению либо к функциональной эквивалентной его схеме.

2. Существует возможность однозначного перехода от УГО элемента либо от его функциональной схемы к аналитическому его описанию. При этом функционирование элемента описывается алгебраическими выражениями логических функций, реализуемых элементом.

3. Функциональные схемы сложных ЛЭ можно построить на различных более простых (менее сложных) логических элементах, причём существует неоднозначность (многовариантность) построения функциональных эквивалентных схем для одного и того же ЛЭ.

Поскольку логические устройства по существу представляют собой совокупность взаимосвязанных логических элементов, то сформулированные выводы можно с успехом распространить и на устройства.

Вместе с тем возникает проблема, - каким образом можно построить устройство с минимальным количеством ЛЭ и на элементах минимальной номенклатуры. Другими словами, как построить устройство с минимальными аппаратурными затратами.

Решение этой проблемы основывается на знании функционально полных наборов логических элементов и выборе по определённым критериям соответствующего набора.

1.3.15. Функционально полные наборы логических элементовФункционально полным называется такой набор ЛЭ, на которых (из которых) можно построить любое логическое устройство сколь сложно оно ни было бы. Функциональная полнота некоторого набора логических элементов, в свою очередь, определяется полнотой некоторой системы логических функций, которые являются логико-математическими моделями выбранного набора ЛЭ.

В булевой алгебре существует теорема Поста-Яблонского, согласно которой устанавливаются критерии полноты некоторой системы логических функций. Сущность этой теоремы сводится к следующему.

Некоторая система логических функций будет полной, если она содержит:

а) функцию, не сохраняющую логическую константу 0,

f (x1, x2, ¼xn) = f (0, 0, ¼0) ¹ 0;

б) функцию, не сохраняющую логическую константу 1,

f (x1, x2, ¼xn) = f (1, 1, ¼1) ¹ 1;

в) функцию, не являющуюся самодвойственной,

![]() ¹

¹ ![]() ;

;

г) функцию, не являющуюся линейной,

f (x1, x2, ¼xn) ¹ х1 Å х2 Å ¼Å хn Åх1 х2 Å ¼ Å х1 х2¼xn;

д) функцию, не являющуюся монотонной.

Если Х1 есть некоторый фиксированный набор значений аргументов функции f (x1,x2,x3,x4), например Х1 = <x1, x2, x3, x4> = <1,1,0,1>, а Х2 = <x1, x2, x3, x4> = <0,0,0,1> - другой набор этих аргументов, то можно считать, что Х1 > Х2, т.е. набор Х2 меньше набора Х1.

Похожие работы

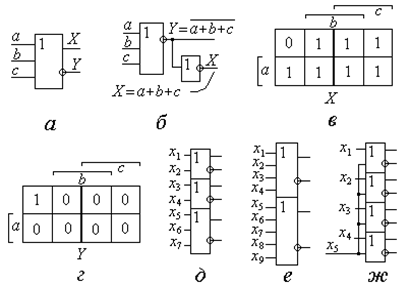

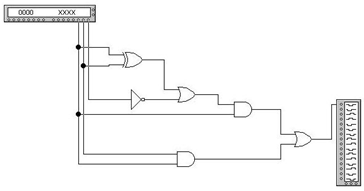

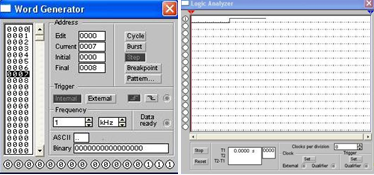

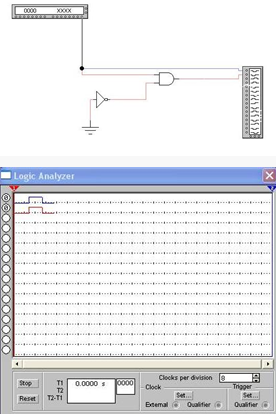

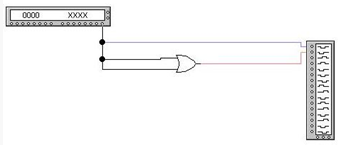

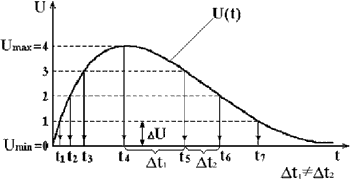

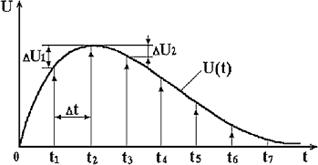

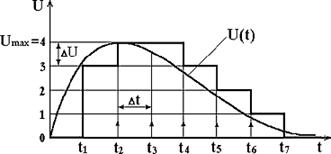

... Поглощение 17 F17=X1+X1’*X2=X1+X2 Поглощение 18 F18=(X1*X2)’=X1’+X2’ 1 правило де Моргана 19 F19=(X1+X2)’=X1’*X2’ 2 правило де Моргана Задание 3 Спроектировать цифровую схему, выполняющая указанные действия и состоящую из простейших элементов И, ИЛИ, НЕ. Результаты подтвердить построением таблицы истинности и соответствующими временными диаграммами. Спроектировать цифровую схему ...

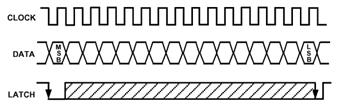

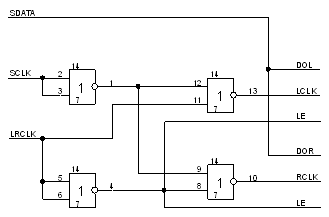

... показана на рисунке 8.4 Величина резистора R выбирается из условия [12] 240 Ом < R < 1,5 кОм.(8.5) Рисунок 8.4 Период генерируемых импульсов (8.6) 9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ 9.1 Комбинационные цифровые устройства (КЦУ) Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических ...

... и цифровых микросхем, аналого-цифрового преобразователя, коммутатора измерительных каналов и, при необходимости, измерительных преобразователей. Блок-схема алгоритма функционирования цифрового регистрирующего устройства, составленная в соответствии с изложенным словесным алгоритмом, представлена на рис. 2 Выбор схемотехнического решения блока цифровой индикации Разрядность цифровых счетных ...

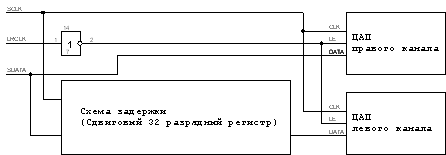

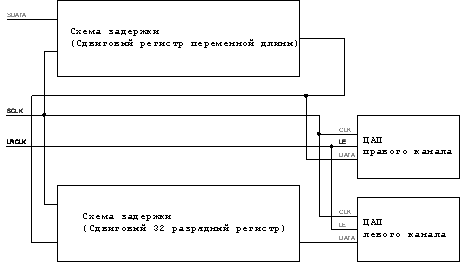

... 5 V, имеет смысл выделить для них отдельный источник питания, а не использовать один источник для схемы разделения цифрового потока и ЦАП одновременно. Это позволит уменьшить уровень помех, проникающих из цифровой части микросхемы ЦАП в аналоговую часть устройства и улучшит звучание системы. Часть 3. Временные диаграммы 3.1 Временная диаграмма работы устройства разделения данных для ...

0 комментариев