Навигация

Проектирование узла цифрового комбинационного устройства

Реферат

1 Получение канонических форм

1.1 Совершенная дизъюнктивная форма

1.2 Совершенная конъюнктивная форма

1.3 Составление схемы СДНФ

1.4 Составление схемы СКНФ

2 Минимизация логической функции методом Квайна

3 Минимизация логической функции методом Квайна - Мак-Класки

4 Минимизация методом карт Вейча

Заключение

Библиографический список

Реферат

Разработка узла цифрового комбинационного устройства. Курсовая работа / ВятГУ, каф. РЭС; рук. Н.А. Краев. - Киров, 2007. ПЗ 18 с., табл.10, источников 2 ,схем 6.

СОВЕРШЕННАЯ ДИЗЪЮНКТИВНАЯ НОРМАЛЬНАЯ ФОРМА, СОВЕРШЕННАЯ КОНЪЮНКТИВНАЯ НОРМАЛЬНАЯ ФОРМА, МИНИМАЛЬНАЯ ДИЗЪЮНКТИВНАЯ НОРМАЛЬНАЯ ФОРМА, МИНИМАЛЬНАЯ КОНЪЮНКТИВНАЯ НОРМАЛЬНАЯ ФОРМА, МЕТОД КВАЙНА, МЕТОД КВАЙНА-МАК-КЛАСКИ, МЕТОД КАРТ ВЕЙЧА, БАЗИСНЫЕ ЭЛЕМЕНТЫ И, ИЛИ, НЕ.

Цель работы - проектирование узла цифрового комбинационного устройства.

Составление модели проектируемого устройства с помощью программы Electronics Workbench.

Научная новизна отсутствует.

В результате получили канонические формы представления логической функций, осуществлена минимизация методами Квайна, Квайна-Мак- Класки и карт Вейча, был спроектирован узел цифрового комбинационного устройства. Расчеты были подтверждены моделированием в программе Electronics Workbench. Данная работа может использоваться в качестве пособия, как пример, при изучении методов минимизации логических функций.

1. Получение канонических форм

Логическая функция задана следующей таблицей истинности:

Таблица 1

| Х1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Х2 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Х3 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Х4 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| F(Х) | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

Похожие работы

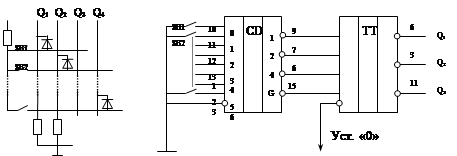

... и цифровых микросхем, аналого-цифрового преобразователя, коммутатора измерительных каналов и, при необходимости, измерительных преобразователей. Блок-схема алгоритма функционирования цифрового регистрирующего устройства, составленная в соответствии с изложенным словесным алгоритмом, представлена на рис. 2 Выбор схемотехнического решения блока цифровой индикации Разрядность цифровых счетных ...

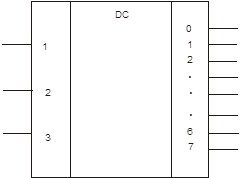

... дешифратор 3x8, а в качестве шифратора – диодный матричный шифратор. Рис.6.Схема, реализующая преобразование 3-элементного кода в 5-элементный Мультиплексоры. Мультиплексором (MS) называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации ...

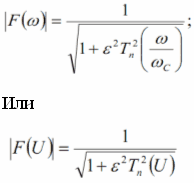

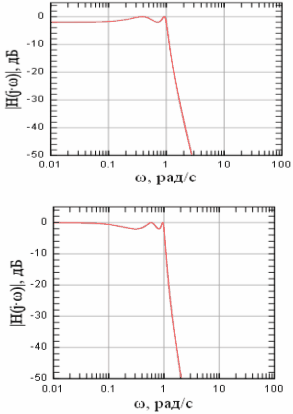

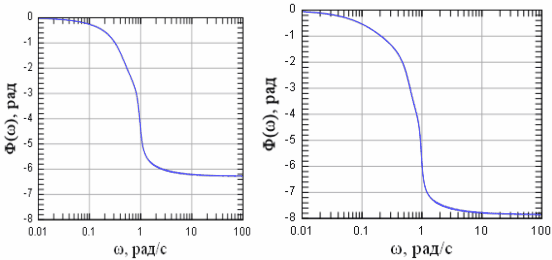

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

... И-НЕ. Для выполнения этой операции (при имеющемся в окошке булевом выражении) следует “нажать” стрелкой кнопку: 3. Математические модели и эквивалентные схемы в программе логического проектирования Любой реальный логический элемент(ЛЭ) не мгновенно реагирует на изменения входных сигналов, поэтому имеется некоторая паразитная задержка между моментом времени, в который на его входы поступают новые ...

0 комментариев