Навигация

1.4 Составление схемы СКНФ

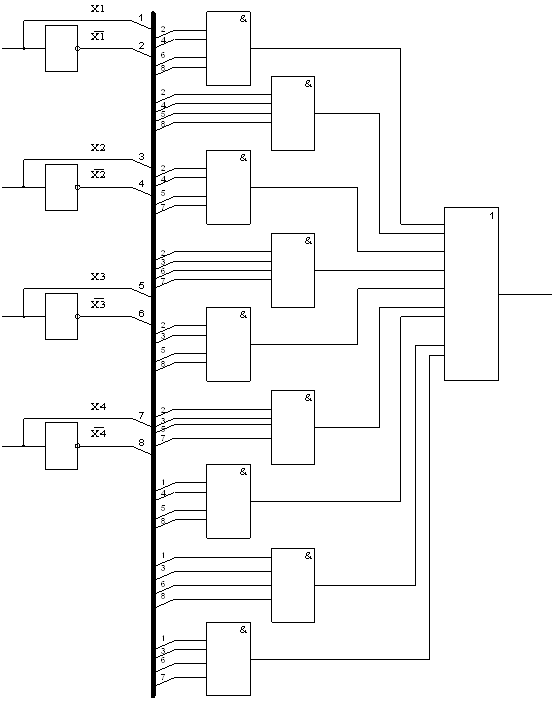

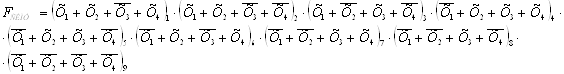

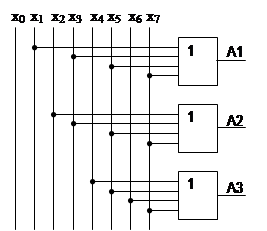

Составляем схему полученной СКНФ с помощью базисных элементов И, ИЛИ, НЕ:

Рисунок 2 – Схема полученной СКНФ

2. Минимизация логической функции методом Квайна

Метод основан на операциях склеивания и поглощения. Операция склеивания производится по правилу: Z(X+X) = Z, где Z произвольная комбинация символов. Операция поглощения выполняется по правилу: М(1+Х)=М. Сначала выполняется операция склеивания, затем операция поглощения. При поглощении из логического выражения удаляются все члены, поглощенные членами, полученными при склеивании.

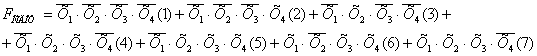

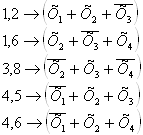

Находим МДНФ (минимальную дизъюнктивную нормальную форму). Для этого с помощью операции склеивания из СДНФ сначала получаем сокращенную форму:

Здесь и далее индексы в скобках — это порядковые номера минтерм, которые используются для большей наглядности проводимых преобразований.

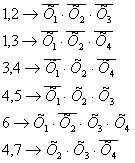

Выполним операцию попарного склеивания:

Получили сокращенную форму, строим импликантную матрицу:

Таблица 2

| Простые импликанты | Члены СДНФ |

| ||||||

|

|

|

|

|

|

|

| ||

|

| Х | Х | ||||||

|

| Х | Х | ||||||

|

| Х | Х | ||||||

|

| Х | Х | ||||||

|

| Х | |||||||

|

| Х | Х | ||||||

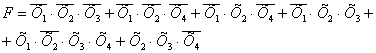

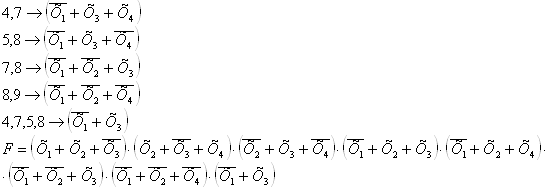

В левом столбце таблицы 2 записываем члены сокращенной формы (простые импликанты), в верхней строке – члены СДНФ. В минимальную форму войдут те члены сокращенной формы, с помощью которых можно представить все члены СДНФ. Из матрицы видно, что не все члены сокращенной формы войдут в минимальную ДНФ:

![]()

Находим МКНФ (минимальную конъюнктивную нормальную форму).

Здесь и далее индексы - это порядковые номера макстермов, которые введены для большей наглядности проводимых преобразований.

Далее выполним операцию попарного склеивания:

Таблица 3 - Импликантная матрица

|

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | |

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | |||||||

|

| Х | Х | Х | Х |

![]()

Похожие работы

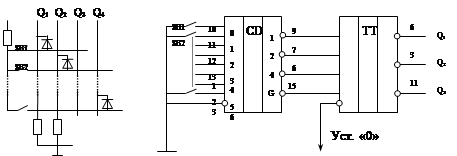

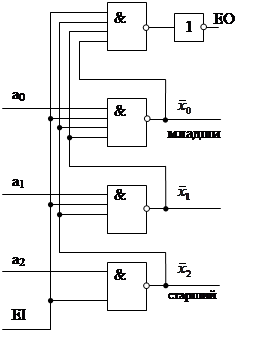

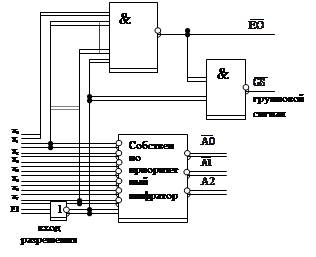

... и цифровых микросхем, аналого-цифрового преобразователя, коммутатора измерительных каналов и, при необходимости, измерительных преобразователей. Блок-схема алгоритма функционирования цифрового регистрирующего устройства, составленная в соответствии с изложенным словесным алгоритмом, представлена на рис. 2 Выбор схемотехнического решения блока цифровой индикации Разрядность цифровых счетных ...

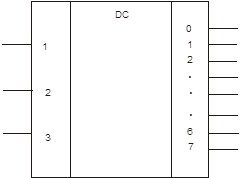

... дешифратор 3x8, а в качестве шифратора – диодный матричный шифратор. Рис.6.Схема, реализующая преобразование 3-элементного кода в 5-элементный Мультиплексоры. Мультиплексором (MS) называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации ...

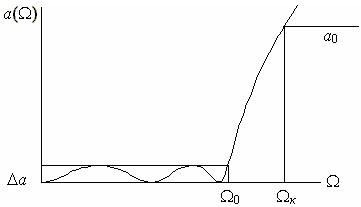

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

... И-НЕ. Для выполнения этой операции (при имеющемся в окошке булевом выражении) следует “нажать” стрелкой кнопку: 3. Математические модели и эквивалентные схемы в программе логического проектирования Любой реальный логический элемент(ЛЭ) не мгновенно реагирует на изменения входных сигналов, поэтому имеется некоторая паразитная задержка между моментом времени, в который на его входы поступают новые ...

0 комментариев