Навигация

Структурный синтез цифровых автоматов

2. Структурный синтез цифровых автоматов

2.1 Задача структурного синтеза

Процесс построения схемы автомата обычно разделяют на две относительно независимых стадии: абстрактный и структурный синтез. На стадии абстрактного синтеза, исходя из заданных условий работы, выполняется построение таблиц переходов и выходов автомата. Задачей структурного синтеза является построение функциональной схемы автомата. Исходными данными для стадии структурного синтеза являются таблицы переходов и выходов автомата, система логических элементов, тип элемента памяти, а также дополнительные условия, накладываемые на качество и на работу схемы, например: время работы, допустимость риска, условия связи с внешней средой, стоимость и т.п.

Следует отметить, что исходные данные и круг вопросов, решаемых на стадии структурного синтеза, могут существенно изменяться. Например, в некоторых случаях при структурном синтезе решают задачу выбора искомой схемы. В дальнейшем изложении совокупность исходных данных и задач, а структурного синтеза предполагаются такими, как они описаны в начале настоящего параграфа.

2.2 Обобщенная структурная схема автомата

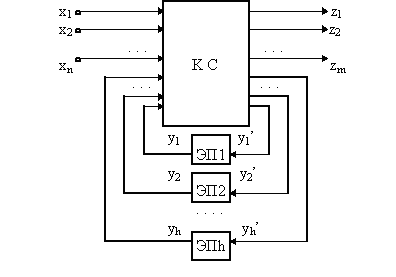

На стадии абстрактного синтеза обычно пользуются представлением автомата в виде одного блока, имеющего один вход и один выход. На стадии структурного синтеза автомат изображают в виде обобщенной структурной схемы, приведенной на рисунке 2.2 т n входных и m выходных каналов, по которым в подавляющем большинстве случаев передаются двоичные сигналы x1, x2,…, xn и z1, z2,…, zm. Переменные x1, x2,…, xn называют входными переменными, а z1, z2,…, zm – выходными переменными или функциями выходов автомата.

Рисунок 2.2. Обобщенная структурная схема автомата

Рассматриваемая схема состоит из двух частей: комбинационной схемы (КС) и набора элементов памяти (ЭП). Переменные y1, y2,…, yh, соответствующие выходным сигналам элементов памяти, называют внутренними переменными автомата. Переменные y1', y2',…, yh' используются в схеме для обозначения входных сигналов, изменяющих состояние элементов памяти, и называют функциями возбуждения. В качестве элементов памяти на практике чаще всего используют элементарные автоматы.

В приведенной схеме наборы значений входных переменных x1, x2,…, xn соответствуют буквам входного алфавита Р абстрактного автомата, наборы выходных переменных z1, z2,…, zm - буквам выходного алфавита W, y1, y2,…, yh - состояниям абстрактного автомата.

2.3 Структурная схема с преобразователями входных и выходных сигналов

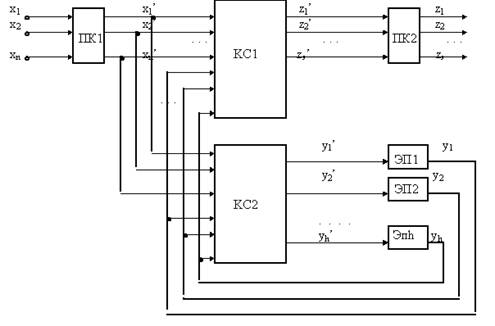

В общем случае комбинационная схема в приведенной структурной схеме автомата может решать несколько различных задач. Если эту схему разбить на подсхемы так, чтобы каждая задача решалась отдельной подсхемой, то структурная схема автомата может быть представлена в виде, изображенном на рис. 2.3. В этой схеме комбинационная схема КС1 вырабатывает функции выхода, КС2 – функции возбуждения, преобразователь кодов ПК1 используется для перекодирования входных сигналов, а преобразователь кодов ПК2 – для преобразования выходных сигналов. Наличие преобразователей кодов ПК1 и ПК2 не является обязательным в структурной схеме автомата, но в некоторых случаях их включение в схему позволяет добиться уменьшения сложности, упростить процесс построения или контроля работы схемы автомата.

Рисунок 2.3. Структурная схема с преобразователями входных и выходных сигналов

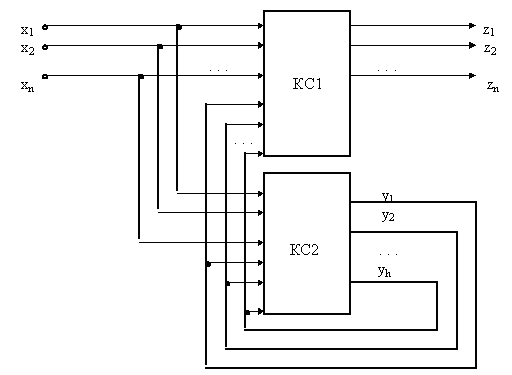

Необходимо отметить, что вид структурной схемы автомата в сильной степени зависит от используемой системы логических элементов. Например, при построении схемы на элементах с синхронизацией, сохраняющих результат логической операции до момента прихода считывающего сигнала, необходимость в элементах памяти часто отпадает. В этом случае структурная схема автомата может быть изображена в виде, приведенном на рисунке 2.3.1.

Рисунок 2.3.1. Упрощенная Структурная схема с преобразователями входных и выходных сигналов

2.4 Структурная схема на элементах импульсного типа

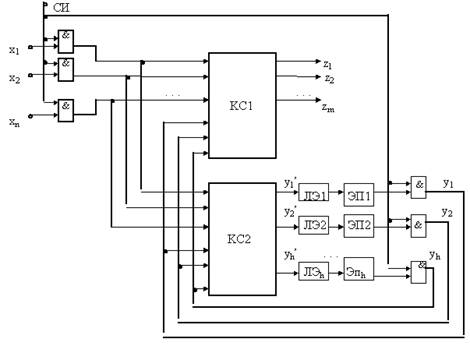

При построении схемы из логических элементов импульсного типа, работающих с импульсными сигналами длительностью t, и элементов памяти с выходными сигналами потенциального типа в структурную схему необходимо включить цепи синхронизации и линии задержки (ЛЗ), как это показано на рис. 4.

Рисунок 2.4. Структурная схема с линиями задержки

Линии задержки в такой схеме осуществляют задержку входных сигналов элементов памяти. Если время задержки (tз) этих линий немного больше величины t, то состояние элементов памяти остается неизменным на время действия синхронизирующего сигнала (СИ).

Похожие работы

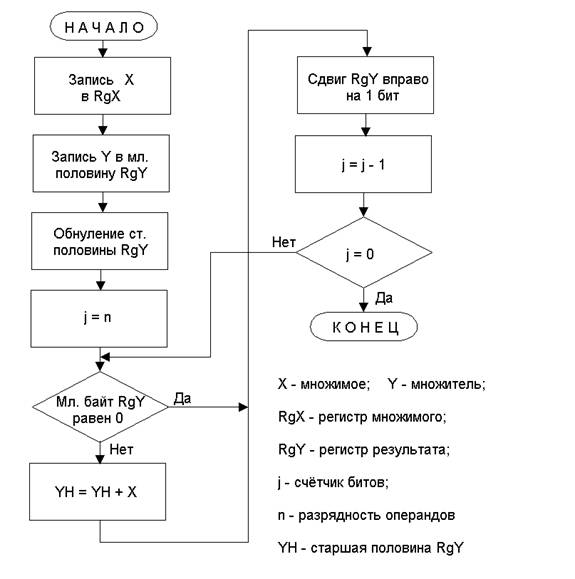

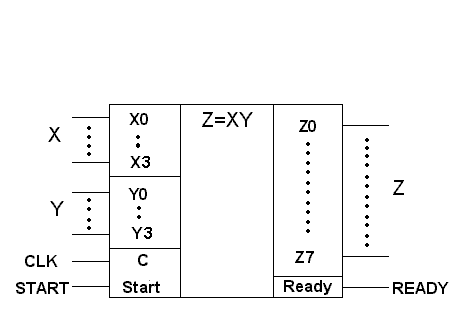

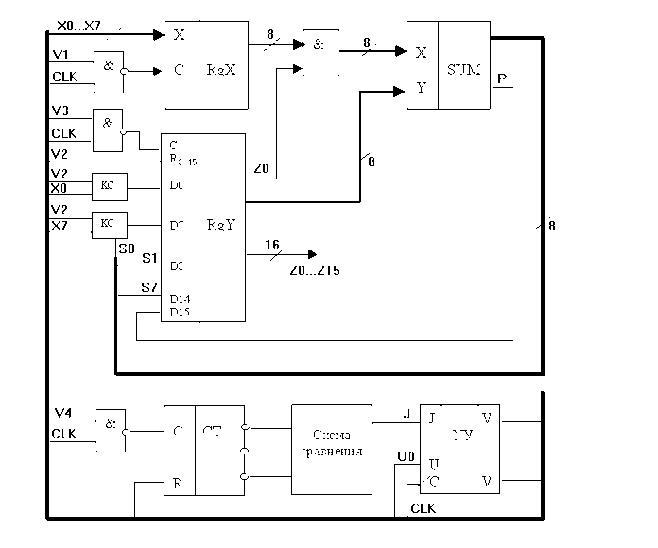

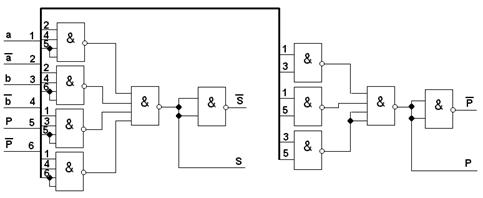

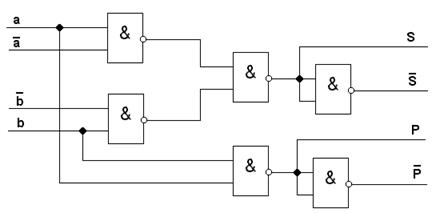

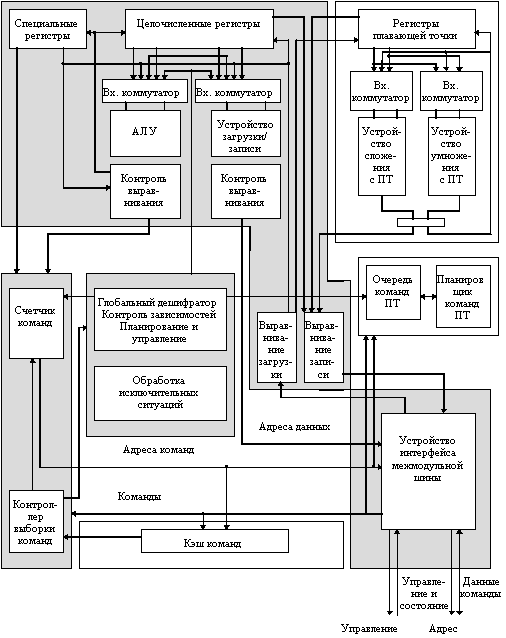

... RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре. Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел. Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме. 3 Синтез ...

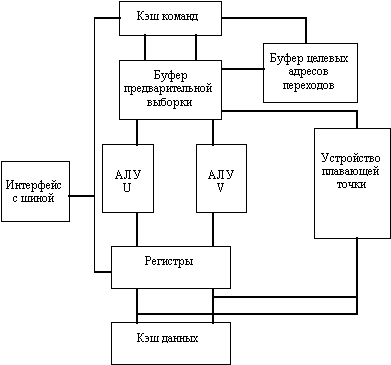

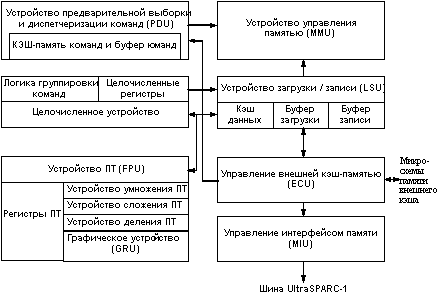

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

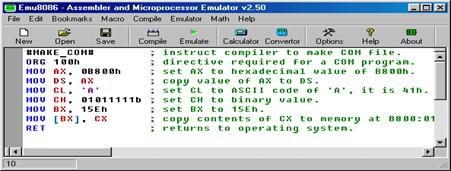

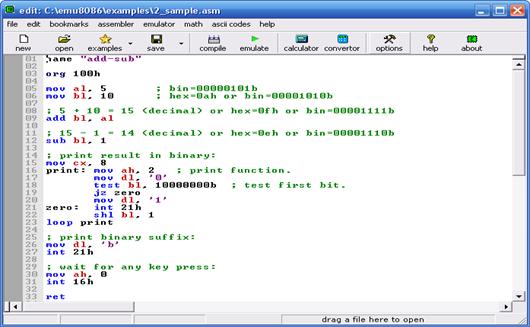

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

0 комментариев