Навигация

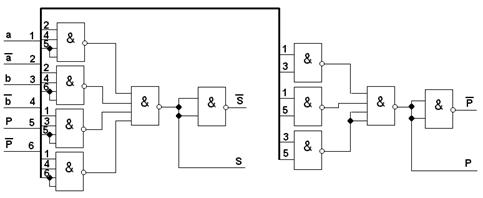

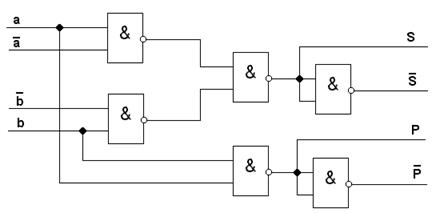

Графическое изображение полной схемы автомата

7. Графическое изображение полной схемы автомата.

2.6 Типы элементов памяти

В качестве элементов памяти на стадии структурного синтеза чаще всего используют элементарные автоматы с двумя выходными сигналами. Однако в последнее время в связи с разработкой больших интегральных схем представляет интерес использование в качестве элементов памяти широко применяемых в цифровых устройствах типовых схем: счетчиков и регистров. Элементы памяти с двумя выходными сигналами обычно называются триггерами. В большинстве случаев триггер является автоматом Мура. Он может иметь один или несколько входов. Работа триггера, как и любого автомата, описывается с помощью таблицы переходов.

На практике часто возникает задача построения триггеров из элементов заданной системы. Для этой цели используют характеристическое уравнение триггера, которое определяет состояние, в которое должен перейти триггер qt+1 в зависимости от входного сигнала xt и состояния qt, в котором находится триггер qt+1 = c (xt, qt). Построение характеристических уравнений триггеров выполняется обычно либо непосредственно по таблице переходов, либо с помощью диаграмм Вейча.

При построении функций возбуждения автомата необходимо решать обратную задачу: находить сигналы, которые нужно подать на вход триггера, чтобы перевести его из одного состояния в другое. Для этого используют матрицу переходов автомата, в которой для каждого перехода указаны соответствующие входные сигналы, вызывающие такой переход. Построение матрицы переходов выполняется, как правило, непосредственно по таблице переходов автомата.

3. Проектирование алгоритма и построение абстрактного автомата арифметико-логического устройства

3.1 Задание и исходные данные

Разработка арифметико-логического устройства, выполняющего операцию сложения и вычитания в прямом двоичном коде.

Исходные данные:

– разрядность операндов – 8 бит;

– разрядность результата – 8 бит;

– элемент памяти – ПЗУ;

– формат операндов и результата – 8 бит;

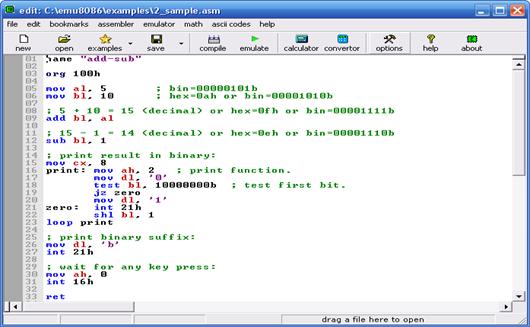

3.2 Разработка алгоритма устройства

Построим алгоритм заданного логического устройства. Распишем все возможные комбинации сочетания знаков чисел, поступающих на вход устройства с учетом типа операции

1.A+B

2.А+(-В)

3.-А+В

4.-А+(-В)

5.А-В

6.А – (-В)

7.-А-В

8.-А – (-В)

Учтя особенности сложения и вычитания в двоичном коде, получим:

1. А+В

2. А+Вд

3. Ад+В

4. Ад+Вд

5. А+Вд

6. А+В

7. Ад+Вд

8. Ад+В, где д – означает число, переведенное в дополнительный код.

Очевидно, что мы получили пары одинаковых комбинаций. Объединив номера 1 и 6, 2 и 5, 3 и 8, 4 и 7 получим:

1. А+В

2. А+Вд

3. Ад+В

4. Ад+Вд

Теперь мы имеем все данные для построения алгоритма, построим его:

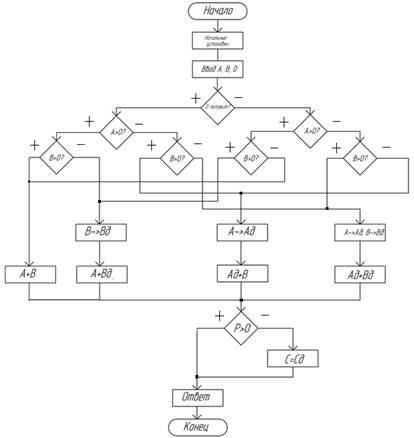

Рисунок 3.2.1. Алгоритм арифметико-логического устройства

Далее разметим алгоритм с учётом входных, выходных сигналов и состояний для построения абстрактного автомата Мили:

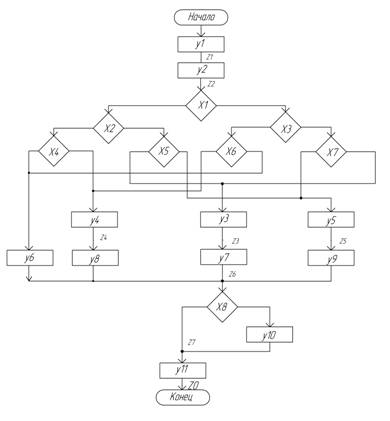

Рисунок 3.2.2 – Алгоритм с учётом входных, выходных сигналов и состояний

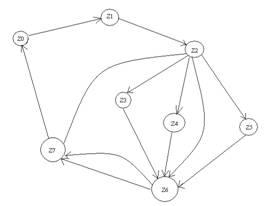

Нарисуем Граф автомата Мили

Запишем составляющие К1, К2, К3, К4, К5

К1=![]()

К2=![]()

К3=![]()

К4=![]()

К5=![]()

Входные сигналы К1, К2, К3, К4, К5, X8, ![]()

По размеченному алгоритму построим таблицу переходов-выходов автомата Мили.

Таблица 3.2 – Таблица переходов-выходов автомата Мили

| 1 |

|

|

|

|

|

|

| |

| Z0 |

| |||||||

| Z1 |

| |||||||

| Z2 |

|

|

|

|

| |||

| Z3 |

| |||||||

| Z4 |

| |||||||

| Z5 |

| |||||||

| Z6 |

|

| ||||||

| Z7 |

|

Похожие работы

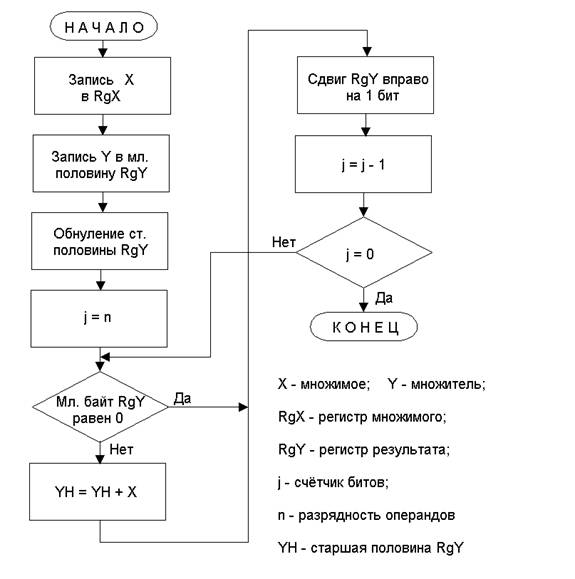

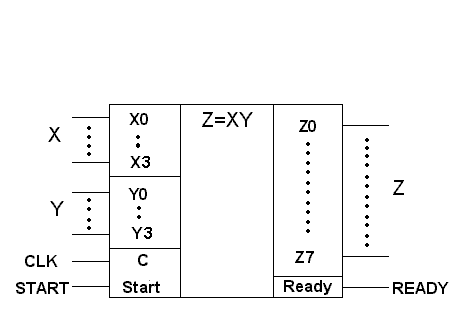

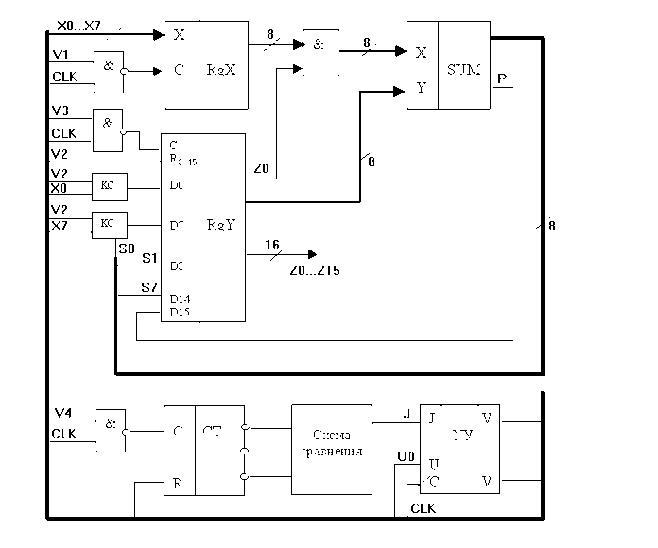

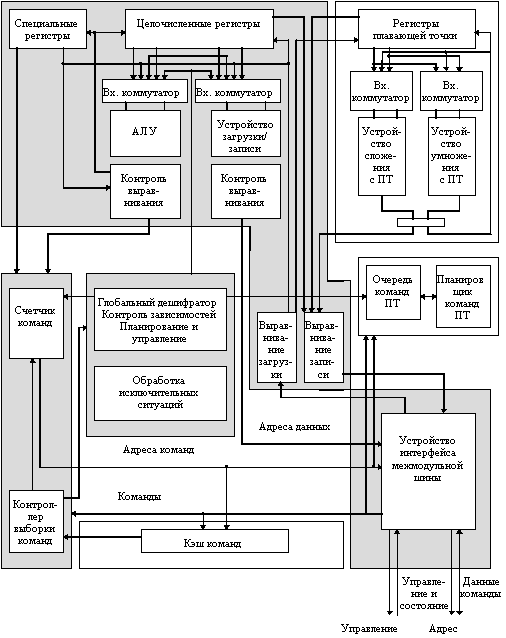

... RgХ и RgY имеют как прямые, так и инверсные выходы , что позволяет уменьшить количество элементов в сумматоре. Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел. Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме. 3 Синтез ...

... версия этого микропроцессора. Как и его предшественник, новый кристалл Alpha 21066A помимо интерфейса PCI содержит на кристалле интегрированный контроллер памяти и графический акселератор. Эти характеристики позволяют значительно снизить стоимость реализации систем, базирующихся на Alpha 21066A, и обеспечивают простой и дешевый доступ к внешней памяти и периферийным устройствам. Alpha 21066A ...

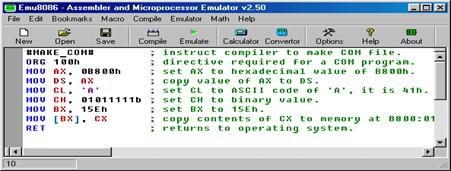

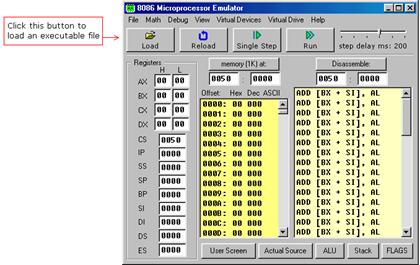

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

аучного цикла является отсутствие возможности реальной постановки учебного, и лабораторного эксперимента. Хотя в настоящее время имеются разработки виртуальных лабораторных практикумов, однако окончательно решение проблемы требует пристального внимания специалистов различных профилей, в том числе и психолого-педагогического. 1.2 Роль технологии виртуальных приборов обучения в техническом вузе ...

0 комментариев