Навигация

FTC- Tриггер с асинхронным сбросом. Назначение выводов: С-вход синхронизации; Т-вход разрешения переключений; CLR-вход сброса; Q- выход

4. FTC- Tриггер с асинхронным сбросом. Назначение выводов: С-вход синхронизации; Т-вход разрешения переключений; CLR-вход сброса; Q- выход.

Таблица истинности элемента FTC приведена в таблице 14.

Таблица 4- Таблица истинности элемента FTC

|

Вход CLR |

Вход Т |

Вход С |

Выход Q |

Режим Работы |

|

0 |

1 |

/ |

|

Переключение |

|

0 |

0 |

Х |

|

Хранение |

|

0 |

Х |

0 |

|

Хранение |

|

0 |

Х |

1 |

|

Хранение |

|

1 |

Х |

Х |

0 |

Асинхронный Сброс |

5. СВ4СЕ- четырехразрядный двоичный счетчик с асинхронным сбросом и входом разрешения счета.

Таблица 5- Таблица истинности элемента СВ4СЕ

|

С |

CLR |

СЕ |

QI |

TC |

CEO |

Режим работы |

|

Х |

1 |

Х |

0 |

0 |

0 |

Асинхронный сброс |

|

/ |

0 |

1 |

Счет |

0 |

0 |

Счет (Q[3;0]#1111) |

|

/ |

0 |

1 |

Счет |

1 |

1 |

Счет Q[3;0]=1111) |

|

Х |

0 |

0 |

|

|

0 |

Хранение |

Назначение выводов: С- тактовый вход; СЕ- вход разрешения счета; CLR-вход сброса; Q0-Q3- выходы (0-3 разряды); ТС-выход переноса (выход завершения счета); СЕО- выход разрешения счета (СЕО=ТС&СЕ).

Таблица истинности СВ4СЕ приведена в таблице 5.

6.СD4СЕ- четырехразрядный двоично-десятичный счетчик с асинхронным сбросом и входом разрешения счета. Назначение выводов: С- тактовый вход, СЕ-вход разрешения счета, CLR-вход сброса, Q0-Q3- выходы (0-3 разряды), ТС-выход переноса (выход завершения счета), СЕО-выход разрешения счета (СЕО=ТС&СЕ).Таблица истинности элемента СD4СЕ приведена в таблице 6.

Таблица 6- таблица истинности элемента СD4СЕ

|

C |

CLR |

СЕ |

QI |

TC |

CEO |

Режим работы |

|

Х |

1 |

Х |

0 |

0 |

0 |

Асинхронный сброс |

|

/ |

0 |

1 |

Счет |

0 |

0 |

Счет (Q[3;0]=1111) |

|

/ |

0 |

1 |

Счет |

1 |

1 |

Счет (Q[3;0]=1111) |

|

Х |

0 |

0 |

|

|

0 |

Хранение |

7.СОМР4 - цифровой четырехразрядный компаратор. Назначение выводов: А0-А3-выходы первого операнда(разряды 0-3), В0-В3-выходы второго операнда(разряды 0-3), EQ- выход А=В. Таблица истинности элемента СОМР приведена в таблице 7.

Таблица 7- таблица истинности элемента СОМР

|

Соотношение значений сигналов на входах А0-А3, В0-В3 |

Выход EQ |

|

IA0=IB0 и IA1=IB1 и IA2=IB2 и IA3=IB3 |

1 |

|

IA0#IB0 или IA1#IB1 или IA2#IB2 или IA3#IB3 |

0 |

8. D2_4E- дешифратор с 2 на 4 со входом разрешения, преобразующий двухразрядный двоичный код, поступающий на входы А0 А1, в напряжение высокого уровня, появляющиеся на одном из четырех входов D0-D3, при наличии сигнала высокого уровня на входе Е. Таблица истинности элемента D2_4E приведена в табл. 8.

Таблица 8- Таблица истинности элемента D2_4E

|

Е |

А0 |

А1 |

D0 |

D1 |

D2 |

D3 |

Режим работы |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

Преобразование двоичного кода в напряжение высокого уровня на соответствующем выходе |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

|

0 |

Х |

Х |

0 |

0 |

0 |

0 |

Стробирование |

9. D3_8E- дешифратор с 3 на 8 со входом разрешения, преобразующий трехразрядный двоичный код, поступающий на входы А0-А2, в напряжение при наличии сигнала высокого уровня на входе Е.

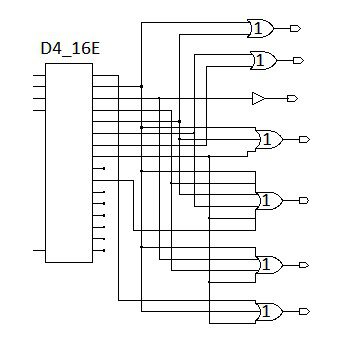

10. D4_16E- дешифратор с 4 на 16 со входом разрешения, преобразующий двухразрядный двоичный код, поступающий входы А0-А3, в напряжение высокого уровня, появляющиеся на одном из четырех входов D0-D15, при наличии сигнала высокого уровня на входе Е. Назначение выводов: Е-вход разрешения, А0-А3-входы (разряды 0-3), D0-D15-выходы(0-15 разряды).

11. М2_1- двухвходовый мультиплексор (2 в 1) с инверсией по одному входу. Назначение выводов D0, D1- информационные входы,S0-вход выбора, O-выход.

12. М4_1Е-четырехвходовый мультиплексор (4 в 1) со стробированием. Назначение выводов: D0-D3-информационные входы,S0,S1- входы выбора,O-выход.

Лабораторная работа №5

Делитель частоты

Цель:ознакомиться с принципами деления частоты.

Общие указания: Построить делитель частоты, чтобы 50МГц делилось в 5*106 раз , чтобы получить в итоге 1Гц. Построить делитель частоты на D-триггерах. Необходимо выбрать количества триггеров и собрать схему, соответствующую заданию.

1. Деление будет производиться в 2 этапа. На первом этапе частота делится на 25000000 раз, в итоге получаются короткие импульсы с частотой в 2 Гц. На следующем этапе импульсы подаются на Т-триггер для формирования меандра с частотой 1Гц.

3.Необходимо составить схему, состоящую из 25 D- триггеров, т.к. ![]()

4. Необходимо организовать элемент, который будет сбрасывать все триггеры в ноль по приходу 25000000-ого импульса. Сигнал сброса будет подаваться на Т-триггер.

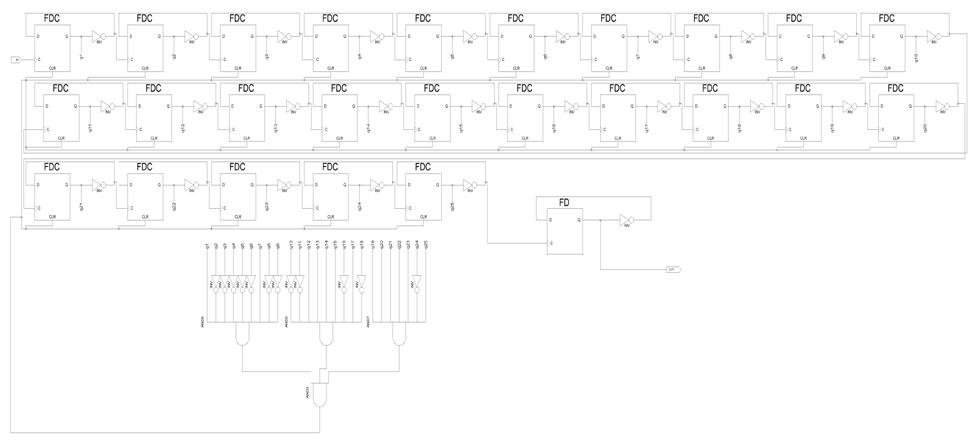

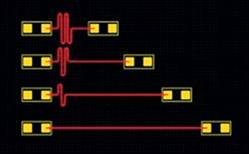

На рисунке 3.30 изображена схема делителя частоты.

Рисунок 3.30 - Схема делителя частоты.

Лабораторная работа №6

Семисегментный индикатор с динамической индикацией.

Цель: собрать схему динамической развертки на данном стенде для вывода четырехзначного числа.

Общие указания:

На рисунке 3.31 изображена схема динамической индикации.

Рисунок 3.31- Динамическая индикация

На рис. 3.32 схема подключения преобразователя к семисегментному индикатору

Рисунок 3.32- Схема подключения преобразователя к семисегментному индикатору

1. Выбираем дешифратор D4_16E. Дешифратор имеет 4 входа и 16 выходов.

2. Собираем схему семисегментного преобразователя на элементах стандартной логики.

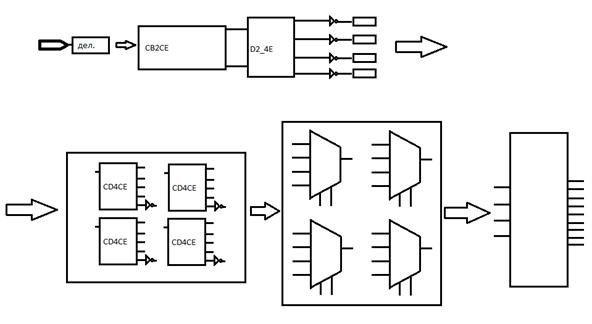

3. На рисунке 3.33 изображена схема динамической развертки.

Рисунок 3.33 - Блок-схема динамической развертки

4. Собранную схему проверить на стенде.

Лабораторная работа №7

Кодер BСD-код

Цель: построить схему кодера BDC кода.

Общие указания:

BCD- схема двоично-десятичного преобразователя (англ. binary-coded decimal), BCD, 8421-BCD — форма записи рациональных чисел, когда каждый десятичный разряд числа записывается в виде его четырёхбитного двоичного кода

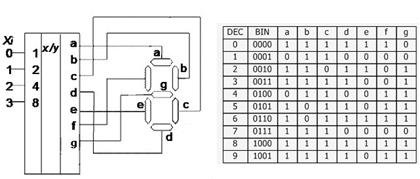

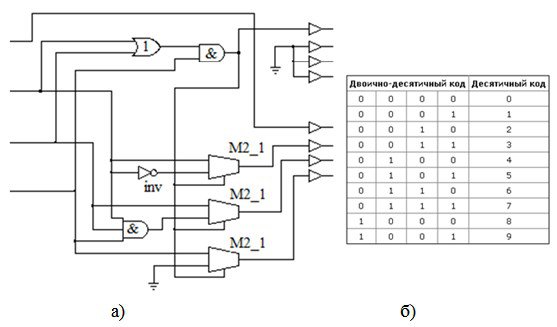

На рисунке 41 изображен BCD код с таблицей истинности

Рисунок 3.34. а)BCD – кодер; б) таблица истинности .

Лабораторная работа №8

Сумматор двоичного кода

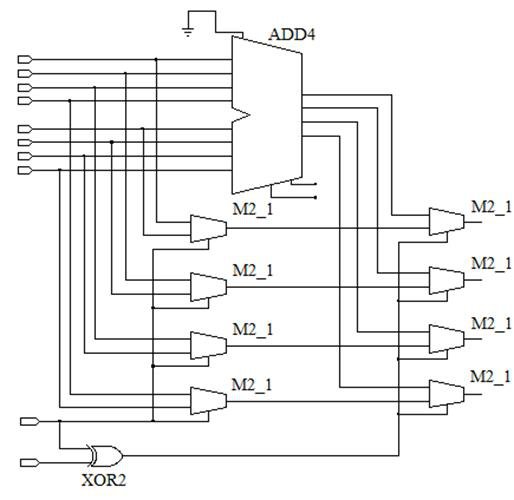

На рисунке 42 приведена схема сложения двух четырехразрядных чисел.

Рисунок 3.25. - Схема двоичного сумматора

1. Схема сумматора строится на базовых элементах, находящихся в библиотеке САПР ISEDesignSuite 14.4.

2. Проверить работу сумматора, подключив BCD и динамическую развертку (см. лабораторные №6 и №7)

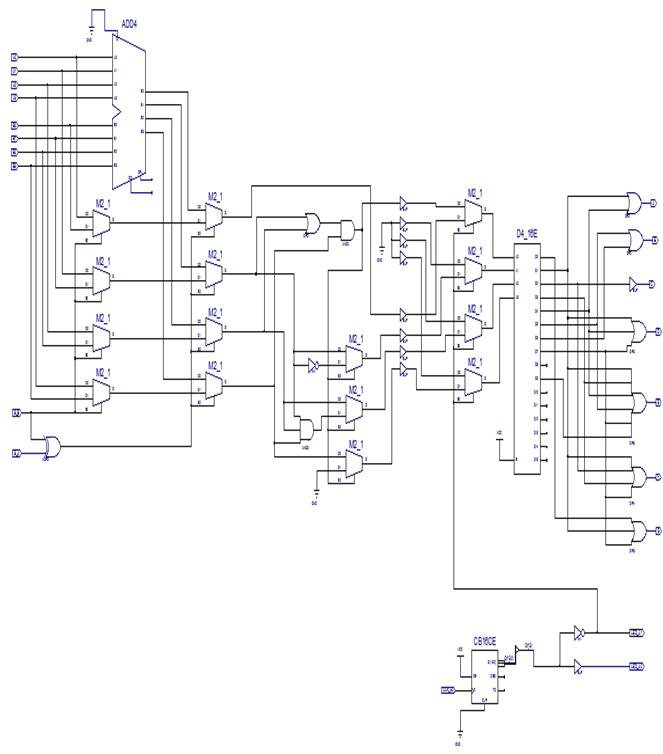

На рисунке 3.26 изображена схема полного сумматора.

Рисунок 3. 26. - Схема полного сумматора

Процесс разработки комплекса лабораторных работ был разбит на несколько этапов:

- Выбор стенда (ПЛИС XC9500XL);

- Разработка лабораторных работ;

- Решение лабораторных работ.

Применение лабораторных работ предназначено для изучения:

- систем на базе программируемых логических интегральных схем фирмы XILINX с архитектурой CPLD;

- принципов логического проектирования несложных узлов цифровых систем с использованием языков структурно–функционального описания аппаратуры;

- периферийных блоков вычислительных систем;

- подсистем ввода-вывода встраиваемых систем.

Возможно проведение данных лабораторных работ по следующим дисциплинам:

- цифровая схемотехника;

- цифровая обработка сигналов;

- цифровые устройства и микропроцессоры;

БИБЛИОГРАФИЧЕСИКЙ СПИСОК

1 Описание ПЛИС :http://plis.ru/docum#63& (дата обращения: 3.04.2015).

2 Зотов В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. - М.: Горячая линия-Телеком, 2003. - 624 с.

3 Фирма Altera: http://www.altera.ru/s-chego-nachat.html (дата обращения: 11.04.2015).

4Зотов В. Разработка встраиваемых микропроцессорных систем на основе ядра MicroBlaze, реализуемых в ПЛИС семейств FPGA фирмы Xilinx, с помощью «мастера» BaseSystemBuilderWizard // Компоненты и технологии. 2005. №№ 3–4

5 Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. - М.: Горячая линия-Телеком, 2006. - 520 с.

6 Разработка устройства на ПЛИС: http://knowledge.allbest.ru

7. ПЛИС:https://ru.wikipedia.org/wiki/%D0%9F%D0%9B%D0%98%D0%A1

8 Программируемые логические схемы и их применение: http://fpga-faq.narod.ru/ (дата обращения 15.04.2015).

Похожие работы

... завершенную автоматную структуру, ориентированную на реализацию как комбинационных (дешифраторов,мультиплексоров, сумматоров), так и последовательностных схем (управляющих автоматов, контроллеров, счетчиков). В ПЛИС заложены возможновти, которые позволяют превратить ее в ИС с любой функцией цифровой логики. Проектирование сводится к выявлению программируемых элементов (перемычек или запоминающих ...

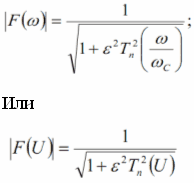

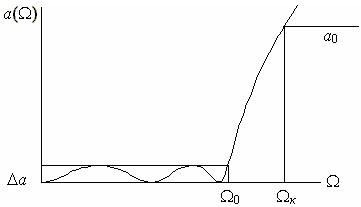

... диаграмм с сохранением результатов в стандартном формате VCD (Value Change Dump), воспринимаемом всеми системами работы с временными диаграммами. [1] 2.МЕТОД ПРОЕКТИРОВАНИЯ УСТРОЙСТВ ФИЛЬТРАЦИИ ПО РАБОЧИМ ПАРАМЕТРАМ Методика проектирования фильтров по рабочим параметрам основана на нахождении значений элементов, нармированных по частоте и сопротивлению нагрузки, путём аппроксимации или с ...

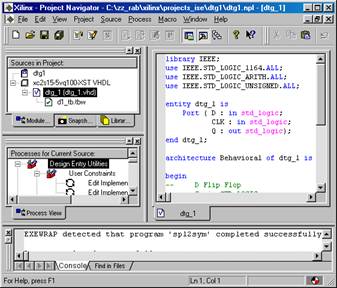

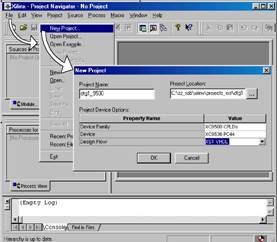

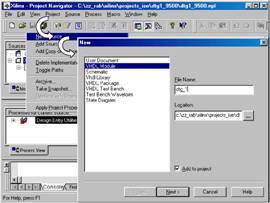

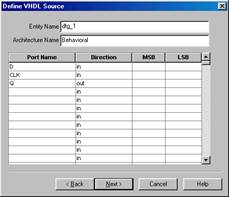

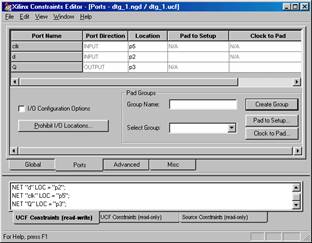

... элементов на кристалле и трассировки связей. 1. Ввод проекта Основные методы и приемы работы с САПР ISE рассмотрим на примере простейшей схемы D –триггера. Использование простейшей схемы позволяет отвлечься от особенностей самой схемы и сосредоточиться только на самом процессе проектирования. Создание нового проекта инициируется последовательным выбором пунктов меню File Þ New ...

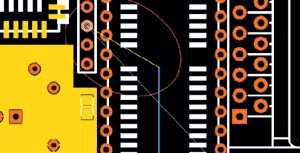

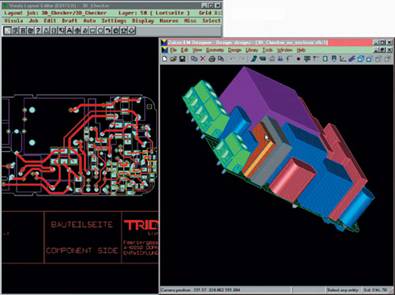

... один почти неизвестный в России, но достаточно мощный и популярный в мире продукт - Visula компании Zuken. Продукты этой компании обеспечивают сквозной цикл проектирования и предлагают мощные средства моделирования и синтеза программируемой логики с последующей разработкой печатной платы. Здесь имеется стандартный набор инструментария, а также собственные средства авторазмещения и автотрассировки ...

0 комментариев