Навигация

Pentium II

7. Pentium II.

7.1 Pentium II

Выпущенный с середины 1997 года, Pentium II ввел ряд больших изменений в мир процессоров PC.

Во-первых, чип и системный кэш второго уровня соединялись по выделенной шине, способной работать на частоте шины процессор-система.

Во вторых, процессор, вторичный кэш и тепло отвод были смонтированы на небольшой плате, вставлявшейся в разъем на системной плате, что больше напоминало карту расширения, чем традиционную схему процессор/гнездо. Intel окрестил это Single Edge Contact cartridge (SEC) - односторонне контактный картридж. В этом картридже находятся шесть отдельных компонент - процессор, четыре индустриально стандартных burst-static-cache RAM и один tag RAM. Дизайн SEC картриджа наделял важными преимуществами. PGA-компоновка Pentium Pro требовала 387 контактов, в то время как SEC-картридж - только 242. Уменьшение на треть числа контактов произошло благодаря наличию в картридже дискретных элементов, таких как замыкающие резисторы и конденсаторы. Эти элементы обеспечивают расщепление сигналов, что значит намного меньшее число требуемых разъемов питания. Разъем SEC-картриджа использует так называемый Slot 1 и воспринимается как принимающий эстафету у уходящего Socket 7.

Третье изменение - в большем синтезе, так как Pentium II объединяет Dual Independent Bus (DIB) от Pentium Pro c технологией MMX от Pentium MMX, формируя новый вид - гибрид Pentium Pro/MMX. Таким образом, внешне очень отличный от предыдущих интеловских процессоров, Pentium II внутренне являет собой смесь новых технологий и улучшений старых чипов.

И наконец, в отличие от Pentium Pro, работающего на 3.3v, Pentium II питается от 2.8v, позволяя Intel пускать его на больших частотах без чрезмерного увеличения требование к мощности. В то время, как 200MHz Pentium Pro с 512kb кэша потребляет 37.9 ватт, 266MHz Pentium II с 512kb кэша сжигает 37.0 ватт.

Подобно Pentium Pro, Pentium II применяет интеловскую Технологию Динамического Исполнения. Когда программная инструкция считывается в процессор и декодируется, она попадает в исполняемый пул. Технология Динамического Исполнения принимает три основных подхода к оптимизации способа обращения процессора с кодом. Множественные Предсказания Ветвлений проверяют программный поток вдоль нескольких ветвей и предсказывают, где в памяти находится следующая инструкция.

Когда процессор читает, он также проверяет следующие инструкции в потоке, ускоряя в результате рабочее течение. Анализ Потока Данных оптимизирует последовательность, в которой инструкции будут выполняться, проверяя декодированные инструкции и определяя, готовы ли они для обработки или зависят от других инструкций. Спекулятивное Выполнение увеличивает скорость таких инструкций просмотром вперед от текущей инструкции и обработкой дальнейших инструкций, которые вероятно могут понадобится. Эти результаты хранятся как спекулятивные до тех пор, пока процессор не определит, какие ему нужны, а какие - нет. С этой точки инструкция возвращается в нормальную очередь и добавляется к потоку.

У Технологии Динамического Исполнения есть два основных преимущества: Инструкции обрабатываются быстрее и эффективнее, чем обычно, и, в отличие от CPU с применением RISC архитектуры, программы не надо перекомпилировать для извлечения выгод процессора. Процессор все делает на лету.

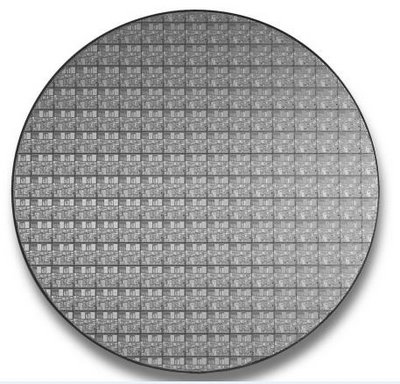

Значительной новой особенностью является удаление вторичного кэша из собственно процессора на отдельную кремниевую пластину в картридже. Процессор читает и пишет данные в кэше используя специализированную высокоскоростную шину. Называемая задней (backside) шиной, она отделена от системной шины процессор-память (сейчас называемой передней (frontside) шиной). Процессор может использовать обе шины одновременно, но архитектура двойной независимой шины имеет другие преимущества.

Хотя шина между процессором и кэшем второго уровня работает медленнее, чем на обычном Pentium Pro (на половине скорости процессора), она чрезвычайно масштабируема. Чем быстрее процессор, тем быстрее кэш, независимо от 66MHz передней шины. Вдобавок, передняя шина может быть увеличена с 66 до 100MHz без влияния на шину кэша второго уровня. Также очевидно, что наличие памяти на одном кристалле с процессором негативно сказывается на проценте выхода годных 512kb Pentium Pro, сохраняя высокими цены.

Pentium II опирается на GTL+ (gunning-transceiver-logic) логику хост-шины, допускающую естественную поддержку двух процессоров. Во время выхода это обеспечивало стоимостно эффективное минималистское двухпроцессорное решение, допускаемое симметричной мультипроцессорностью (SMP). Двухпроцессорное ограничение налагалось не самим Pentium II, а поддержкой чипсета. Изначальное ограничение чипсета двухпроцессорной конфигурацией позволяло Intel и поставщикам рабочих станций предлагать двухпроцессорные системы как временное и экономичное решение, что по другому и не было возможно. Это ограничение было снято с середины 1998 года с выходом чипсета 450NX, поддерживающего от одного до четырех процессоров. Чипсет 440FX, содержащий чипы PMC и DBX, не допускал чередования (interleaving) памяти, но поддерживал EDO DRAM, позволяя улучшать производительность памяти уменьшением ожидания.

Когда Intel проектировал Pentium II, он также взялся за слабую 16-битную производительность его предшественника. Pentium Pro роскошно работает с полностью 32-битным обеспечением, таким как Windows NT, но опускается ниже стандартного Pentium'а, обрабатывая 16-битный код. Это влечет худшую чем Pentium производительность под Windows 95, большие части которой пока 16-битны. Intel решил эту проблему использованием пентиумного кэша с дескрипторами сегментов в Pentium II.

Как и Pentium Pro, Pentium II чрезвычайно быстр в арифметике плавающей точки. В сочетании с Accelerated Graphics Port (AGP) это делает Pentium II мощным решением для высокопроизводительной 3D графики.

Похожие работы

... привилегированных инструкций или операций, которые можно выполнять только при определенных уровнях CPL и IOPL (биты 13 и 14 регистра флагов). ГЛАВА 2 Архитектура 32-разрядных процессоров История 32-разрядных процессоров началась с процессора Intel386. Эти процессора вобрали в себя все свойства своих 16-разрядных предшественников 8086/88 и 80286 для обеспечения программной совместимости с ...

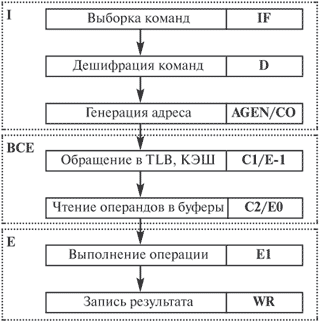

... конвейер. 3) поток команд порождает недостаточное количество операций для полной загрузки конвейера [3]. Рассмотрим принципы конвейерной обработки информации на примере пятиступенчатого конвейера, в котором выполнение команды складывается из следующих этапов: IF (Instruction Fetch) - считывание команды в процессор; ID (Instruction Decoding) - декодирование команды; OR (Operand Reading) - ...

... такой скорости, при которой Windows не загружается, вернитесь к предыдущему значению скорости (уменьшение скорости также проводите постепенно); - определив необходимую скорость работы процессора и, перезагрузив компьютер, проведите тестирование системы на предмет стабильной ее работы. Аппаратное и программное управление разгоном Для изменения частоты системной шины и значения множителя на ...

... : -производитель чипсет, если возможно – модель материнской платы; -тактовые частоты процессора, памяти, системных шин; -названия, параметры работы всех системных и периферийных устройств; -расширенная информация о процессоре, памяти, жестких дисках, 3D-ускорителе; -разнообразные параметры программной среды: ОС, драйверы, процессы, системные файлы и т.д.; -информация о поддержке видеокартой ...

0 комментариев