Навигация

Процессор 80186/88

3.4. Процессор 80186/88.

В 1981 г. появились микропроцессоры 80186/80188, которые сохраняли базовую архитектуру микропроцессоров 8086/8088, но содержали на кристалле контроллер прямого доступа к памяти, счетчик/таймер и контроллер прерываний. Кроме того, была несколько расширена система команд. Однако широкого распространения эти микропроцессоры (как и персональные компьютеры PCjr на их основе), не получили.

3.5. Процессор 80286.

Следующим крупным шагом в разработке новых идей стал микропроцессор 80286, появившийся в 1982 году. При разработке были учтены достижения в архитектуре микрокомпьютеров и больших компьютеров. Процессор 80286 может работать в двух режимах: в режиме реального адреса он эмулирует микропроцессор 8086, а в защищенном режиме виртуального адреса (Protected Virtual Adress Mode) или P-режиме предоставляет программисту много новых возможностей и средств. Среди них можно отметить расширенное адресное пространство памяти 16 Мбайт, появление дескрипторов сегментов и дескрипторных таблиц, наличие защиты по четырем уровням привилегий, поддержку организации виртуальной памяти и мультизадачности. Процессор 80286 применяется в ПК PC/AT и младших моделях PS/2.

3.6. Процессор 80386.

При разработке 32-битного процессора 80386 потребовалось решить две основные задачи - совместимость и производительность. Первая из них была решена с помощью эмуляции микропроцессора 8086 - режим реального адреса (Real Adress Mode) или R-режим.

В Р – режиме процессор 80386 может выполнять 16-битные программы (код) процессора 80286 без каких-либо дополнительных модификаций. Вместе с тем, в этом же режиме он может выполнять свои "естественные" 32-битные программы, что обеспечивает повышение производительности системы. Именно в этом режиме реализуются все новые возможности и средства процессора 80386, среди которых можно отметить масштабированную индексную адресацию памяти, ортогональное использование регистров общего назначения, новые команды, средства отладки. Адресное пространство памяти в этом режиме составляет 4 Гбайт.

Микропроцессор 80386 дает разработчику систем большое число новых и эффективных возможностей, включая производительность от 3 до 4 миллион операций в секунду, полную 32-битную архитектуру, 4 гигабитное (2 байт) физическое адресное пространство и внутреннее обеспечение работы со страничной виртуальной памятью.

Несмотря на введение в него последних достижений микропроцессорной техники, 80386 сохраняет совместимость по объектному коду с программным обеспечением, в большом количестве написанным для его предшественников, 8086 и 80286. Особый интерес представляет такое свойство 80386, как виртуальная машина, которое позволяет 80386 переключаться в выполнении программ, управляемых различными операционными системами, например, UNIX и MS-DOS. Это свойство позволяет производителям оригинальных систем непосредственно вводить прикладное программное обеспечение для 16-битных машин в системе на базе 32-битных микропроцессоров. Операционная система P-режима может создавать задачу, которая может работать в режиме виртуального процессора 8086 (Virtual 8086 Mode) или V-режим. Прикладная программа, которая выполняется в этом режиме, полагает, что она работает на процессоре 8086.

32-битная архитектура 80386 обеспечивает программные ресурсы, необходимые для поддержки "больших " систем, характеризуемых операциями с большими числами, большими структурами данных, большими программами (или большим числом программ) и т.п. Физическое адресное пространство 80386 состоит из 2 байт или 4 Гбайт; его логическое адресное пространство состоит из 2 байт или 64 терабайт (Тбайт). Восемь 32-битных общих регистров 80386 могут быть взаимозаменяемо использованы как операнды команд и как переменные различных способов адресации. Типы данных включают в себя 8-, 16- или 32-битные целые и порядковые, упакованные и неупакованные десятичные, указатели, строки бит, байтов, слов и двойных слов. Микропроцессор 80386 имеет полную систему команд для операций над этими типами данных, а также для управления выполнением программ. Способы адресации 80386 обеспечивают эффективный доступ к элементам стандартных структур данных: массивов, записей, массивов записей и записей, содержащих массивы.

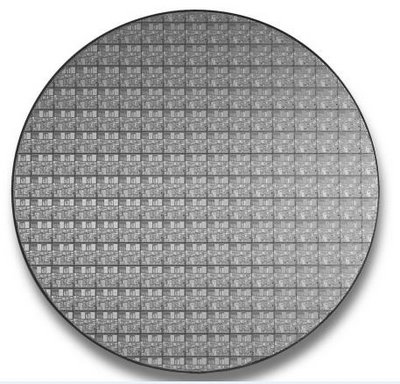

Микропроцессор 80386 реализован с помощью технологии фирмы Intel CH MOSIII - технологического процесса, объединяющего в себе возможности высокого быстродействия технологии HMOS с малым потреблением технологии кмоп. Использование геометрии 1,5 мкм и слоев металлизации дает 80386 более 275000 транзисторов на кристалле. Сейчас выпускаются оба варианта 80386, работающих на частоте I2 и I6 МГц без состояний ожидания, причем вариант 80386 на 16 МГц обеспечивает скорость работы 3-4 миллиона операций в секунду.

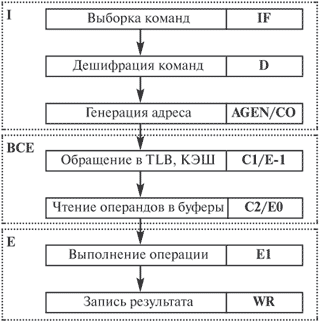

Микропроцессор 80386 разделен внутри на 6 автономно и параллельно работающих блоков с соответствующей синхронизацией. Все внутренние шины, соединяющие эти блоки, имеют разрядность 32 бит. Конвейерная организация функциональных блоков в 80386 допускает временное наложение выполнения различных стадий команды и позволяет одновременно выполнять несколько операций. Кроме конвейерной обработки всех команд, в 80386 выполнение ряда важных операций осуществляется специальными аппаратными узлами. Блок умножения/деления 80386 может выполнять 32-битное умножение за 9-41 такт синхронизации, в зависимости от числа значащих цифр; он может разделить 32-битные операнды за 38 тактов (в случае чисел без знаков) или за 43 такта (в случае чисел со знаками). Регистр группового сдвига 80386 может за один такт сдвигать от 1 до 64 бит. Обращение к более медленной памяти (или к устройствам ввода/вывода) может производиться с использованием конвейерного формирования адреса для увеличения времени установки данных после адреса до 3 тактов при сохранении двухтактных циклов в процессоре. Вследствие внутреннего конвейерного формирования адреса при исполнении команды, 80386, как правило, вычисляет адрес и определяет следующий магистральный цикл во время текущего магистрального цикла. Узел конвейерного формирования адреса передает эту опережающую информацию в подсистему памяти, позволяя, тем самым, одному банку памяти дешифрировать следующий магистральный цикл, в то время как другой банк реагирует на текущий магистральный цикл.

Похожие работы

... привилегированных инструкций или операций, которые можно выполнять только при определенных уровнях CPL и IOPL (биты 13 и 14 регистра флагов). ГЛАВА 2 Архитектура 32-разрядных процессоров История 32-разрядных процессоров началась с процессора Intel386. Эти процессора вобрали в себя все свойства своих 16-разрядных предшественников 8086/88 и 80286 для обеспечения программной совместимости с ...

... конвейер. 3) поток команд порождает недостаточное количество операций для полной загрузки конвейера [3]. Рассмотрим принципы конвейерной обработки информации на примере пятиступенчатого конвейера, в котором выполнение команды складывается из следующих этапов: IF (Instruction Fetch) - считывание команды в процессор; ID (Instruction Decoding) - декодирование команды; OR (Operand Reading) - ...

... такой скорости, при которой Windows не загружается, вернитесь к предыдущему значению скорости (уменьшение скорости также проводите постепенно); - определив необходимую скорость работы процессора и, перезагрузив компьютер, проведите тестирование системы на предмет стабильной ее работы. Аппаратное и программное управление разгоном Для изменения частоты системной шины и значения множителя на ...

... : -производитель чипсет, если возможно – модель материнской платы; -тактовые частоты процессора, памяти, системных шин; -названия, параметры работы всех системных и периферийных устройств; -расширенная информация о процессоре, памяти, жестких дисках, 3D-ускорителе; -разнообразные параметры программной среды: ОС, драйверы, процессы, системные файлы и т.д.; -информация о поддержке видеокартой ...

0 комментариев