Навигация

2.4. Отладка и тестирование

Тестирование производилось с помощью отладчика Turbo Debugger корпорации Borland. Была выполнена трассировка всей программы. Трассировка – это процесс пошагового выполнения команд с листингом состояний всех регистров, флагов, сегмента данных на момент выполнения каждой команды.

В ходе трассировки были обнаружены следующие ошибки:

неправильное определение состояния математического сопроцессора - неправильно указанная маска очистки, так называемого слова «equpment list», получаемого с помощью прерывания 11h;

“зависание” при вызове процедуры TestMem - ошибка в реализации алгоритма теста памяти – неправильно указанная метка перехода во вложенном цикле.

Кроме того, было обнаружено множество ошибок в синтаксисе команд.

Так как программа писалась на одном компьютере, проверить её на правильность определения конфигурации ПК не представлялось возможным, поэтому, после завершения программы, она выполнялась на разных ПК с разными конфигурациями: в ходе этого теста ошибок обнаружено не было – все аппаратные средства определялись правильно.

Также невозможно было проверить программу на правильность теста памяти на практике, потому что она выполнялась на всех ПК с исправной памятью, а попытки найти ПК с заведомо неисправной оперативной памятью не увенчались успехом. Тем не менее теоретически тест должен работать правильно.

2.5. Инструкция к пользователю

Для запуска программы выполните файл с именем «kurs.com». Вашему вниманию представиться аннотация – внимательно прочитайте её, а затем нажмите любую клавишу на клавиатуре (например, enter). Затем на экране высветится меню, изображенное на рис. 3.

| 1 – Сведения о системе 2 - Тест памяти 3 – Выход Ваш выбор ? : |

рис. 3

Для того, чтобы получить краткие сведения о вашем ПК - нажмите клавишу «1», затем «Enter» на вашей клавиатуре, и на экран высветится список устройств с текущем состоянием. Для возврата в меню нажмите любую клавишу.

Для того, чтобы протестировать оперативную память вашего ПК – нажмите клавишу, «2» затем «Enter» на вашей клавиатуре, и на экране высветится сообщение о состоянии памяти вашего ПК. Для возврата в меню нажмите любую клавишу.

Для того, чтобы выйти из программы - нажмите клавишу «3», затем «Enter» на вашей клавиатуре.

2.6. Заключение о результатах проектируемой задачи

В ходе выполнения поставленной в курсовом проекте задачи были приобретены навыки реализации сложных ассемблерных программ с использованием макросов и процедур. Кроме того, был получен огромный опыт и умение работы с CMOS (область памяти, где хранятся сведения о конфигурации ПК) на низком уровне, т.е. с использованием прерывания BIOS 11h и 70h порта, а также опыт использования дополнительных сегментных регистров и регистров модификаторов.

Реализованная программа может быть полезна при диагностике оборудования на относительно старых моделях ПК, поскольку в программе используется система команд 8086 процессора, который был выпущен в 1979 г. корпорацией Intel, и сейчас эта модель процессора является устаревшей.

Приложение № 1 7.1 СИСТЕМЫ СЧИСЛЕНИЯЛюбое неотрицательное число в позиционной системе счисления (СС) может быть представлено в виде:

D = Cn-1*bn-1 + Cn-2*bn-2 + ... + C1*b1 + C0*b0 + C-1*b-1 + C-2*b-2 +..,

где D - десятичный эквивалент числа, Ci - значение i-го разряда, b - основание системы счисления,b в степени i - вес i-го разряда и n число разрядов целой части числа. В вычислительной технике ниболее распространены: двоичная (BIN), десятичная (DEC), шестнадцатиричная (HEX) и непозиционная двоично-десятичная (BCD) системы счисления. В BCD системе вес каждого разряда равен степени 10, как в десятичной системе, а каждая цифра i-го разряда кодируется 4-мя двоичными цифрами. Восьмиричная СС (OCT) применяется реже. Первые 16 чисел представлены в таблице 1.

Двоичное число 10010011 = 1 * 2^7 + 1 * 2^4 + 1 * 2^1 + 1 * 2^0 = 147 (DEC). Для перевода числа из двоичной системы в 16 - ную, его необходимо разбить начиная справа на группы по 4 двоичных цифры и каждую группу представить 16 - ной цифрой из таблицы. Для обратного перевода каждая HEX цифра заменяется четверкой двоичных, незначащие нули слева отб- расываются. Двоично-десятичное число можно записывать и десятичными цифрами, например 1997, и двоичными - 0001 1001 1001 0111. Каждое десятичное число можно представить в виде BCD, например 19(DEC) = 19(BCD), но их двоичные представления не равны: 19(DEC) = 10011(BIN), а 19(BCD) = 1 1001(BIN). Не каждая запись из нулей и единиц имеет двоично-десятичный эквивалент. Например, 11001001(BIN) = ?(BCD) = C9(HEX) = 201(DEC), т.к. десятичной цифры 12 = 1100 несуществует!

7.2 МАШИННОЕ ПРЕДСТАВЛЕНИЕ ИНФОРМАЦИИМикропроцессоры обрабатывают упорядоченные двоичные наборы. Минимальной единицей информации является один бит.

Далее следуют - тетрада (4 бита), байт ( byte 8 бит), двойное слово (DoubleWord 16 бит) или длинное (LongWord 16 бит) и учетверенное слова. Младший бит обычно занимает крайнюю правую позицию.

7.3 ЧИСЛА С ФИКСИРОВАННОЙ ТОЧКОЙТакие числа могут быть как целыми, так и дробными. Точка мысленно фиксируется рядом с любым разрядом. Если она располагается справа от младшего бита, то число целое, если слева от старшего - число дробное. Далее будут рассматриваться только целые числа с фиксированной точкой, для нецелых чисел чаще применяется показательная форма, о которой пойдет речь дальше.

Естественным представлением целого неотрицательного числа является двоичная система счисления. Кодирование отрицательных чисел производится тремя наиболее употребительными способами, в каждом из которых крайний левый бит - знаковый. Отрицательному числу соответствует единичный бит, а положительному - нулевой. Каждый способ оценивается по скорости и затратам на выполнение сложения и изменения знака числа, т.к. вычитание есть сложение с измененным знаком одного операнда.

1.Прямой код. Изменение знака производится просто, путем инверсии бита знака. Пусть 00001001 = 9, тогда 10001001 = -9. Если при сложении двух чисел в этом коде знаки совпадают, то трудностей нет. Если знаки различаются необходимо найти наибольшее число, вычесть из него меньшее, а результату присвоить знак наибольшего слагаемого. 2.Обратный код, инверсный или дополнительный "до 1". Изменение знака производится просто - инверсией всех бит: 00001001 = 9, а 11110110 = -9. Сложение также выполняется просто, т.к. знаковые биты можно складывать. При переносе единицы из левого (старшего) бита, она должна складываться с правым (младшим). Например: 7 + (-5) = 2.

00000111 = 7

11111010 =-5 (инверсия 00000101 = 5)

1 00000001

1

00000010 = 2

Сложение в обратном коде происходит быстрее, т.к. не требуется принятие решения, как в предыдущем случае. Однако суммирование бита переноса требует дополнительных действий. Другим недостатком этого кода является представление нуля двумя способами, т.к. инверсия 0...00 равна 1. ..11 и сумма двух разных по знаку, но равных по значению чисел дает 1...11.Например: (00001001 = 9) + (11110110 = -9) = 11111111. Кстати, из этого примера понятно почему код называется дополнительным "до 1". Этих недостатков лишен ---

3.Дополнительный или дополнительный "до 2" код. Число с противоположным знаком находится инверсией исходного и добавлением к результату единицы. Например, найти код числа -9.

00001001 = 9 11110111 =-9

11110110 - инверсия 00001000 - инверсия

1 1

11110111 =-9 00001001 = 9

Проблемы двух нулей нет. +0 = 00000000, -0 = 11111111 + 1 = 00000000 (перенос из старшего бита не учитывается).Сложение производится по обычным для неотрицательных чисел правилам.

00001001 = 9

11110111 =-9

1 00000000

Из этого примера видно, что в каждом разряде двух равных по модулю чисел складываются две единицы, что и определило название способа. Этот метод применяется наиболее часто, и когда говорят о дополнительном коде, то имеется в виду дополнительный "до 2-х" код.

7.4 ДИАПАЗОН ЦЕЛЫХ ЧИСЕЛ С ФИКСИРОВАННОЙ ТОЧКОЙБеззнаковые числа: 0 <= D <= 2^n - 1. n - число разрядов

Байт: 0 - 255 (DEC) Слово: 0 - 65535

00..0 - 11..1 (BIN) 00..0 - 11..1

0 - FF (HEX) 0 - FFFF

Числа со знаком:-2^(n-1) <= D <= +2^(n-1)-1. n - число

разрядов.

Байт: -128 - +127 (DEC) Слово: -32768-+32767

10..0 - 01..1 (BIN) 10..0 - 01..1

80 - 7F (HEX) 8000 - 7FFF 7.5 ЧИСЛА С ПЛАВАЮЩЕЙ ТОЧКОЙ (ВЕЩЕСТВЕННЫЕ)

Вещественные числа хранятся и используются в ЭВМ в показательной форме, т.е. в виде двух составляющих: мантиссы и порядка. Различия в способах такого представления чисел заключаются в количестве байтов отводимых под порядок и мантиссу и небольших отличиях в форме их хранения. Например в четырехбайтовом формате под мантиссу отводится 3 байта и один байт для хранения порядка (КВ - короткий вещественный формат).

D = ±M * 2^(E-127)

Последовательность расположения байтов

в различных ЭВМ может быть разной. D - десятичный эквивалент числа , M - нормализованная мантисса, Е - смещенный порядок, SM - бит знака мантиссы.

7.6 ДИАПАЗОН ПРЕДСТАВЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛУ нормализованной мантиссы первая значащая цифра (единица) мысленно находится слева от запятой, а справа располагаются 23 разряда - 1,xx..xx. Поэтому Mmax = 1,111..11 = 1 +1/2 +1/4+ 1/8 +...= 2, а Mmin= 1,000..00 = 1 для положительных чисел (SM=0) и -1 и -2 для отрицательных, (SM=1). Порядок числа Emax = 11111110 = 254, а Emin = 00000001 = 1. Теперь нетрудно определить диапазон представления положительных чисел от +Dmax = Mmax * 2^(254-127) = 3,4 * 10^38 до +Dmin = Mmin * 2^(1-127) = 1,17 * 10^(-38). Точность определяется числом достоверных десятичных цифр. При 23 двоичных разрядах мантиссы 2^23 примерно равно 10^7, т.е. достоверными являются только 6-7 значащих десятичных знаков, а не 38. Необходимо отметить, что значения порядка 11111111 и 00000000 по международному стандарту IEEE 754 и 854 предназначены для кодирования денормализованных чисел, отрицательной и положительной бесконечностей, неопределенности и, так называемых Не-чисел.

7.7 ДВОИЧНО-ДЕСЯТИЧНЫЙ КОДДвоично-десятичный код (ДДК) или Binary Coded Decimal (BCD) может быть упакованным, когда в одном байте хранятся две десятичные цифры, либо неупакованным - по одной цифре в байте.Упакованное число 1996 представляется в виде двух байтов: 0001 1001 и 1001 0110. Для знака числа отводится дополнительный байт, например в формате (ДД) девять байтов отводится для размещения 18-ти цифр, а в старшем бите десятого байта находится знак числа.

7.8 БУКВЕННО-ЦИФРОВОЙ КОДДля вывода информации на устройства отображения, например дисплей или принтер, а также для ввода или передачи данных используются буквенно-цифровые коды. Буквы, цифры, математические символы, знаки препинания, символы для рисования линий, управляющие символы и некоторые другие кодируются однобайтовыми числами. Существует несколько разновидностей таких кодов, например: ASCII, КОИ-7, КОИ-8, альтернативный код ГОСТ, основной код ГОСТ и другие. ASCII и 7-ми битовый код для обмена информацией (КОИ-7) отображают первые 128 символов и входят в состав остальных кодировок. Дополнительные символы и русский алфавит входят в восьмибитовые расширенные коды (КОИ-8, альтернативный и основной). Общее число символов в этих кодах равно 256. Таблица некоторых кодов приведена ниже. Следует отметить, что нулевой код (NULL) не кодирует цифру ноль и вообще никак не отображается.

Символ ¦ Код(HEX) Символ ¦ Код(HEX) Символ ¦ Код(HEX)

--------+--------- -------+--------- -------+---------

"ничего"¦ 00 "A" ¦ 41 "А" ¦ 81

"0" ¦ 30 "B" ¦ 42 "Б" ¦ 82

"1" ¦ 31 "C" ¦ 43 "В" ¦ 83

.. ¦ .. .. ¦ .. .. ¦ ..

"9" ¦ 39 "Z" ¦ 5A "Я" ¦ 9F

":" ¦ 3A "[" ¦ 5B "а" ¦ A0

\_________ASCII кодировка___________/

\_______________альтернативная кодировка_______________/

В Internet для русского языка используется кодировка КОИ-8. В настоящее время разработан и используется 16-ти битовый Unicode с 65536 различными симвоволами.

7.9 ВОСЬМИСЕГМЕНТНЫЙ КОДСлужит для отображения образа BCD или HEX цифры высвечиваемой на индикаторе в виде набора 0 и 1. Может быть принято следующее соответствие между битами и сегментами:

Внизу приведен битовый набор для высвечивания цифры 4. Единицы обычно соответствуют светящимся сегментам.

7.10 НЕОДНОЗНАЧНОСТЬ ПРЕДСТАВЛЕНИЯ ДВОИЧНЫХ НАБОРОВНабор единиц и нулей хранящихся в регистре или ячейке памяти (двоичный набор) для микропроцессора ничего не означает. Пусть в регистре находится набор из восьми битов 10000110. Он может быть интерпретирован следующим образом, как:

1) двоичное число = 10000110, имеющее

а) шестнадцатиричный эквивалент = 86(HEX),

б) восьмиричный эквивалент = 206(OCT),

в) десятичный эквивалент числа без знака = 134(DEC),

2) дополнительный код отрицательного числа =-122(DEC),

3) двоично-десятичное упакованное число = 86(BCD),

4) альтернативный код буквы "Ж",

4') код КОИ-8 символа "¦",

5) восьмисегментный код цифры "1.",

6) часть вещественного числа,

7) реализация множества,включающего 3 элемента из 8-ми,

8) часть адреса ячейки памяти или внешнего устройства,

9) код операции и т.д.

Поэтому ответственность за интерпретацию двоичных наборов возлагается на программиста. Например, попытка сложить ASCII коды "1" + "2" не даст в сумме код "3", а даст 31(HEX) + 32(HEX) = 63(HEX), что соответствует коду латинской буквы "c".

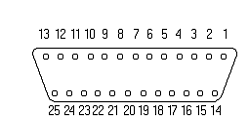

Приложение № 2 СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРАОгромное количество микропроцессоров (МП) не позволяет рассмотреть их особенности, поэтому выбор пал на родоначальника семейства 80x86 : МП К1810ВМ86/88 (8086/8088). Такой выбор оправдан, во-первых преобладающим парком ЭВМ с этим МП, во-вторых тем, что все МП этого семейства при включении начинают работу в реальном режиме МП 8086, и в-третьих - программной совместимостью их ассемблеров снизу вверх. На рис 1. приведена структурная схема МП8086 и внешний вид типового микропроцессора.

Устройство управления декодирует байты программы и управляет работой операционного устройства и шинного интерфейса. Операционное устройство МП состоит из 4-х шестнадцатиразрядных регистров общего назначения: РОН (AX,BX,CX,DX), из 4-х регистров указателей (адресных регистров SP,BP,SI, DI) и арифметико-логического устройства (АЛУ) с регистром признаков операций (флагов F).

РОН служат для хранения промежуточных результатов операций, т.е. операндов. Помимо общих, каждый из этих регистров имеет и некоторые специальные функции, о которых будет сказано далее. Каждый РОН может раcсматриваться, как состоящий из двух независимых 8-ми разрядных регистров AH, AL, BH, BL, CH, CL и DH, DL.

Адресные регистры хранят 16-ти битовые указатели (адреса) на области памяти. В SP (StackPointer) находится текущий адрес "вершины стека" - специально организованной области памяти, которая будет описана далее. Регистр BP(Base Pointer) хранит любой базовый адрес в области стека. Два регистра SI и DI (Source и Destination Index) адресуют области памяти, называемые источником и приемником данных.

Шинный интерфейс, на рис.1 его узлы отмечены двойной чертой, выполняет операции обмена между МП и памятью или внешними устройствами. В сегментных регистрах CS,SS,DS,ES хранятся указатели на 64-х килобайтные области памяти называемые сегментами. Значения этих указателей могут перекрываться. Адрес байта в ячейке памяти получается суммированием содержимого одного из сегментных регистров и одного из регистров (SP,SI,DI,IP). Например адрес текущего байта программы, извлекаемого из памяти определяется суммой адресов, хранящихся в регистре кодового сегмента (CS) и указателе команд (IP). В регистре IP хранится 16-битовый адрес байта в кодовом сегменте к которому микропроцессор дожен обратиться. Подробнее об этом будет сказано далее. Связь с внешними устройствами осуществляется через специальные тристабильные схемы с повышенной нагрузочной способностью и называемые буферами.

Текущий байт программы направляется в очередь команд: шесть однобайтовых регистров расположенных конвейером (по принципу "первым вошел - первым вышел" или FIFO ). Конвейер позволяет одновременно выполнять команду из очереди и загружать следующую, повышая производительность МП. Буферные тристабильные элементы увеличивают мощность сигналов до стандартных значений ТТЛ.

8.2 РЕГИСТР ФЛАГОВПо результатам операций АЛУ устанавливает либо сбрасывает отдельные биты в регистре флагов F.

x обозначает, что содержимое этого бита не имеет значения. Некоторые операции влияют только на отдельные флаги, а другие совсем на них не воздействуют, поэтому при описании флагов подразумевается выполнение тех команд (операций), которые влияют на эти флаги. В дальнейшем, в тексте, фраза "содержимое XX" будет обозначаться круглыми скобками - (XX).

ZF - флаг/признак нулевого результата (Zero), устанавливается в 1, если получен нулевой результат, иначе (ZF)=0. CF - флаг переноса (Carry) устанавливается, если в результате выполнения операции из старшего бита переносится или занимается 1 при сложении или вычитании, иначе (CF)=0. На CF влияют также команды сдвига и умножения. SF - флаг знака результата (Sign) равен единице, если результат отрицательный, т.е. он дублирует старший знаковый бит результата. PF - флаг четности (Parity). (PF)=1, если сумма по модулю два всех битов результата равна нулю (число единичных битов - четное). AF - флаг дополнительного переноса (Auxiliary) устанавливается, если есть перенос из старшего бита младшей тетрады (бит D3) в младший бит старшей тетрады (бит D4). Используется в операциях над упакованными BCD числами. OF - флаг переполнения (Overflow) устанавливается, когда результат операции превысит одно- или двухбайтовый диапазон чисел со ЗНАКОМ, а также в некоторых других случаях. Другое определение: (OF)=1, если перенос/заем в старший бит результата не равен переносу/заему из старшего бита.Рассмотрим в качестве примера сложение двух однобайтовых чисел: 125 + 4 = 129 выходит за пределы -128.. ..+127 чисел со знаком (для беззнаковых чисел 129 - корректный результат).

0 1 1 1 1 1 0 1 = +125

0 0 0 0 0 1 0 0 = +4

1 0 0 0 0 0 0 1 = +129 > +128 (или -127 ???)

/ / :

0 1 :

Перенос в бит D7 равен 1, а из бита D7 = 0, в результате сложения чисел (OF) = 1, (CF) = 0, (ZF) = 0, (SF) = 1, (PF) = 0, (AF) = 1. Остальные три флага будут рассмотрены далее. Содержимое регистра признаков называется также словом состояния процессора(программы) и обозначается PSW.

ОРГАНИЗАЦИЯ ПАМЯТИ И ВЫЧИСЛЕНИЕ АДРЕСАМП 8086 имеет 20-ти разрядную шину адреса ША, позволяющую обращаться к 2^20 или примерно к одному миллиону ячеек памяти. 16-ти битовая шина данных ШД может пересылть информацию байтами или словами. Память обычно организована в виде линейного одномерного массива байтов, причем два соседних байта могут рассматриваться как слово. Все мегабайтное пространство памяти условно делится на 16 сегментов объемом по 64Kb. Микропроцессору доступны в каждый момент четыре - кодовый сегмент, где хранится программа, стековый сегмент, сегмент данных программы и дополнительный сегмент данных. Начальные адреса этих сегментов хранятся в регистрах CS,SS,DS и ES. Так как эти регистры 16-ти битовые, а все адресное пространство 20-ти битовое, то МП начальный сегментный адрес в 20-ти битовом сумматоре сдвигает на четыре бита влево (эквивалентно умножению на 16) и складывает с содержимым одного из регистров (IP,SP,DI,SI).

Полученное число называется физическим адресом. Например, извлекая из памяти очередной байт кода программы МП формирует физический адрес по формуле: Физический адрес = (IP) + (CS) * 16, где (IP) - смещение, эффективный или исполнительный адрес, (CS) - сегментный адрес, а (CS) * 16 - называется начальным сегментным адресом. Организация памяти приведена на рис.2.

8.4 ПРОЦЕССОРНЫЙ БЛОК (ПБ )включает микропроцессор, стабилизируемый кварцем генератор импульсов, два устройства для формирования адресных и управляющих сигналов и двунаправленный буфер шины данных. Схема ПБ представлена на рис.3. Для уменьшения общего количества выводов МП, по некоторым из них в разные моменты передаются разные сигналы, поэтому младшие 16 линий адреса и шина данных совмещены (мультиплексированы).

Конденсатор C до включения питания разряжен. В начальный момент времени t0 подается напряжение питания на выводы (+). Начиная с этого момента времени на входе ~RES действует логический 0 до момента t1, когда напряжение на конденсаторе C достигнет порогового значения логической 1. В течение интервала t0..t1 выходной сигнал RESET имеет активный уровень лог.1. Микропроцессор переводится в исходное состояние. При этом в регистр CS записывается код FFFFh, а в регистр IP код 0000h.

Когда C зарядится и сигнал ~RES станет "1", на входе RESET микропроцессора сигнал снизится до пассивного уровня. Начинается основной цикл работы. МП извлекает из ячейки памяти с адресом FFFF:0000 первый байт команды, который чаще всего является кодом безусловного перехода к тому месту в памяти, где находится начало программы. В процессе работы можно перезапустить МП с помощью кнопки SW. Конденсатор C разряжается до нуля и процесс запуска повторяется. МП может работать в двух режимах в максимальном и минимальном. Минимальный режим ограничивает адресуемый объем памяти до 64Kb. В большинстве приложений в приборостроении такого объема достаточно, поэтому сигнал ~MX/MN = 1. Формирователи сигналов ШУ,ША и ШД (шины управления адреса и данных), выполнены на элементах ИЛИ, регистрах и шинных формирователях и служат также для увеличения мощности этих сигналов.

Генератор G формирует последовательность импульсов CLK, называемых тактовыми. Выполнение команды производится в течение интервалов времени, называемых циклами. Если в цикле есть обращение к памяти или к внешним устройствам, то он называется циклом шины. Цикл шины содержит 4 обязательных такта T1 ... T4.

В такте T1 микропроцессор передает по совмещенной шине адрес/данные адрес ячейки памяти или внешнего устройства (ВУ), подключенного к шинам ШУ,ША и ШД. В такте T2 производится выбор направления обмена данными с памятью или ВУ, а в тактах T3,T4 - передача данных. Если ЗУ (запоминающее устройство) или ВУ медленные, то на вход готовности RDY посылается сигнал RDY = 0, по которому МП вставляет циклы ожидания TW, до тех пор, пока не будет установлена готовность ВУ или ЗУ (RDY = 1). Если в цикле нет обращения к шине, то МП формирует холостые циклы TI.

Для разделения сигналов совмещенной шины адрес/данные ШАД(AD15..0) их необходимо "демультиплексировать" с помощью регистра защелки адреса RG и двунаправленного буфера BD. При обращении к памяти (в том числе при выборке команды) микропроцессор передает по ШАД адрес ячейки памяти. Этот адрес записывается в D-триггеры регистра RG сигналом ALE генерируемым микрпроцессором в этот момент и поступающим на синхровходы D-триггеров. Адрес в регистре сохраняется на время последующей передачи данных. Следом по ШАД передаются, либо данные от микропроцессора к ВУ или ЗУ, либо в обратном направлении. МП должен, во-первых, обеспечить правильное направление передачи буфера BD и , во-вторых, открыть (разрешить) тристабильные элементы буфера для передачи данных. Первую задачу решает сигнал МП ~DT/R (~DT/R=0 передача данных от МП - Transmit, ~DT/R=1 прием данных МП - Receive).

Вторая задача решается генерацией МП сигнала ~DEN (Data Enable). Чтение или ввод данных в один из регистров МП осуществляется с помощью инверсных сигналов шины управления (ШУ): ~MEMR (чтение из памяти),~IOR (ввод из ВУ), называемыми еще стробами чтения. Запись или вывод данных из МП по шине данных сопровождается стробами записи ~MEMW (запись в память (ЗУ)), или ~IOW (вывод во внешнее устройство (ВУ)). Четверка стробов, которые являются основными сигналами шины управления, формируется из сигналов чтения, записи (~RD,~WR) и сигнала M/~IO, определяющего к чему производится обращение : к ЗУ или ВУ. Формирование этих сигналов производится с помощью простой комбинационной схемы, содержащей 4 элемента ИЛИ и один инвертор.

8.5 МИКРОПРОЦЕССОРНАЯ СИСТЕМА С ТРЕМЯ ШИНАМИРаботой всех устройств подключаемых к процессорному блоку управляет дешифратор DC, к входам которого подводятся линии шины адреса. Обычно дешифраторов бывает несколько. Если используется не все адресное пространство для памяти и ВУ, то на дешифратор заводятся не все линии адреса, чаще всего несколько старших разрядов ША. Например, если на DC завести 4 линии A19..A16, то все адресное пространство будет разбито на неперекрывающиеся блоки по 2^20 / 2^4 = 64Кб, принадлежащие каждому из 16-ти (2^4 = 16) устройств ЗУ или ВУ, подключенных к шинам (на рис.4 показаны 7 устройств). Часть из них могут использовать все отводимое им адресное пространство, например ПЗУ и ОЗУ, другие только несколько адресов.

Типовая МПС, показанная на схеме содержит:

микросхему программируемого периферийного интерфейса ППИ (PPI или IOP), к которой через три 8-битовых независимых канала PA,PB и PC можно подключать периферийные устройства, например принтер, клавиатуру, 8-ми сегментный дисплей или ЦАП и АЦП. Через ППИ может производиться обмен данными с другими МПС или ЭВМ.

Ввод с клавиатуры и вывод на дисплей могут производиться специальными микросхемами.

Связь с удаленными устройствами или абонентами сетей может осуществляться с помощью универсального асинхронного последовательного приемо-передатчика УАПП-UART (программируемый связной интерфейс ПСИ-PCI или IOS). К выводам RxD - приемник и TxD - передатчик через линию связи подключаются передатчик и приемник другого абонента или устройства. Если связь производится через модем, то доступны любые сети.

Для формирования точных, различных по частоте и длительности сигналов, в т.ч. и звукового диапазона используется программируемый интервальный таймер ПИТ-PIT, имеющий три независимых 16-ти разрядных двоичных счетчика. Задержка, длительность или частота выходного сигнала каждого счетчика кратна 3..65535 периодам входного сигнала.

Если в системе используется режим прерывания выполнения основной программы внешними устройствами, требующими безотлагательного вмешательства микропроцессора, то может применяться программируемый контроллер прерываний ПКП - PIC (устройство собирающее заявки на обслуживание от ВУ с входов IRi). Подробно прерывания будут рассмотрены ниже.

Обмен данными между МП и ЗУ или одним из ВУ возможен только при появлении на выходе дешифратора DC единственного сигнала ~CS = 0, поступающего на то устройство с которым будет производиться запись или чтение байта данных. Остальные (невыбранные) устройства будут в пассивном состоянии, т.к. их сигналы ~CS = 1. Байт информации на ШД считывается ВУ, ЗУ или МП в строго ограниченном интервале времени во время действия одного из управляющих сигналов чтения/записи (~MEMR, ~MEMW) из памяти или в память, или во время действия одного из сигналов управления вводом/выводом (~IOR, ~IOW) в/из ВУ.

Быстрый обмен данными может производиться с помощью устройства прямого доступа к памяти ПДП (DMA).

8.6 СТЕКОбласть памяти с упрощенной схемой адресации, к которой МП обращается по принципу "последним вошел - первым вышел" (LIFO). Байты программы в оперативной памяти располагаются последовательно по нарастающим адресам. Стек заполняется по последовательно убывающим адресам. Во избежание перекрытия этих двух областей памяти стек обычно располагается в старших адресах. Начальный адрес стека, называемый дном (bottom) записывается в регистр SP командой MOV SP,0fffeh. Вместо 0fffeh - адрес предпоследнего байта сегмента, может быть другое значение, но выравненное по двухбайтовым, т. е. четным адресам. Текущее значение содержимого SP называется, также адресом вершины стека (top). Если адрес вершины совпадает с адресом дна - стек считается пустым. Рассмотрим механизм помещения в стек и извлечения из него данных на примере команд PUSH AX и POP BX. Пусть начальное значение аккумулятора AX равно 874c.

Команда PUSH выполняется в четыре этапа:

Адрес в SP уменьшается на 1: (SP) <-- (SP) - 1. По этому адресу помещается старший байт 87: ((SP)) <-- (AH). Содержимое SP снова уменьшается на 1: (SP) <-- (SP) - 1. По полученному адресу загружается младший байт 4c: ((SP)) <-- (AL).Действие команды POP аналогично описанному процессу, но в происходит в обратном порядке:

(BL) <- ((SP)), (SP) <- (SP) + 1, (BH) <- ((SP)), (SP) <- (SP) + 1.Байты в стек помещаются по правилу "старший байт по старшему адресу" . На рис.7 показан пустой стек до выполнения команды PUSH AX и после ее выполнения, а на рис.8 после выполнения команды POP BX.

Преимущество стека в том, что программисту не нужно заботиться об абсолютных значениях адресов переменных, но в этом таится и опасность, если текущее содержимое указателя стека будет потеряно, при неаккуратных действиях программиста, то работа компъютера станет непредсказуемой и он, как говорят в таких случаях, "зависнет". В программах стек используется для:

1) сохранения и извлечения адреса возврата из подпрограмм командами ассемблера CALL и RET (IRET),

2) хранения локальных переменных,

3) передачи фактических параметров подпрограммам (трансляторами с языков высокого уровня),

4) временного хранения содержимого регистров фоновой программы при ее прерывании.

8.7 СПОСОБЫ ВВОДА-ВЫВОДАОбмен данными между ЭВМ и ВУ или ЗУ называется вводом-выводом (ВВ). Существует четыре основных способа ВВ.

Программный ВВ ВВ по прерываниям Прямой доступ к памяти (ПДП) или DMA Транзакции (MCS-96)В первых двух случаях в обмене данными участвует микропроцессор. В режиме ПДП функции управления обменом берет на себя специальное устройство - контроллер ПДП, причем МП в это время в обмене данными не участвует. В 4-ом способе пересылки производятся параллельно с работой МП периферийным сервером транзакций.

8.7.1 ПРОГРАММНЫЙ ВВОД-ВЫВОДДля внешних устрйств выделяеся адресное пространство, либо не входящее в состав ЗУ, либо являющееся его частью. Следовательно программный ВВ может быть двух типов:

с помощью команд ассемблера ввод (IN) и вывод (OUT) с использованием всех команд пересылки ассемблера (MOV, LODSB,..).В пределах 64K блока карта распределения памяти для первого случая показана на рис.5 слева.

В пределах интервала 0000 ...XXXX адреса ВУ и ЗУ пересекаются. Поэтому для однозначного обращения к ячейкам памяти или ВУ в процессорном блоке формируются управляющие пересылкой стробирующие импульсы - ~IOR,~IOW для ввода или вывода данных во внешнее устройство и ~MEMR,~MEMW для чтения или записи в память.Емкость ЗУ для размещения программ и данных не уменьшается.

Карта распределения памяти для второго случая показана на рис.5 справа. Под внешние устройства выделяется часть адресного пространства ЗУ. Емкость ЗУ уменьшается на количество адресов отводимых для ВУ. Второй способ позволяет адресоваться к ВУ с помощью всех команд оперирующих с памятью. Основное достоинство программного ВВ в простоте. Но при выполнении ввода, например с клавиатуры, МП затрачивает до 99,99..% времени на ожидание, не выполняя при этом другой полезной работы. Избавиться от этого недостатка позволяет ВВ по прерываниям.

8.7.2 ВВОД-ВЫВОД ПО ПРЕРЫВАНИЯЮВ общем случае прерывания могут вызываться

внешнними устройствами (внешние прерывания), командами прерываний (программные прерывания) автоматически самим МП (внутренние прерывания), например при попытке деления на 0.В этом разделе будут рассмотрены внешние прерывания. Работу МП можно разделить во времени между двумя независимыми программами: фоновой, которая выполняет основную задачу и программой ВВ данных. Когда ВУ подготовит данные для передачи, оно посылает сигнал запроса на прерывание непосредственно на вход МП INTR или в специальное устройство - контроллер прерываний. В процессе обслуживания прерывания выполняются следующие действия:

1. ВУ самостоятельно, либо через контроллер прерываний посылает сигнал прерывания INT(R) на одноименный вход МП;

2. МП завершает выполнение текущей команды и,если преывания разрешены командой ассемблера STI(EI для 8085), то подтверждает разрешение сигналом ШУ -INTA;

3. В МП по ШД передается тип(номер) прерывания - N;

4. Содержимое PSW, а также CS,IP (адрес возврата), скорректированное с учетом сброса очереди помещается в стек;

5. Сбрасываются флаги IF (флаг разрешения прерываний) и TF (флаг трассировки), причем т.к. (IF) = 0 дальнейшие прерывания запрещаются;

6. В IP загружается содержимое двух байтов с начальным адресом 4*N, а в CS - содержимое следующих двух байтов . Эти 4 байта называются вектором (указателем) прерывания.

7. Начинает выполняться подпрограмма - обработчик прерывания.

INT_SUBR:

STI

PUSH AX

....; здесь

....; команды

MOV AL,5; обработчика

....; прерывания

....

POP AX

IRET

Если допускаются вложенные прерывания, то вначале помещается команда STI- разрешение преываний, запрещенных в п.5. Инструкции push и pop сохраняют и восстанавливают содержимое регистров фоновой задачи, если эти же регистры используются и обработчиком прерывания (в примере регистр AX).

Похожие работы

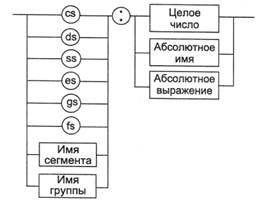

... как единое целое. Результатом вычисления выражения может быть адрес некоторой ячейки памяти или некоторое константное (абсолютное) значение. В табл. 2.2 приведены поддерживаемые языком ассемблера операторы и перечислены их приоритеты. Арифметические операторы. К ним относятся унарные операторы «+» и «-», бинарные «+» и «-», операторы умножения «*», целочисленного деления «/», получения остатка ...

... ) ФАКУЛЬТЕТ ЭЛЕКТРОНИКИ И ПРИБОРОСТРОЕНИЯ КАФЕДРА КЭС группа Э-92 ДАТА ЗАЩИТЫ апреля 1997 г. Отзыв на дипломную работу студента гр.Э-92 Сорокина Ю.В. “Разработка программы контроллера автоматически связываемых объектов для управления конструкторской документацией в среде Windows 95/NT”. Широкое использование вычислительной техники в народном хозяйстве требует увеличения производства и ...

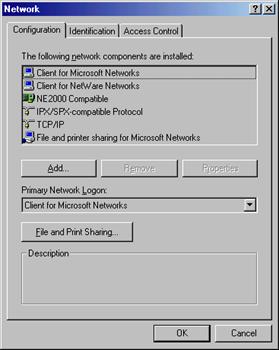

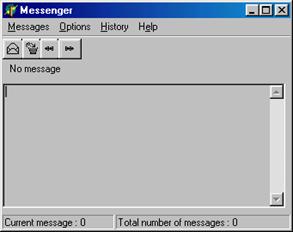

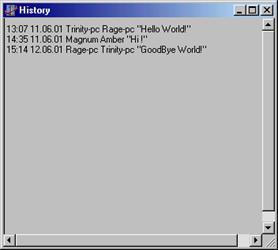

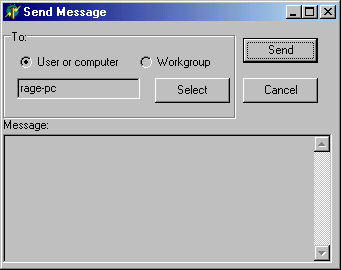

... выбрать имя в ListBox’e и нажать кнопку «OK», после чего выбранное имя автоматически отобразиться в окне получателя сообщения. Рис. 1.10. Выбор адресата получателя Поиск компьютеров в локальной сети Приведём пример кода программы, реализующую поиск компьютеров в локальной сети Microsoft. procedure TForm4. Button1Click (Sender: TObject); var Q, BufferSize: DWord; R: THandle; Buf: ^ ...

... значения низкого порога температуры, высвечивается сообщение и остается до пор, пока температура не станет выше, сохраненного значения низкого порога температуры. 3. Разработка программы Для того чтобы нам реализовать программу, необходимо компьютером считывать сигналы. Считывать сигналы будем с помощью параллельного порта LPT1. Pin In/Out Signal Name Pin In/Out Signal ...

0 комментариев