Навигация

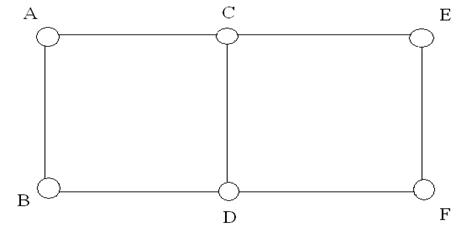

РАССМОТРЕНИЕ РАЗЛИЧНЫХ ВАРИАНТОВ ПОСТРОЕНИЯ СТРУКТУРНОЙ СХЕМЫ

3.2 РАССМОТРЕНИЕ РАЗЛИЧНЫХ ВАРИАНТОВ ПОСТРОЕНИЯ СТРУКТУРНОЙ СХЕМЫ

Исходя из назначения устройства, можно представить устройство в виде некоего блока, который обеспечивает пространственно-временную коммутацию 256ти входящих цифровых каналов, в соответствии с сигналами УСТРОЙСТВА УПРАВЛЕНИЯ, и выравнивает входящие групповые каналы по циклам. Структурная схема такого устройства показана на рисунке 3.1.

БЛОК

КОММУТАЦИИ

УСТРОЙСТВО УПРАВЛЕНИЯ

Шина обмена с внешним контроллером управления

- 2,048 Мбит/с

- Шины обмена

Рис. 3.1 Общее строение устройства коммутации.

Для обеспечения циклового выравнивания входящих групповых каналов в БЛОКЕ КОММУТАЦИИ необходим специальный блок, отвечающий за выравнивание (назовем этот блок БЛОКОМ КОММУТАЦИИ И ЦИКЛОВОГО ВЫРАВНИВАНИЯ), а для синхронизации необходимо выделить синхроимпульсы цикловой и сверхцикловой синхронизации. Тогда структурная схема примет вид, показанный на рис. 3.2. Этот вариант укрупненной структурной схемы включает в себя дополнительно БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА.БЛОК

КОММУТАЦИИ И ЦИКЛОВОГО ВЫРАВНИВАНИЯ

БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА

УСТРОЙСТВО УПРАВЛЕНИЯ

Шина обмена с внешним контроллером управления

- 2,048 Мбит/с

- Шины обмена

Рис. 3.2 Укрупненная структурная схема проектируемого устройства.

Далее необходимо рассмотреть принцип коммутации разноименных временных каналов, как отмечалось во Введении, коммутация сводится к перестановке импульсов из одной временной позиции в другую. Но в данном случае такая перестановка возможна только в одном групповом канале, а нам необходимо скоммутировать 8 групповых каналов, т.е. помимо временной коммутации необходима еще и пространственная. Такие требования существенно усложняют проектируемое устройство и поэтому необходимо рассмотреть возможность исключения пространственной коммутации, этого можно добиться объединением входящих групповых каналов в один общий канал с пропускной способностью 16,384 Мбит/c.

2,048 [Мбит/с] * 8 = 16,384 [Мбит/с]. (3.1)

Такое преобразование канала должен выполнять специальный БЛОК ФОРМИРОВАНИЯ ОБЩЕГО КАНАЛА, тогда вся коммутация будет осуществляться только во временной области и это упростит решение задачи построения коммутационного блока. До этого блока необходимо выровнять входящие каналы по циклам, поэтому цикловое выравнивание следует выполнять в отдельном БЛОКЕ ЦИКЛОВОГО ВЫРАВНИВАНИЯ. При таком построении схемы на выходе БЛОКА КОММУТАЦИИ будет сформирован общий канал со скоростью передачи 16,384 Мбит/с, его необходимо разделить на 8 исходящих групповых каналов, для этого требуется БЛОК ОБРАТНОГО ПРЕОБРАЗОВАНИЯ. Структурная схема, отвечающая вышеперечисленным требованиям, изображена на рис. 3.3.

УСТРОЙСТВО УПРАВЛЕНИЯ

2,048 Мбит/с

16,384 Мбит/с

Шины обмена

Шина обмена с внешним контроллером управления

Рис. 3.3 Первичный вариант структурной схемы.

При всех достоинствах данного построения, у этой структурной схемы существует недостаток, который заключается во внутреннем умножении тактовой частоты в 8 раз, что накладывает свой отпечаток на построение устройства в целом. В качестве прототипа мне была предложена следующая схема построения устройства (см. рис. 3.4), здесь предложено распараллелить общий канал на 2 канала, по которым поступают четные и нечетные импульсы, это позволяет снизить умножение частоты в два раза, другими словами пропускная способность каждого из внутренних каналов составляет 8,192 Мбит/с.

( 2,048 [Мбит/с] * 8 ) / 2 = 8,192 [Мбит/с]. (3.2)

Такое построение схемы позволяет частично компенсировать недостатки предыдущей схемы и в конечном итоге снизить требования к быстродействию отдельных элементов схемы. В структурной схеме прототипа была реализована возможность объединения нескольких блоков со сходными функциями в один. В результате преобразования блоки ЦИКЛОВОГО ВЫРАВНИВАНИЯ, ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА и БЛОК ФОРМИРОВАНИЯ ОБЩЕГО КАНАЛА были объединены в БЛОК ЦИКЛОВОГО ВЫРАВНИВАНИЯИ ПРЕОБРАЗОВАНИЯ КОДА ИКМ-30/32. А БЛОКОБРАТНОГО ПРЕОБРАЗОВАНИЯ был переименован в БЛОК ОБРАТНОГО ПРЕОБРАЗОВАНИЯ КОДА. Преобразованная структурная схема устройства коммутации представлена на рис. 3.4.

УСТРОЙСТВО УПРАВЛЕНИЯ

Шина обмена с внешним контроллером управления

2,048 Мбит/с

8,192 Мбит/с

Шины обмена

Рис. 3.4 Структурная схема прототипа.

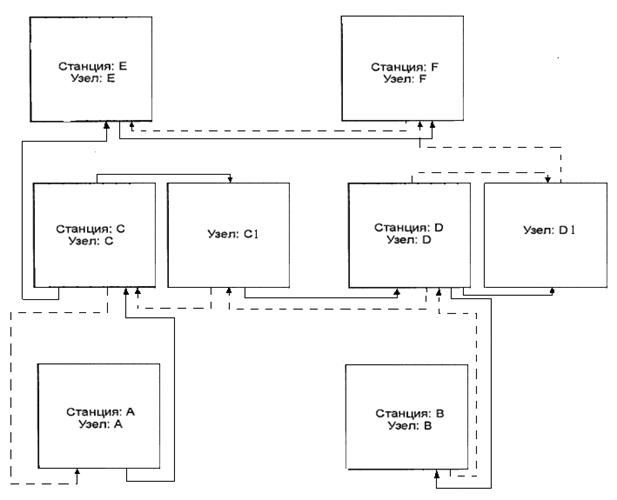

Логичным продолжением рассмотренных вариантов структурных схем, на мой взгляд, является вариант схемы, где общий канал распараллеливается на 8 каналов, что позволяет снизить внутреннюю пропускную способность каналов до 2,048 Мбит/с и, соответственно, не производить внутреннего умножения частоты. Это позволяет существенно снизить требования к быстродействию внутренних элементов и упростить схемотехнику устройства. При детальном рассмотрении структуры можно заметить, что для обеспечения циклового выравнивания входящих групповых каналов необходимо запомнить информацию из этих каналов, приходящую в разное время, а затем начать считывание информации по сигналу синхронизации из УСТРОЙСТВА УПРАВЛЕНИЯ. Как показано во Введении, для выполнения временной коммутации также необходимо запомнить приходящую информацию, а затем считывать эту информацию в порядке соответствующим карте коммутации. Отсюда несложно сделать вывод о целесообразности объединения блоков ЦИКЛОВОГО ВЫРАВНИВАНИЯ и КОММУТАЦИИ, а БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА можно оставить в виде отдельного блока. Такая структурная схема представлена на рис. 3.5.

Рассмотрим подробнее назначение блоков и их отличия от прототипа:

БЛОК ЦИКЛОВОГО ВЫРАВНИВАНИЯ И КОММУТАЦИИ предназначен для приема 8ми входящих групповых каналов формата ИКМ – 30/32 их последующего выравнивания, временного уплотнения и коммутации. По сравнению с прототипом такое объединение функций позволило снизить внутреннюю частоту с 8192 кГц до 2048 кГц, т.е. в четыре раза, а задержку передачи информации с 2 – 3 циклов в прототипе, до 1 - 2 за счет объединения функций коммутации и выравнивания в одном блоке. Снизить внутреннюю частоту до тактовой частоты входного сигнала стало возможным из-за пространственного распараллеливания разрядов уплотненного общего канала и передачи этих разрядов по параллельной шине. А так как все восемь разрядов информационного канала всегда коммутируются по одному адресу, то пространственной коммутации не требуется, а весь процесс коммутации сводится, как показано выше лишь к перестановке канала из одной временной позиции в другую.

БЛОК ВЫДЕЛЕНИЯ ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА предназначен для выделения из информационных каналов потока ИКМ – 30/32 сигналов цикловой и сверхцикловой синхронизации, которые позволяют синхронизировать работу устройства в целом и выровнять входящие групповые каналы. Этот блок принципиально не отличается от аналогичного блока в прототипе.

БЛОК ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ предназначен для преобразования скоммутированного уплотненного временного канала в 8 выходных групповых каналов и вставки в них служебных каналов, пришедших из УСТРОЙСТВА УПРАВЛЕНИЯ. Принципиальным отличием от аналогичного блока в прототипе является отсутствие повышенной тактовой частоты входящего уплотненного канала и наличие 8ми разрядной шины на входе блока.

ГЛАВА 4

ВЫБОР СХЕМО-ТЕХНОЛОГИИ ПРОЕКТИРУЕМОЙ БИСКРАТКИЙ ОБЗОР СУЩЕСТВУЮЩИХ СХЕМО-ТЕХНОЛОГИЙ ПРИМЕНЯЕМЫХ В ИНТЕГРАЛЬНЫХ СХЕМАХ

Рассмотрим наиболее распространенные схемотехнологии применяемые в интегральных схемах:Транзисторно-транзисторная логика (ТТЛ).

Эмиттерно-связанная логика (ЭСЛ).

Логика, построенная на основе структуры метал-диэлетрик-полупроводник с п-каналом (пМДП).

Логика, построенная на основе структуры метал-диэлетрик-полупроводник с транзисторами разной проводимости (КМДП).

ТЕХНОЛОГИЯ ТТЛ.

Технология ТТЛ основана на биполярных структурах. Базовый элемент ТТЛ представляет собой схему, содержащую один многоэмиттерный транзистор и один обычный (см. рис. 5.1), это логическая схема И-НЕ (функцию И выполняет транзистор VT1, а функцию инверсии выполняет транзистор VT2).

Рис. 5.1. Базовый элемент ТТЛ.

Подобная схема обладает низкой помехоустойчивостью и низким быстродействием, быстродействие можно увеличить, используя сложный инвертор, который позволяет сократить время включения (переход из логического «0» в логическую «1»); но время выключения (переход из логической «1» в логический «0») сократить, не удается.

Более высокое быстродействие позволяют получить схемы субсемейства ТТЛШ (транзисторно-транзисторная логика с использованием транзисторов с барьером Шотки; см. рисунок 5.2). В таких схемах барьер Шотки создает нелинейную обратную связь в транзисторе, в результате транзисторы не входят в режим насыщения, хотя и близки к этому режиму. Следовательно, практически исключается время рассасывания, что позволяет существенно увеличить быстродействие.

Р

ис. 5.2. Транзистор Шотки.

ТЕХНОЛОГИЯ ЭСЛ.

Т

ехнология ЭСЛ является так же, как и технология ТТЛ, биполярной, т.е. элементы строятся с использованием биполярных структур. Основой элементов ЭСЛ является так называемый «переключатель тока», на основе которого строится базовый элемент этой технологии - ИЛИ- -НЕ (см. рис. 5.3); по выходу1 данной схемы реализуется логическая функция ИЛИ-НЕ, а по выходу2 - ИЛИ.

Рис. 5.3. Базовый элемент ЭСЛ.

Из-за низкого входного сопротивления схемы ЭСЛ обладают высоким быстродействием и работают преимущественно в активном режиме, следовательно, помеха попавшая на вход усиливается. Для повышения помехоустойчивости шину коллекторного питания делают очень толстой и соединяют с общей шиной.

По сравнению со схемами ТТЛ схемы ЭСЛ обладают более высоким быстродействием, но помехоустойчивость у них гораздо ниже. Схемы ЭСЛ занимают большую площадь на кристалле, потребляют большую мощность в статическом состоянии, так как выходные транзисторы открыты и через них протекает большой ток. Схемы, построенные по данной технологии не совместимы со схемами, построенными по другим технологиям, использующим источники положительного напряжения.

ТЕХНОЛОГИЯ пМДП.

В отличие от технологий, рассмотренных выше, технология пМДП основана на МДП - структурах, которые обеспечивают следующие преимущества по сравнению с биполярными:

Входная цепь (цепь затвора) в статическом режиме практически не потребляет тока (высокое входное сопротивление);

Простая технология производства и меньшая занимаемая площадь на кристалле.

О

сновными логическими схемами изготовлеваемыми на основе пМДП являются схема ИЛИ-НЕ и И-НЕ (см. рис. 5.4 и рис. 5.5).

Р

ис. 5.4. Схема ИЛИ-НЕ.

Рис. 5.5. Схема И-НЕ.

К недостаткам этих схем можно отнести невысокое быстродействие, по сравнению со схемами ТТЛШ и ЭСЛ. Но в настоящее время благодаря применению новых технологий (окисная изоляция, использование поликремневых затворов, технология «кремний на сапфире») создаются быстродействующие МДП структуры.

Похожие работы

... эксплуатации (станционный сервер). Подключение выполняется посредством соединения через COM-порт или через соединение локальной сети Ethermet 100 Мбит/с. Связь сервера с терминалами центра управления осуществляется посредством локальной сети. 6. Цифровые системы уплотнения аналоговых линий Задача таких систем заключается в экономии физических линий связи, когда на одну пару телефонной линии ...

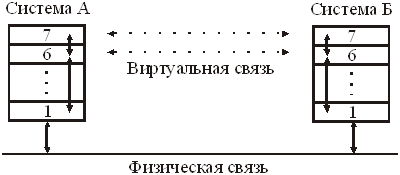

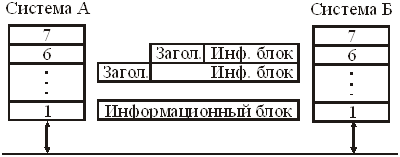

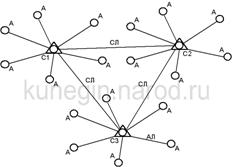

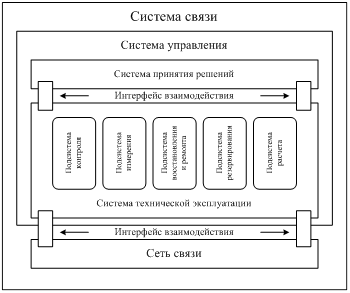

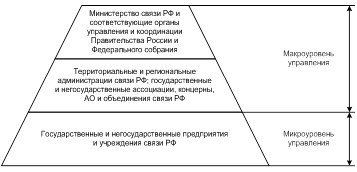

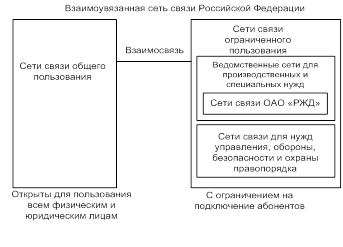

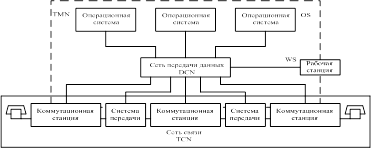

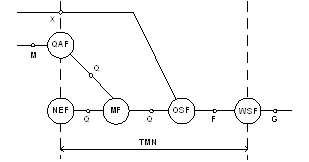

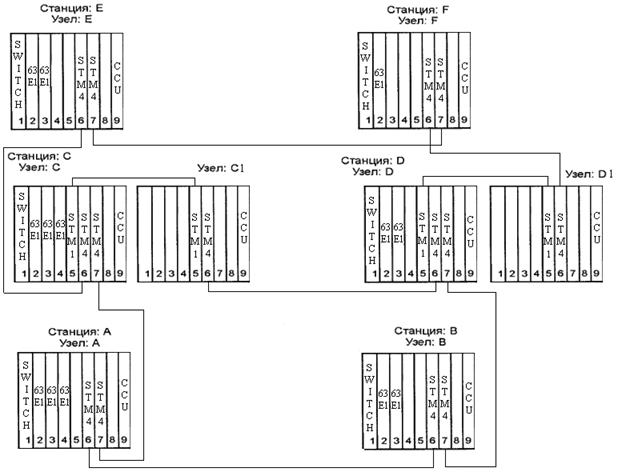

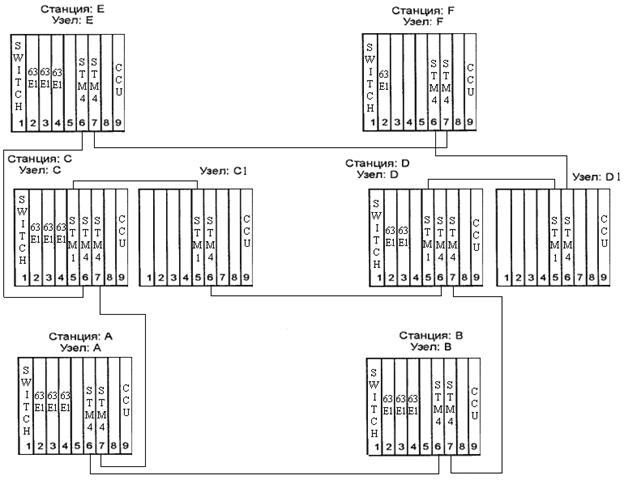

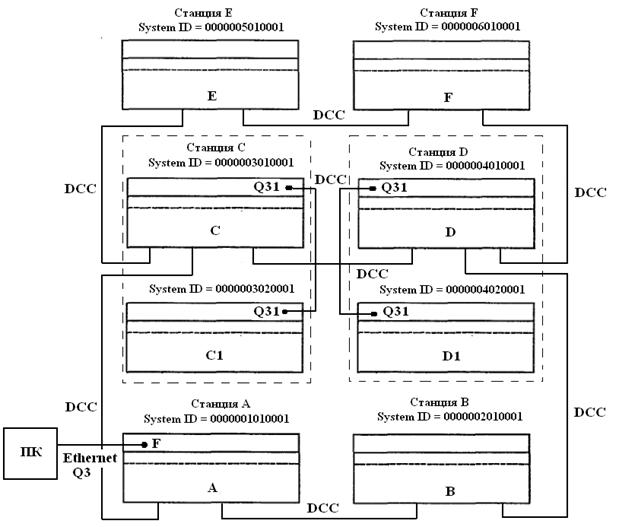

... Каждому элементу соответствует численный и символьный идентификатор. В имя переменной включается полный путь до нее от корневого элемента root. 3. Система мониторинга и администрирования 3.1 Системы управления технологическим сегментом магистральной цифровой сети связи ОАО «РЖД» РФ При построении современных цифровых сетей следует различать следующие сетевые уровни: уровень первичной ...

... ПО. Центральное ПО может взаимодействовать с другими функциональными блоками в центральном процессоре. Взаимодействие функциональных блоков всегда происходит на уровне CP. 3 Виды доступа В коммутационной системе AXE-10 используется различное оборудование доступа, которое позволяет строить сети с достаточной гибкостью. К этому оборудованию относится следующее: - Удаленный абонентский ...

... нм; - STM-4 L-4.2 - модуль оптического приемопередатчика организует один оптический интерфейс STM-4 (или STM-4c), связанный с модулем кроссовой коммутации, работает на длине волны 1550 нм; - STM-16 - модуль оптического компонентного интерфейса; - Gigabit Ethernet - модуль позволяет организовать передачу данных в формате Gigabit Ethernet с сетевой топологией «точка-точка»; - 63 Е1 - плата ...

0 комментариев