Навигация

5.1.4. ТЕХНОЛОГИЯ КМДП.

Следующим шагом развития МДП технологии стало использование комплиментарных МДП транзисторов, т.е. транзисторов с разным типом проводимости, причем основными являются транзисторы п-типа; а транзисторы р-типа используются в качестве динамической нагрузки.

Использование КМДП-схем по сравнению со схемами пМДП позволяет снизить потребляемую мощность, повысить быстродействие и помехоустойчивость, однако это достигается за счет увеличения площади занимаемой на кристалле и усложнения технологии производства.

Б

азовыми элементами КМДП-схем являются, как и для пМДП, логические элементы ИЛИ-НЕ и И-НЕ (см рис.

5.6 и 5.7).

Р

ис. 5.6. Схема ИЛИ-НЕ.

Рис. 5.7. Схема И-НЕ.

К особенностям интегральных схем, построенных по технологии КМДП можно отнести следующее:

Чувствительность к статическому электричеству (для защиты в буферные каскады ставятся диоды);

Тиристорный эффект (в КМДП структурах образуются паразитные биполярные, подобные тиристору, структуры между шинами питания). При включении питания тиристор включается и замыкает шину «+» на общую шину (для защиты используется окисная изоляция).

ВЫБОР СХЕМОТЕХНОЛОГИИ ПОСТРОЕНИЯ БИС

При сравнении рассмотренных выше схемотехнологий не трудно придти к следующим выводам:

В биполярных технологиях базовым является элемент реализующий лишь одну логическую функцию (И-НЕ в ТТЛ(Ш) и ИЛИ-НЕ в ЭСЛ), в то время как базовыми в МДП технологиях являются и те и другие логические элементы. Конечно, можно любую логическую функцию перевести в базисы И-НЕ или ИЛИ-НЕ, но это усложняет и процесс создания схемы, и саму схему. Следовательно с этой позиции схемы предпочтительней строить на основе МДП структур.

Так как внутреннее умножение частоты в проектируемой БИС было устранено, то быстродействие не играет значительной роли, следовательно, технология ЭСЛ отпадает; так как интегральные схемы, построенные по данной технологии, потребляют значительную мощность и менее помехоустойчивы, чем все остальные; а для обеспечения питания таких схем необходимы специальные каскады.

У схем МДП более простая технология изготовления, что сказывается на себестоимости всего устройства в целом, следовательно, с этих позиций технология МДП предпочтительней биполярной.

В результате анализа различных технологий (см. ГЛАВА 9) было отдано предпочтение технологии КМДП, как наиболее оптимальной для решения данной задачи.

СХЕМЫ КМДП С ТРЕЬИМ СОСТОЯНИЕМ

Для решения некоторых задач, например, таких как подключение нескольких устройств к одной шине, используются схемы с третьим состоянием. Помимо двух логических уровней у такой схемы есть еще одно - третье состояние, в котором выход (иногда вход) схемы отключен, и сигналы проходящие по шине в этот момент не влияют на элементы данной схемы, и в тоже время на шину не поступают сигналы от отключенных таким способом элементов. В результате схемы с третьим состоянием позволяют избежать наложения сигналов от разных устройств, подключенных к одной шине и, следовательно, избежать помех в общих для нескольких устройств проводниках. Так как для построения схемы была выбрана технология КМДП, то рассмотрим схему с тремя состояниями на примере инвертора построенного по технологии КМДП, схема этого устройства изображена на рисунке 5.8.

Транзисторы VT1 и VT2 представляют собой обычный КМДП инвертор, подключенный к источнику питания и общей шине через транзисторные ключи, построенные на транзисторах VT3 и VT4.

Р

ис. 5.8. Схема КМДП с тремя состояниями.

Рассмотрим принцип работы данной схемы. Управление ей осуществляется двумя входами Z и Z. Если на вход Z подать напряжение логической единицы, то транзисторы VT3 и VT4 откроются и схема работает как обычный инвертор, а при подаче на управляющий вход напряжения логического нуля транзисторы VT3 и VT4 закроются и на выходе схемы окажется очень большое сопротивление. Таблица истинности такого элемента сведена в таблицу 5.1.

Таблица 5.1.

| Вход | Z | Z | Выход |

0 1 0 1 | 0 0 1 1 | 1 1 0 0 | Отключен Отключен 1 0 |

ГЛАВА 5

РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ПРОЕКТИРУЕМОЙ ЗАКАЗНОЙ БИСЛюбое цифровое устройство предназначено для выполнения той или иной логической функции, следовательно, такое устройство можно представить в виде элементарных ячеек, таких как НЕ, И-НЕ, ИЛИ-НЕ. Рассмотрим их схемы и принцип работы. Из-за того, что разработка элементов велась на программе схемотехнического моделирования в стандарте ANSI, то обозначения элементов не совпадают принятыми в нашей стране; соответствие элементов показано на рисунке 6.1.

Рис. 6.1. Таблица соответствия элементов.

ЯЧЕЙКА НЕ (ИНВЕРТОР).

Инвертор представляет собой элемент, с помощью которого реализуется логическая функция НЕ, т.е. при поступлении на вход логической единицы на выходе образуется логический ноль, а при поступлении на вход логического нуля на выходе образуется логическая единица. Результат схемотехнического моделирования и таблица истинности данного элемента представлены на рисунке 6.2.

Принцип работы этой схемы заключается в следующем, при поступлении на вход напряжения логической единицы транзистор VT1 открывается, а VT2 закрывается, напряжение на выходе падает до величины логического нуля (см. осциллограмму на рисунке 6.2). При подаче на вход схемы напряжения логического нуля транзисторы VT1 закрывается, а VT2 открывается, на VT1 возникает падение напряжения и напряжение на выходе начинает возрастать до величины логической единицы (см. осциллограмму на рисунке 6.2).Рис. 6.2. Схема инвертора.

ЯЧЕЙКА ИЛИ-НЕ

Схема ИЛИ-НЕ представляет собой элемент, который при поступлении хотя бы на один его из входов напряжения логической единицы выдает на выходе логический ноль, в противном случае на выходе схемы ИЛИ-НЕ будет логическая единица.

Ячейка ИЛИ-НЕ на два входа представлена на рисунке 6.3. Рассмотрим принцип работы данного элемента. При поступлении напряжения логической единицы на один из входов схемы, один из входных транзисторов (VT1 или VT2) открывается, а соответствующий ему нагрузочный транзистор (VT3 или VT4) закрывается, в результате выход оказывается подключенным к «земле», т.е. на выходе образуется логический ноль. При поступлении на оба входа схемы напряжения логического нуля, транзисторы VT1 и VT2 закрываются, а нагрузочные транзисторы наоборот открываются, в результате на закрытых транзисторах образуется падение напряжения и на выход схемы поступает напряжение логической единицы. На осциллограмме (см. рис. 6.3) представлены эпюры напряжений на входах и выходе схемы, иллюстрирующие работоспособность данного элемента, на этом же рисунке представлена таблица истинности элемента ИЛИ-НЕ.

Иногда требуются схемы ИЛИ-НЕ с большим количеством входов. Для построения таких схем достаточно добавить по два транзистора на каждый вход, транзистор п-типа подключить параллельно другим транзисторам п-типа, а транзистор р-типа подключить последовательно другим транзисторам р-типа. Схема ИЛИ-НЕ на три входа изображена на рисунке 6.4. Принцип работы данной схемы не отличается от принципа работы схемы ИЛИ-НЕ на два входа.

Р

ис. 6.3. Ячейка ИЛИ-НЕ на два входа.

Рис. 6.4. Схема ИЛИ-НЕ на три входа.

ЯЧЕЙКА И-НЕ

Схема И-НЕ представляет собой элемент, который при поступлении на все входы напряжения логической единицы выдает на выходе напряжение логического нуля, в противном случае на выходе будет логическая единица.

Схема И-НЕ на два входа представлена на рисунке 6.5. Рассмотрим принцип работы данного элемента. При поступлении хотя бы на один из входов напряжения логического нуля один из входных транзисторов (VT1 или VT2) закрывается, на нем образуется падение напряжения, а один из нагрузочных транзисторов (VT3 или VT4) открывается, в итоге на выходе образуется напряжение логической единицы. При поступлении на оба входа напряжения логической единицы, оба транзистора VT1 и VT2 открываются, а транзисторы VT3 и VT4 закрываются, и выход оказывается подключен к «земле», другими словами на выходе действует напряжение логического нуля.

Рис. 6.5. Схема И-НЕ на два входа.

Иногда требуются схемы И-НЕ с большим количеством входов. Для построения таких схем достаточно добавить по два транзистора на каждый вход, транзистор п-типа подключить последовательно другим транзисторам п-типа, а транзистор р-типа подключить параллельно другим транзисторам р-типа. Схема ИЛИ-НЕ на три входа изображена на рисунке 6.6. Принцип работы данной схемы не отличается от принципа работы схемы ИЛИ-НЕ на два входа.

Рис. 6.6 Схема И-НЕ на три входа.

Похожие работы

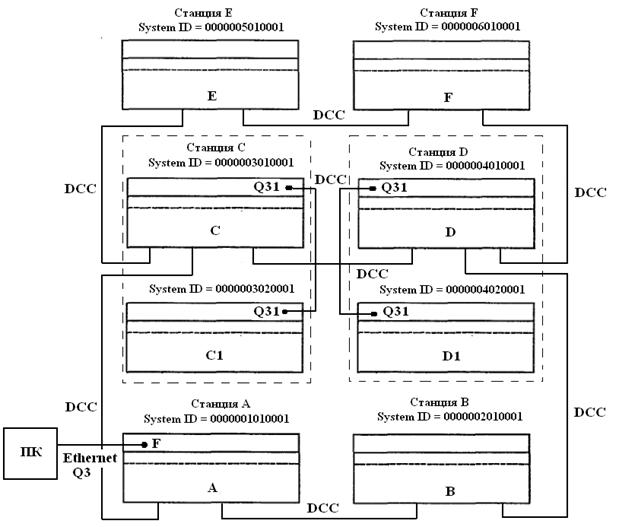

... эксплуатации (станционный сервер). Подключение выполняется посредством соединения через COM-порт или через соединение локальной сети Ethermet 100 Мбит/с. Связь сервера с терминалами центра управления осуществляется посредством локальной сети. 6. Цифровые системы уплотнения аналоговых линий Задача таких систем заключается в экономии физических линий связи, когда на одну пару телефонной линии ...

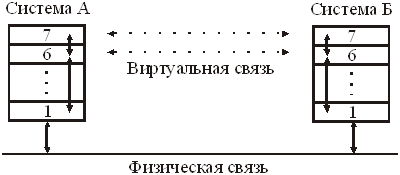

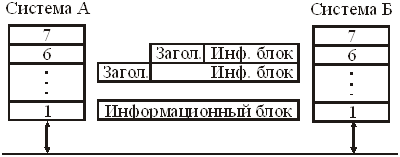

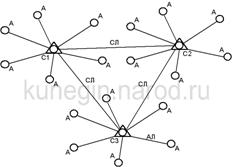

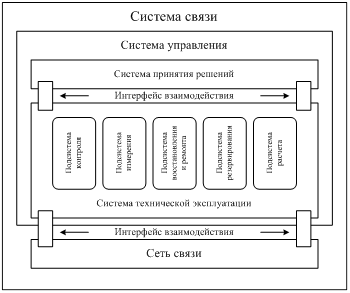

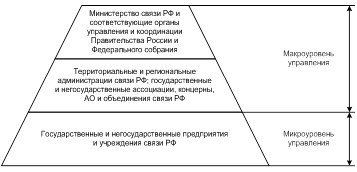

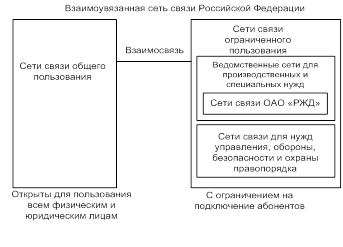

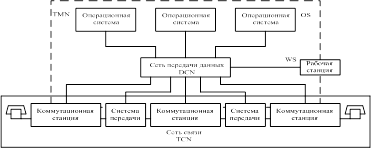

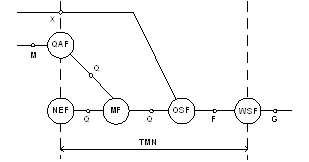

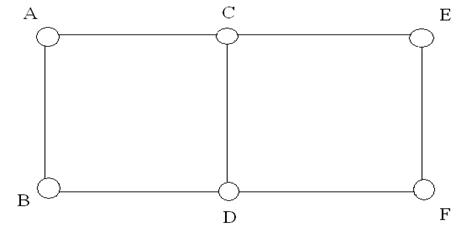

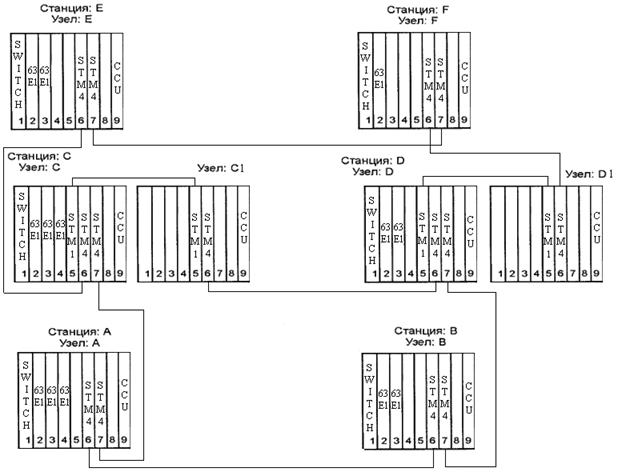

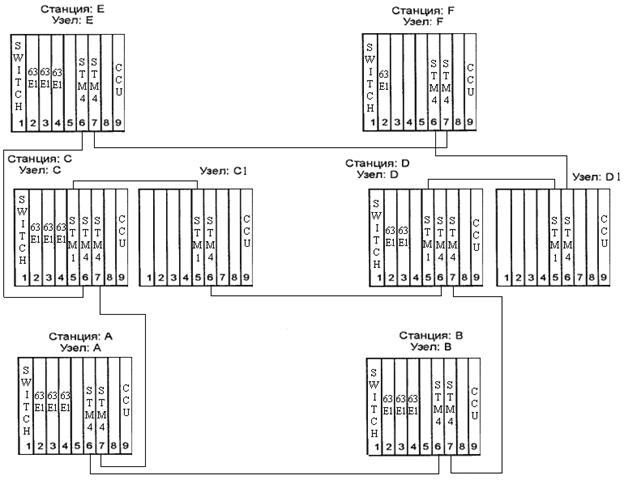

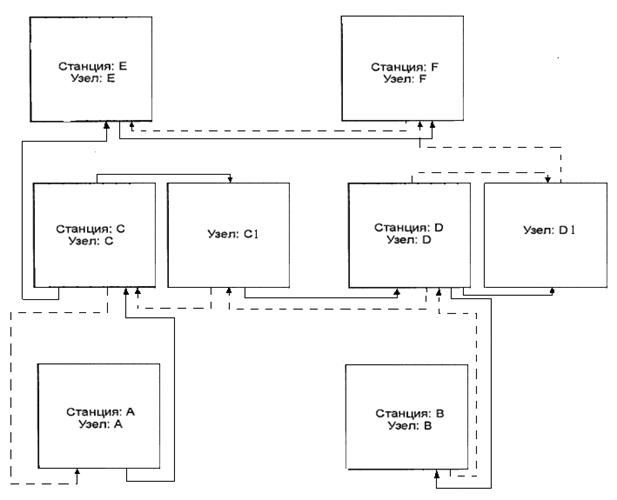

... Каждому элементу соответствует численный и символьный идентификатор. В имя переменной включается полный путь до нее от корневого элемента root. 3. Система мониторинга и администрирования 3.1 Системы управления технологическим сегментом магистральной цифровой сети связи ОАО «РЖД» РФ При построении современных цифровых сетей следует различать следующие сетевые уровни: уровень первичной ...

... ПО. Центральное ПО может взаимодействовать с другими функциональными блоками в центральном процессоре. Взаимодействие функциональных блоков всегда происходит на уровне CP. 3 Виды доступа В коммутационной системе AXE-10 используется различное оборудование доступа, которое позволяет строить сети с достаточной гибкостью. К этому оборудованию относится следующее: - Удаленный абонентский ...

... нм; - STM-4 L-4.2 - модуль оптического приемопередатчика организует один оптический интерфейс STM-4 (или STM-4c), связанный с модулем кроссовой коммутации, работает на длине волны 1550 нм; - STM-16 - модуль оптического компонентного интерфейса; - Gigabit Ethernet - модуль позволяет организовать передачу данных в формате Gigabit Ethernet с сетевой топологией «точка-точка»; - 63 Е1 - плата ...

0 комментариев