Навигация

6.4 ЭЛЕМЕНТЫ «И» И «ИЛИ»

Элементы И и ИЛИ получаются добавлением на выход элементов И-НЕ и ИЛИ-НЕ инверторов, в результате двойного логического отрицания на выходе схемы получается требуемая логическая функция. Эквивалентные логические схемы элементов И и ИЛИ представлены на рисунках 6.7 и 6.8.

Р

ис. 6.7. Эквивалентная схема элемента И.

Рис. 6.7. Эквивалентная схема элемента ИЛИ.

6.5 ЯЧЕЙКА ПАМЯТИ

Ячейка памяти является еще одним базовым элементом, на основе которого строятся запоминающие устройства различных блоков. Ячейка памяти предназначена для хранения информации поступившей по входной шине и считывания информации по выходной шине, причем ячейка должна памяти должна обеспечивать координатную выборку информации. Ячейка памяти представляет собой простейший триггер, содержащий две пары КМДП транзисторов и два п-канальных транзистора в качестве ключей (см. рис. 6.8). Необходимо отметить, что при разработке элементов ячейки памяти учитывались требования миниатюризации с одн

ой стороны и требования обеспечения определенного запаса по быстродействию с другой.

Рис. 6.8. Принципиальная схема запоминающей ячейки.

Рассмотрим принцип работы данной ячейки. При поступлении напряжения логической единицы на адресный вход (Адрес), транзисторы VT5 и VT6 открываются и триггер, собранный на VT1 - VT4, начинает работать в обычном режиме, т.е. при поступлении на вход логической единицы, на выходе образуется логический ноль, и, наоборот, при поступлении логического нуля, на выходе образуется логическая единица. Это происходит из-за того, что один из транзисторов VT1 или VT2 открыт, т.к. они включены в противофазе. Транзисторы VT3 и VT4 играют роль динамической нагрузки. Если использовать один из входов триггера для записи информации (Запись), а с другого эту информацию считывать (Считывание), то получится ячейка памяти, но с инверсным выходом, т.к. считанные сигналы необходимо усилить, то это можно сделать при помощи инвертирующих усилителей считывания.

Для объединения ячеек памяти в единое запоминающее устройство необходимо объединить в общие шины входные и выходные выводы, так чтобы была возможность записывать и считывать информацию в соответствии с функциональными требованиями, а выводы выбора адреса объединить в одну параллельную шину. Схема фрагмента запоминающего устройства из четырех ячеек приведена на рисунке 6.9.

Рис. 6.9. Схема объединения запоминающих ячеек.

Результаты разработки топологии запоминающих ячеек проектируемой БИС рассмотрены в ГЛАВЕ 7, там же рассмотрен принцип размещения ячеек на одном кристалле.

ГЛАВА 6

РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ПРОЕКТИРУЕМОЙ БИСДля построения принципиальной схемы на основе функциональной необходимо разработать библиотеку элементов. Библиотека элементов включает в себя наиболее часто используемые элементы функциональной схемы, такие как счетчики, триггеры и др. Библиотечные элементы составляются из базовых ячеек, разработанных ранее. Затем библиотечные элементы объединяются на одной принципиальной схеме.

РАЗРАБОТКА БИБЛИОТЕКИ ЭЛЕМЕНТОВ

ТАКТИРУЕМЫЙ D-ТРИГГЕР

Т

актируемые D-триггеры используются в схеме приемника циклового и сверхциклового синхронизма (на них собран регистр сдвига); у тактируемого триггера добавлен еще один вход для синхроимпульса, по которому и срабатывает триггер. Схема D-триггера, обозначение и таблица переходов приведены на рисунке 7.1.

Рис. 7.1. Схема D-триггера.

Рассмотрим принцип работы триггера, его схема содержит два входа: один информационный (D), а другой синхронизирующий (C). При подаче логического нуля на вход С, как видно из осциллограмм, состояние триггера не изменяется, т.к. сигнал не проходит через элементы И-НЕ на входе схемы, и следовательно состояние триггера не изменяется. При подаче на вход С напряжения логической единицы, поступающий на вход D сигнал изменит состояние триггера, т.к. на один из входных элементов И-НЕ поступит единица. При поступлении логической единицы на вход D (на входе С действует напряжение логической единицы), триггер перейдет в состояние, когда на выходе Q действует напряжение логической единицы; а при поступлении логического нуля триггер перейдет в состояние, когда на выходе Q действует напряжение логического нуля.

СЧЕТЧИКИ.

С

четчики присутствуют во всех частях схемы. Простейшим двоичным счетчиком будет обыкновенный делитель на два, который при поступлении на вход импульса, на выходе будет выдавать логическую единицу до тех пор, пока на вход не поступят еще

один импульс. Такой делитель можно собрать на одном D-триггере, соединив выход Q со входом D и снимая информацию с этого же выхода. Двухразрядный счетчик импульсов получится объединении двух делителей на два, причем вход С второго делителя необходимо присоединить к выходу Q первого делителя. Схема двухразрядного двоичного счетчика приведена на рисунке 7.2.

Рис. 7.2. Схема простейшего двухразрядного счетчика.

Принцип работы данной схемы заключается в следующем, при подаче первого импульса на вход схемы (Т) входной триггер переходит в состояние, когда на выходе Q действует логический ноль, при этом на инверсном выходе образуется логическая единица, поступающая на вход D. Следовательно, при поступлении следующего импульса логическая единица на входе D «перебросит» триггер в состояние, когда на выходе Q начинает действовать логическая единица, запускающая второй триггер, который работает аналогичным образом. Таким образом, на выходах схемы формируется последовательность двоичных чисел (см. осциллограммы на рис. 7.2), сначала 00, затем 01, затем 10 и, наконец, 11; после поступления следующего импульса на вход Т, на выходе снова образуется 00.

У

приведенного выше счетчика существует один недостаток, его нельзя «сбросить» в исходное, нулевое состояние. Этот недостаток легко устраним, т.к. у D-триггера имеется возможность вывести еще один вход для сброса триггера в нулевое состояние ®, тогда схема такого счетчика примет следующий вид (см. рис. 7.3).

Рис. 7.3 Двухразрядный счетчик.

Принцип работы данной схемы не отличается от принципа работы схемы приведенной выше, за исключением того, что в нулевое состояние (на выходе 00) эту схему можно перевести в любой момент времени по сигналу R.

П

ри необходимости увеличить разрядность счетчика можно, добавляя в схему новые триггеры (таким образом строятся схемы на 3, 4 и более разрядов), но иногда возникает необходимость сбросить не все выходы счетчика, а лишь один разряд. Такую схему можно построить, добавив элемент ИЛИ-НЕ, подключенный к триггеру обслуживающему заданный разряд. Рассмотрим схему четырехразрядного счетчика, с возможностью сброса четвертого разряда. Схема такого устройства представлена на рисунке 7.4.

Рис. 7.4. Схема четырехразрядного счетчика с возможностью сброса четвертого разряда.

Принцип работы данной схемы практически не отличается от принципа работы счетчика, рассмотренного выше, кроме того, что сброс четвертого разряда может осуществляться как вместе со сбросом всего счетчика, так и отдельно, для этого в схему добавлен элемент ИЛИ-НЕ.

ДЕШИФРАТОРЫ

Д

ешифраторы, как и счетчики, встречаются во всех элементах схемы. Применяемые в устройстве дешифраторы являются позиционными, они преобразуют двоичный код в импульс на соответствующем коду номере выхода. Для построения такой схемы, в отличие от предыдущих, не нужно использовать элементы с памятью (такие как триггеры), ее можно собрать лишь из схем НЕ и И. Схема трехразрядного дешифратора представлена на рисунке 7.5.

Рис. 7.5. Схема трехразрядного дешифратора.

Схема работает следующим образом, при поступлении кодовой комбинации (от 000 до 111) на вход ищется совпадение (при помощи схем И) и на соответствующий выход поступает напряжение логической единицы. Инверторы требуются для преобразования кодовых комбинаций, содержащих логические нули.

В разрабатываемой БИС существует необходимость и в дешифраторах на большее количество разрядов (4 и 5), поэтому необходимо рассмотреть схемы таких дешифраторов. Принципы функционирования таких схем не отличаются от принципа функционирования трехразрядного дешифратора, только количество схем совпадения (И) увеличивается в соответствии с увеличением выходов (N):

N = 2n;[7.1]

где n - количество входов, и количество инверторов увеличится до количества входов.

Схема дешифратора на четыре входа представлена на рисунке 7.6. Аналогично строится схема и пятиразрядного дешифратора.

Р

ис. 7.5. Схема четырехразрядного дешифратора.

МУЛЬТИПЛЕКСОР

Мультиплексор является устройством, подключающим один из входов к выходу по сигналу управления. В схеме проектируемого устройства мультиплексор встречается всего один раз, но так как схема его получается достаточно простой, то было решено вынести мультиплексор в библиотеку элементов. У разрабатываемого мультиплексора 10 информационных входов, разбитых на две группы по 5 входов, и 5 выходов, к которым подключается соответствующая группа входов, управление производится при помощи одного управляющего входа. Схема такого мультиплексора представлена на рисунке 7.6.

Рассмотрим принцип работы данной схемы, при поступлении на вход А уровня логического нуля через инвертор подключаются схемы совпадения для первой группы входов, при прохождении через любой из входов этой группы сигнала логической единицы, одна из схем И срабатывает и выдает на своем выходе напряжение логической единицы, через схему ИЛИ подключены выходы, и при поступлении на один из входов схемы ИЛИ, сигнал проходит на выход. При подаче напряжения логической единицы на вход А первая группа входов отключается, и подключается вторая группа входов, схема работает в аналогичном первому случаю режиме, только на выход поступают сигналы со второй группы входов. Этот принцип работы хорошо иллюстрируется при помощи осциллограмм приведенных на рисунке 7.6.

Рис. 7.6. Схема мультиплексора.

РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ СХЕМ БЛОКОВ ПРОЕКТИРУЕМОЙ БИС

РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ПРИЕМНИКА ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА

Разработку принципиальной схемы на основе разработанной библиотеки элементов необходимо вести по функциональной схеме данного блока. В функциональной схеме имеется регистр сдвига на тактируемых триггерах (следовательно, нам понадобятся 8 D-триггеров), схемы совпадения собраны на собраны на элементах И (на 4 и на 6 входов), счетчики и дешифраторы также являются библиотечными элементами, следовательно, по сравнению с функциональной схемой принципиальная не несет в себе изменений. Принципиальная схема, построенная с помощью программы схемотехнического моделирования, представлена на рисунке 7.7, единственным отличием, связанным со спецификой программы является построение схемы в стандарте ANSI. Функционирование схемы, подробно описано в ГЛАВЕ 3.

Рис. 7.7. Принципиальная схема приемника циклового и сверхциклового синхронизма.

РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ КОММУТАЦИОННОГО ЭЛЕМЕНТА

Принципиальная схема КОММУТАЦИОННОГО ЭЛЕМЕНТА также строится на основе функциональной схемы, но в данном случае необходимо рассмотреть соединение ячеек памяти, входящих в состав двух ОЗУ (запоминающего устройства адреса и информационного запоминающего устройства).

В

запоминающем устройстве адреса, как следует из описания структурной схемы запись и считывание производятся словами по 6 бит, следовательно, необходимо объединить входы и выходы ячеек, расположенных в одной строке, а адресные входы необходимо объединить у ячеек, расположенных в одном столбце (см. рис. 7.8).

Рис. 7.8. Принципиальная схема запоминающего устройства адреса.

В

информационном запоминающем устройстве запись производится побитно, а считывание словарно (по 8 бит), для этого необходимо объединить входы всех ячеек, а выходы ячеек объединить по строкам, при этом необходимо к каждому адресному входу подключит элемент И, который и позволит выбрать именно ту ячейку памяти, которую и необходимо (см. рис. 7.9). При таком построении запоминающего устройства адрес строки и адрес столбца должны задаваться для каждой ячейки отдельно.

Рис. 7.9. Принципиальная схема запоминающего устройства коммутации.

Дальнейшая разработка принципиальной схемы КОММУТАЦИОННОГО ЭЛЕМЕНТА сводится к подстановке разработанных библиотечных элементов в соответствии с функциональной схемой данного блока. Запоминающие устройства на принципиальной схеме блока представлены в виде отдельных элементов. Разработка принципиальной схемы велась при помощи программы схемотехнического моделирования, и все элементы данного устройства представлены в стандарте ANSI. Принципиальная схема коммутационного элемента представлена на рисунке 7.10.

Функционирование данной схемы описано в ГЛАВЕ 7, но необходимо отметить, что в запоминающем устройстве коммутации при записи и считывании информация представляется в разной форме (при записи побитно, а при считывании словарно) и поэтому дешифратор строк при считывании информации необходимо отключить.

Рис. 7.10. Принципиальная схема коммутационного элемента.

ПРИНЦИПИАЛЬНАЯ СХЕМА БЛОКА ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ

Р

азработка принципиальной схемы БЛОКА ФОРМИРОВАНИЯ ИСХОДЯЩИХ КАНАЛОВ, не отличается от разработки предыдущих принципиальных схем. Рассмотрим принцип работы запоминающего устройства. При записи запоминающее устройство воспринимает информацию словарно по 8 бит, и записывает ее в соответствующий столбец (для этого необходимо объединить входы элементов входящих в одну строку), а считывание информации происходит из соответствующей строки (для этого необходимо объединить элементы, входящие в один столбец) (см. рис. 7.11)

Рис. 7.11. Принципиальная схема запоминающего устройства.

Д

ля построения принципиальной схемы всего блока, также была использована программа схемотехнического работающая в стандарте ANSI. Принципиальная схема блока представлена на рисунке 7.12.

Рис. 7.12. Принципиальная схема блока формирования исходящих каналов.

Функционирование данного блока более подробно описано в ГЛАВЕ 3.

ГЛАВА 7

КОНСТРУКТИВНЫЕ ОСОБЕННОСТИ ПРОЕКТИРУЕМОГО УСТРОЙСТВАВВЕДЕНИЕ

В настоящее время существует несколько стандартных технологий производства кристалла с линиями рисунка от 0,25 до 3,0 мкм. Но в связи с тем, что в нашей стране технологии 0,25 и 0,35 мкм еще не отработаны, то приходится разрабатывать устройства с учетом имеющихся технологий, т.е. приходится прибегать к схемотехническим изощрениям для получения конкурентоспособной интегральной схемы. В результате была выбрана технология изготовления кристалла с минимальной шириной рисунка 1,2 мкм, как наиболее отработанная и наиболее экономически выгодная. При появлении в нашей стране более современных технологий на одном кристалле при тех же размерах можно будет разместить коммутатор на большее количество каналов.

8.1.1 ОСНОВНЫЕ ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ КРИСТАЛЛА

Рассмотрим основные характеристики проектируемой БИС, в основном, определяемые технологией производства:

Напряжение питания - 5 В;

Ток потребления - не более 1 мА;

Диапазон рабочих температур - от -20 до +60 0С;

Технология производства - стандартная, 1,2 мкм;

Предполагаемый тип корпуса - 2123.40-1, стандартный, с количеством выводов – 40.

НАЗНАЧЕНИЕ ВЫДОВ МИКРОСХЕМЫ

Таблица 8.1

Предварительно принятое назначение выводов микросхемы

| Выводы | Назначение |

| 1 - 8 9 - 16 17,18 - 22 - 26 - 30 31 32 33 34 35 | Групповые входы Групповые выходы Питание и «земля» Шина обмена информацией между кристаллами по горизонтали Шина обмена информацией между кристаллами по вертикали Адресные выводы кристалла Ввод команды Вывод результатов Выбор кристалла Ввод тактовой частоты Ввод синхроимпульсов |

ЭЛЕМЕНТЫ ТОПОЛОГИИ

КОНСТРУКТИВНО - ТЕХНОЛОГИЧЕСКИЕ ОГРАНИЧЕНИЯ

В данном разделе приведены основные конструкторско-технологические ограничения на проектирование микросхемы, определяемые заводом изготовителем в соответствии с применяемой технологией.

Конструкторско-технологические ограничения предназначены для проектирования топологии цифровых КМДП БИС по технологии, предусматривающей использование «карманов» п-типа проводимости, изоляцию элементов посредством заглубленных в объем монокристаллического кремния, легированного фосфором, самосовмещенных транзисторных структур и двухуровневой разводки, сформированной на основе сплавов алюминия.

Перечень и последовательность слоев фотолитографии, существенных при проектировании БИС, приведены в таблице 8.2.

Минимальная ширина топологического рисунка - 1,2 мкм. Остальные минимально-допустимые размеры элементов топологии, существенные для проектирования блоков БИС, приведены в таблице 8.3.

Транзисторные структуры, выполненные по данной технологии характеризуются следующими физико-технологическими параметрами:

Эффективная длинна канала транзистора - 1,0 мкм;

Удельная емкость затвора - 800 пф/мм;

Подвижность электронов в канале - 400 см/В с;

Подвижность дырок в канале - 200 см/В с;

Пороговое напряжение

п-канальных транзисторов - 0,5 … 1,5 В;

р-канальных транзисторов - 0,8 … 2,0 В.

Таблица 8.2

Перечень слоев фотолитографии

| Номер слоя | Наименование слоя |

| 1 2 3 4 5 6 7 8 9 10 | Карман п-типа Диффузионные области р-охраны Активные области транзисторов (тонкий окисел) Затворы из поликристаллического кремния, легированного фосфором Диффузионные области истока-стока р-канальных транзисторов Диффузионные области истока-стока п-канальных транзисторов Первые контактные окна в диэлектрическом слое Алюминиевая металлизация первого уровня Вторые контактные окна в диэлектрическом слое Алюминиевая металлизация второго уровня |

Таблица 8.2.

Минимально-допустимые размеры элементов топологии

| № пп | Наименование элемента топологии | Размер, мкм |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 | Перекрытие области тонкого окисла областью кармана п-типа Перекрытие области охраны р-типа областью тонкого окисла Расстояние между границей области кармана и границей области охраны р-типа Ширина области локального окисла внутри области кармана п-типа Расстояние от границы тонкого окисла до контактной площадки из поликристаллического кремния Расстояние между двумя соседними областями из поликристаллического кремния Ширина затворов из поликристаллического кремния Размер стороны контактной площадки из поликристаллического кремния Ширина шин из поликристаллического кремния вне области канала Расстояние между областью охраны р-типа и областями исток-сток п-канальных транзисторов Расстояние между областями исток-сток р-канальных транзисторов и карманом п-типа Размер стороны контактного окна Расстояние от края контактного окна до края контактной площадки Ширина шин алюминия первого уровня металлизации Ширина шин алюминия второго уровня металлизации Расстояние между двумя шинами алюминия в одном уровне металлизации Расстояние от линии рельефа до края контактного окна Расстояние от края контактного окна к диффузионной области истока-стока до поликристаллического затвора Перекрытие локального окисла поликремневым затвором п- и р-канальных транзисторов. | 0,5 1,0 4,0 2,0 0,5 1,2 1,2 4,0 2,0 2,0 1,2 1,0 1,2 3,0 4,0 1,2 0,5 1,0 1,2 |

Похожие работы

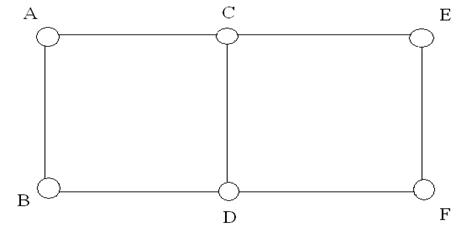

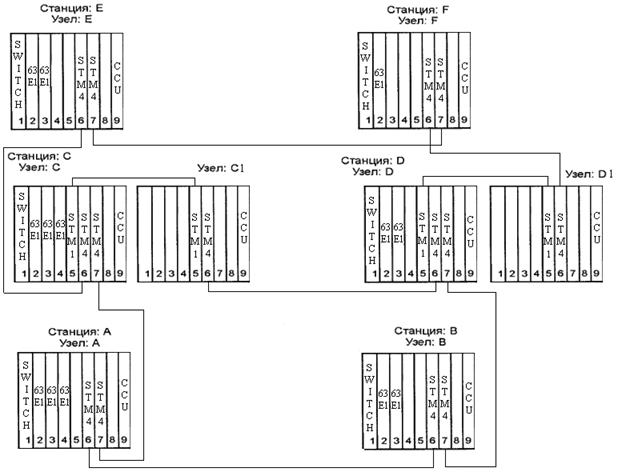

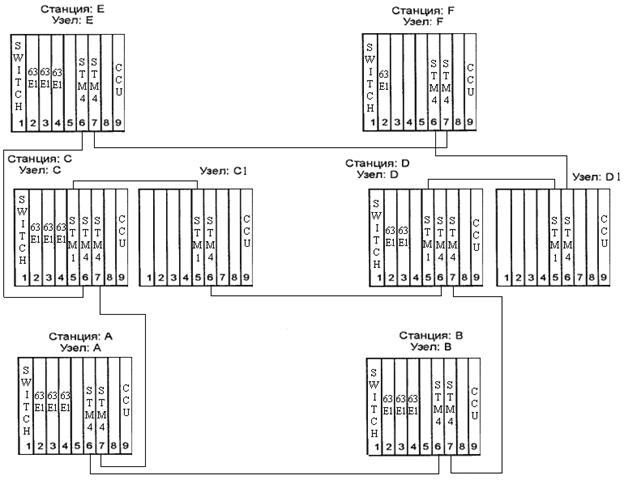

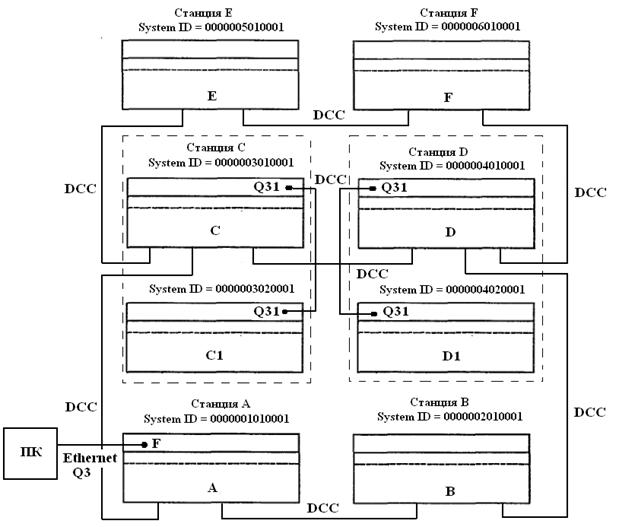

... эксплуатации (станционный сервер). Подключение выполняется посредством соединения через COM-порт или через соединение локальной сети Ethermet 100 Мбит/с. Связь сервера с терминалами центра управления осуществляется посредством локальной сети. 6. Цифровые системы уплотнения аналоговых линий Задача таких систем заключается в экономии физических линий связи, когда на одну пару телефонной линии ...

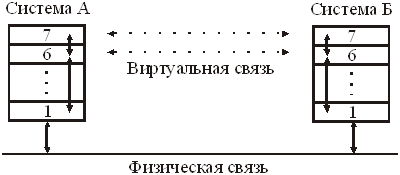

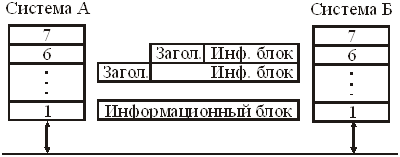

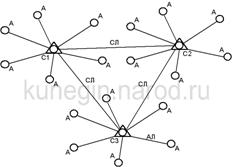

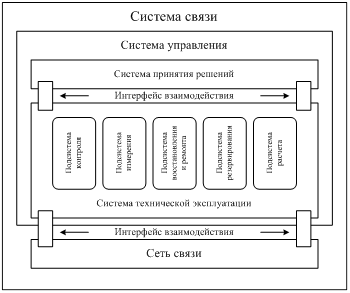

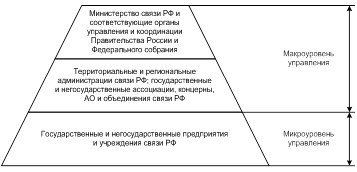

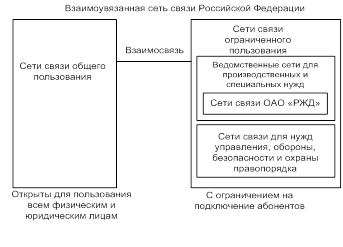

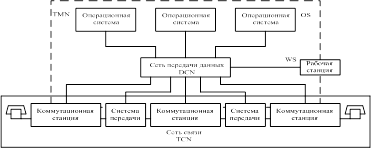

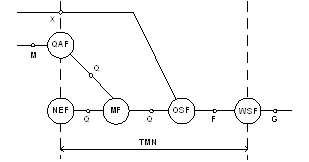

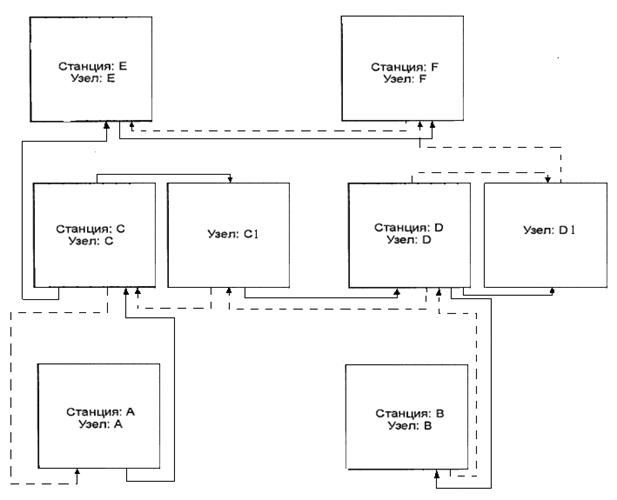

... Каждому элементу соответствует численный и символьный идентификатор. В имя переменной включается полный путь до нее от корневого элемента root. 3. Система мониторинга и администрирования 3.1 Системы управления технологическим сегментом магистральной цифровой сети связи ОАО «РЖД» РФ При построении современных цифровых сетей следует различать следующие сетевые уровни: уровень первичной ...

... ПО. Центральное ПО может взаимодействовать с другими функциональными блоками в центральном процессоре. Взаимодействие функциональных блоков всегда происходит на уровне CP. 3 Виды доступа В коммутационной системе AXE-10 используется различное оборудование доступа, которое позволяет строить сети с достаточной гибкостью. К этому оборудованию относится следующее: - Удаленный абонентский ...

... нм; - STM-4 L-4.2 - модуль оптического приемопередатчика организует один оптический интерфейс STM-4 (или STM-4c), связанный с модулем кроссовой коммутации, работает на длине волны 1550 нм; - STM-16 - модуль оптического компонентного интерфейса; - Gigabit Ethernet - модуль позволяет организовать передачу данных в формате Gigabit Ethernet с сетевой топологией «точка-точка»; - 63 Е1 - плата ...

0 комментариев