Навигация

Выбор программных средств

4.2. Выбор программных средств.

В настоящее время существует большой выбор различных программных средств. При этом каждое из них имеет свою область применения. Например, для написания системных драйверов используются языки программирования низкого уровня (Assembler, Forth), так как работа таких программ идет в реальном времени, и для своевременной обработки данных требуется большое быстродействие драйвера-программы. Для написания удобных интерфейсов программ, а также программ, связанных с ведением баз данных, где не требуется столь высокого быстродействия, используются языки программирования высокого уровня (Clipper, Pascal, FoxPro, C++, Visual Basic). Т.е. выбор тех или иных программных средств реализации зависит конкретно от поставленной задачи и возлагаются на программиста, решающего эту задачу.

При проектировании данного устройства, для написания подпрограмм обмена информацией между проектируемым устройством и компьютером было решено использовать Assembler (процессора 80286), поскольку он обеспечивает максимальное быстродействие, минимальный объем, а также простоту и удобство в написании подпрограмм подобного класса.

При этом сохраняется возможность использования для этой цели морально устаревших в настоящее время компьютеров на базе процессоров 80286 и 80386, имеющихся в достаточном количестве на предприятиях, работающих в операционной системе MS-DOS. Также (при использовании соответствующих микропроцессоров и программных средств) этим обеспечивается максимальная транспортабельность программы при создании интерфейсов под другие операционные системы (OS/2, Windows 95, Windows NT, Unix и пр.).

Ассемблер представляет собой язык программирования низкого уровня, в котором программист пишет инструкции, управляющие работой процессора. При помощи программы-компилятора эти инструкции переводятся в машинный код, исполняемый непосредственно процессором. В число команд Ассемблера входит самый минимальный набор (команды перехода, вызова подпрограмм и возврата из них, работы с регистрами, памятью, арифметические операции, логические операции, операции сдвига, сравнения, работы с портами ввода/вывода).

Для написания интерфейса программы поддержки данного устройства возможно использование любого из языков программирования высокого уровня, позволяющего вставлять подпрограммы на Ассемблере в текст программы. Поскольку данный вопрос выходит за рамки настоящей работы, подробно он рассматриваться не будет [8,9].

5. Описание принципиальных схем.

5.1. Описание состава принципиальных схем в сопоставлении с соответствующими структурными схемами узлов.

После выяснения структуры устройства и выбора элементной базы можно приступать к проектированию принципиальной схемы.

1) Входные регистры (см. структурную схему на рис.2).

Данный узел представляет собой 32-разрядный запоминающий регистр с ТТЛ-уровнями, без Z-состояния, использующий 8 входных линий данных и несколько линий управления на 32 выходных линии. Принципиальная схема узла изображена на рис.9.

Работает следующим образом: на контакты 2-9 разъема LPT-порт подаются 8 бит данных. На один из контактов 1-4 разъема X1 (с дешифратора) подается логический “0” - выбор регистра, в который должна быть произведена запись. Перепадом логических уровней “0”Þ”1” на контакте 16 разъема LPT-порт происходит защелкивание данных в выбранном регистре. Запись данных в остальные регистры производится аналогичным образом.

Питание узла: микросхемы DD2-DD5: 10 вывод - GND, 20 вывод - +5в.

Максимально потребляемый ток I1+5впотр.= 28мА*4 = 112мА

Рис.9. Входные регистры (принципиальная схема).

2) Устройство согласования по входу (см. структурную схему на рис.2).

Данный узел обеспечивает согласование между ТТЛ-выходами регистров и входами испытуемой микросхемы как по напряжению (приведение уровней ТТЛ Þ КМОП или ТТЛ), так и по току. Принципиальная схема узла изображена на рис.10.

Исходя из приложения [3] максимальные входные токи для микросхем ТТЛ логики равны: ток “0” - 2мА, ток “1” - 0.1 мА.

Напряжение +Umc - напряжение питания испытуемой микросхемы. Для ТТЛ микросхем оно равно +5в. Для КМОП микросхем - +9в. При помощи него формируется входной ток “1”.

Напряжение -Umc зависит от выбранного типа микросхемы (задается пользователем, выставляется при помощи одного бита управляющего регистра). Для ТТЛ микросхем оно равно -9.3в. Для КМОП микросхем - -1в.

Расчет резисторов R33 и R65 в цепях стоков транзисторов VT1 и VT33 соответственно:

а) Для ТТЛ типа (считаем падение напряжения на открытых полевых транзисторах близким к 0):

R33 = (|+Umc|-2.4в)/I1вх.макс.ТТЛ = 2.6в/0.1мА = 26К » 27К

R65 = (|-Umc|-Uпад.VD2)/I0вх.макс.ТТЛ = 9.3в-1.1в/2мА » 4.3К

б) Для КМОП логики соответственно:

I1вх.макс.КМОП = (|+Umc|-7в)/R33 = 9в-7в/27К » 0.07 мА

I0вх.макс.КМОП = (|-Umc|-Uпад.VD2)/R65 = 0.3в/4.3К » 0.07 мА

Диоды VD1 и VD2 нужны для ограничения потенциала U0вх. (т.е. этот потенциал не должен быть ниже потенциала общего провода, поскольку при этом возможен выход из строя микросхем КМОП логики). Значения 2.4в и 7в в формулах - это минимальные уровни логической “1” для ТТЛ и КМОП микросхем соответственно [3].

Данный узел инвертирует значение входного сигнала. Разъем X3 является панелью для вставки испытуемой микросхемы.

Узел работает следующим образом:

При подаче на вход логической “1”, напряжение на затворе транзистора VT1 будет близко к +5в, вследствие чего он находится в закрытом состоянии. Канал исток-сток этого транзистора имеет большое сопротивление, и ток через него не течет (не учитывая очень малые токи утечки). В то же время транзистор VT33 открыт, т.к. напряжение между подложкой и затвором равно около +5в. Через него, резистор R65 и диод VD2 течет ток, равный » 2мА. При подключении входа испытуемой микросхемы к аноду диода VD1, часть этого тока пойдет через него, обеспечивая уровень логического “0” на входе микросхемы. Диод VD1 нужен для компенсации падения напряжения на VD2, чтобы не допустить на входе микросхемы уровня напряжения ниже уровня общего провода (что является причиной выхода из строя КМОП микросхем).

При подаче на вход уровня логического “0” наоборот, транзистор VT33 будет закрыт, транзистор VT1 - открыт. Ток потечет через переход исток-сток транзистора VT1, резистор R33 и вход испытуемой микросхемы. Максимальный входной ток для ТТЛ микросхем будет примерно U1вх;макс.=(|+Uмс| - 2.4в)/R33 » 0.1мА.

Питание узла: +Uмс, -Uмс, +5в.

Максимально потребляемые токи (+Uмс.макс.=+9в, -Uмс.макс.=-10в):

I2+Uмспотр.= (+Uмс.макс./R33)*32 = (9в/27000)*32 » 11мА

I2-Uмспотр.= (|-Uмс.макс.+UVD2|/R65)*32 = (9.3в/4300)*32 » 69мА

I2+5впотр.= Iзатв.VT1*32 » 0мА (Iзатв.VT1 имеет малую величину, порядка нескольких микроампер, поэтому в расчет не принимается)

Рис.10. Устройство согласования по входу (принципиальная схема).

3) Устройство согласования по выходу (см. структурную схему на рис.2).

Узел служит для согласования ТТЛ или КМОП уровней, считываемых с испытуемой микросхемы, в ТТЛ-уровни, для подачи на выходные мультиплексоры. Представляет собой простейшую схему включения NPN-транзистора с ОЭ. Инвертирует входной сигнал. Схема изображена на рис.11. Работает следующим образом:

При подаче на вход логической “1” в цепи базы течет ток, равный Iб=(|+Uмс|-Uбэ)/R97. Iб»0.043мА для ТТЛ и Iб»0.083мА для КМОП микросхем. Ток в цепи коллектора Iк=(5в-Uбэ)/R129 » 0.43мА. Потенциал на коллекторе транзистора равен ~0.7в, что на входе мультиплексора будет воспринято как уровень логического “0” (поскольку для серии К555 напряжение U0вх.макс.=0.8в).

При подаче же на вход логического “0”, транзистор будет закрыт. Напряжение на коллекторе будет близко к +5в. Ток потечет через R129 и вход мультиплексора.

Питание узла: +5в.

Максимально потребляемый ток: I3+5впотр.= ((+5в-Uкэ VT65)/R129)*32 = (4.3в/10000)*32 » 14мА

Рис.11. Устройство согласования по выходу (принципиальная схема).

4) Выходные мультиплексоры (см. структурную схему на рис.2).

Узел представляет собой мультиплексор-преобразователь для передачи данных с 32-х входных линий на 4 выходных линии. Уровни сигналов - ТТЛ. Принципиальная схема изображена на рис.12, в схеме используется параллельное включение выходов и раздельное управление выборкой мультиплексоров.

Узел работает следующим образом: на один из выводов 1-4 разъема X1 для выборки нужного мультиплексора подается уровень логического “0”. При помощи вывода 2 разъема LPT-порт подачей “0” или “1” производится выбор входов мультиплексора. На выходах мультиплексора появляются данные с соответствующих входов. Эти данные могут быть считаны с выводов 10-13 разъема LPT-порт. Далее 2 считанных ниббла (по 4 бита) программно собираются в 1 байт (8 бит).

Питание узла: +5в (микросхемы DD13-DD16).

Максимально потребляемый ток: I4+5впотр.= 19мА*4 = 72мА

Рис.12. Выходные мультиплексоры (принципиальная схема).

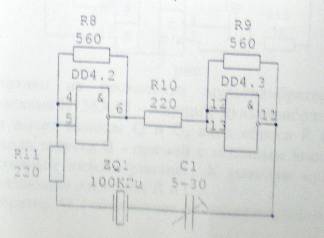

5) Управляющее устройство (см. структурную схему на рис.2).

Узел служит для выборки необходимых регистров и мультиплексоров при записи данных в регистры и считывании данных из мультиплексоров. Является дешифратором адреса 3x8. Схема изображена на рис.13.

Узел работает следующим образом: при подаче на выводы 1,14,16 разъема LPT-порт двоичного кода, на соответствующем выводе разъема X1 появляется уровень логического “0”. При этом производится выборка соответствующего регистра или мультиплексора.

Питание узла: +5в (DD1, 8 вывод - GND, 16 вывод - +5в).

Максимально потребляемый ток I5+5впотр.= 10мА

Рис.13. Управляющее устройство (принципиальная схема).

6) Блок питания (см. структурные схемы на рис.2, 3).

Принципиальная схема узла (без устройства коммутации и источника питания устройства) изображена на рис.14. Узел обеспечивает цифровую регулировку напряжения питания испытуемой микросхемы, цифровое управление ограничением потребляемого тока с малым шагом (благодаря чему возможно его измерение с достаточной точностью), защиту от к/з в цепи нагрузки.

Узел работает следующим образом:

а) Регулировка напряжения.

В регистр DD7 программно записываются 8 бит значения напряжения (числовые значения лежат в диапазоне от 0 (0H) до 255 (0FFH)). С выхода этого регистра 8 бит поступают на умножающий ЦАП (DA3), где преобразуются в аналоговое напряжение. Выбранный ЦАП имеет разрядность 10 бит. Его младшие 2 бита не используются (заземлены). Их использование в данном случае нецелесообразно, так как это потребовало бы введения дополнительных разрядов у запоминающего регистра, что сделало бы точность установки напряжения питания избыточной и усложнило устройство. С точки зрения программирования и размещения данных также намного удобнее и эффективнее работать с 8-битными величинами, нежели с 10-битными.

Опорное напряжение для DA3 поступает с VD65 и равно +9в. Резистор R161 выбран из расчета, что Uвх.»13в, Iстаб.»10мА, R161=(Uвх.-Uстаб.)/Iстаб.=(13-9)/10»390ом. Шаг регулировки в этом случае будет равен 9в/256»0.04в. Далее напряжение с аналогового выхода DA3 поступает на вход регулируемого стабилизатора напряжения DA1, включенного по типовой схеме с внешним транзистором VT98 [2]. С эмиттера этого транзистора снимается напряжение питания устройства согласования +Uмс, а через резистор R171 - напряжение +Uпит.мс., предназначенное для питания испытуемой микросхемы.

б) Регулировка потребляемого тока.

В регистр DD8 программно заносятся 8 бит значения ограничиваемого тока (0-255). Аналогично регулировке напряжения, для преобразования численного значения в напряжение используется ЦАП DA4. При опорном напряжении +9в, шаг регулировки напряжения на аналоговом выходе DA4 равен примерно 0.04в.

Как было сказано выше, в цепи питания испытуемой микросхемы стоит резистор R171. Он служит простейшим преобразователем ток-напряжение, т.к. напряжение на нем прямо пропорционально току, проходящему через данный резистор: UR171=Iпотр.*R171. Для развязки разности потенциалов, снимаемых с данного резистора применен дифференциальный усилитель на ОУ DA6, схема которого взята из [1]. При равенстве сопротивлений R163=R164 и R165=R166 Uвых.ОУ.=UR171(R165/R163)=Iпотр.*R171*R165/R163.

Для уменьшения погрешности измерений, R171 должен быть выбран как можно меньше, чтобы падение напряжения на нем было минимальным. Чувствительность можно поднять за счет увеличения усиления (соотношения R165/R163) дифференциального усилителя. Примем R171=0.1ом. Поскольку максимальный потребляемый ток Iпит.мс. выбран 256мА, то макс. падение напряжения на R171, соответствующее этой величине, будет 256мА*0.1ом=25.6 мВ. При напряжении питания в +9в погрешность составит 0.0256в/9в*100%=0.28%, что по величине меньше суммарной погрешности ЦАП. Напряжению 25.6мВ на входе дифференциального усилителя должно соответствовать напряжение +9в на его выходе, чтобы обеспечить сравнение сигналов, поступающих с ЦАП и с усилителя. Т.е. коэффициент усиления должен быть равен R165/R163=9в/0.0256в=351.5. Выбрав R163=1К, получим R165»360К.

Сигналы с выходов дифференциального усилителя DA6 и ЦАП DA4 поступают на вход компаратора DA5. На выходе компаратора появляется сигнал сравнения, который в свою очередь подается на вход S триггера DD12. Данный триггер обеспечивает хранение состояния включен/выключен для регулируемого стабилизатора напряжения DA1. Вход R триггера DD12 используется для сброса сработавшей аппаратной защиты по току. При инициализации устройства на контакте 1 разъема X5 выставляется уровень логической “1”, который поступает на базу транзистора VT98. Этот транзистор инвертирует входной сигнал и обеспечивает согласование уровней; сигнал с его коллектора (в нормальном режиме - логический “0”) поступает на вход R триггера DD12.

Если реально потребляемый ток меньше выставленного цифрового значения в регистре DD8 (положительный потенциал на прямом входе 3 компаратора ниже потенциала на его инверсном входе 4), то на выходе компаратора DA5 напряжение близко к 0в. Оно поступает на вход S триггера. Состояние триггера остается неизменным, на выходе Q DD12 и входе +Uвыкл. DA1 присутствует уровень логического “0”; на испытуемую микросхему подается напряжение питания.

Если же реально потребляемый ток превышает выставленное в регистре DD8 цифровое значение (соответственно потенциал на входе 3 DA5 выше потенциала на входе 4), то на выходе компаратора появляется напряжение около +12в, которое подается на вход S триггера DD12. На выходе Q триггера появляется напряжение логической “1” (+12в), которое, в свою очередь подается на вход +Uвыкл. DA1, и приводит к снятию напряжения питания с нагрузки. Теперь для включения стабилизатора напряжения питания необходимо программно осуществить перепад напряжения “1”Þ”0”Þ”1” на контакте 1 разъема X5, но при этом включение будет возможно только при условии, что реальная нагрузка ниже выставленной цифровой. В противном случае на выходе Q триггера DD12 останется уровень логической “1” (поскольку на входе S будет +12в с компаратора) и стабилизатор не будет включен.

Для контроля состояния выхода компаратора DA5 используется контакт 15 разъема LPT-порт. На него данный сигнал поступает через резистор R169 и стабилитрон VD67, служащие для его преобразования к ТТЛ уровню. Присутствие логической “1” на нем показывает, что потребляемый испытуемой микросхемой ток превышает программно выставленный.

Конденсаторы C1, С2 служат для сглаживания пульсаций в цепях формирования опорного напряжения, C4 - в цепи питания испытуемой микросхемы.

Питание узла: +5в (DD7, DD8, DA3, DA4), +Uвх. (из него формируется +Uмс, +Uпит.мс, питания микросхем DD12, DA5, DA6 и опорные напряжения для микросхем DA3, DA4).

Максимально потребляемые токи:

I6+5впотр.= Iпотр.DD7*2 + Iпотр.DA3*2 = 28мА*2 + 2мА*2 = 60 мА

I6+Uвх.потр.= IR161 + IR162 = (Uвх.-Uстаб.VD65)/R161 + (Uвх.-Uстаб.VD66)/R162 = (13в-9в)/390ом + (13в-11в)/270ом = 10+7 мА = 17мА

Рис.14. Блок питания (принципиальная схема).

6.1) Устройство коммутации питания (см. структурную схему на рис.4).

Данный узел обеспечивает коммутацию напряжения питания, подаваемого на выводы испытуемой микросхемы. При помощи него производится также переключение -Uмс ( -1в или -9.3в, для КМОП и ТТЛ логики соответственно, в зависимости от выбранного типа микросхемы) и включение регулируемого стабилизатора напряжения. Схема изображена на рис.15.

Работает следующим образом:

Аналогично записи во входные регистры, в регистр DD6 программно записывается 8-битное число. Путем анализа разновидностей питания ТТЛ и КМОП микросхем установлено, что необходимо коммутировать 6 выводов испытуемой микросхемы по “+” и 3 вывода по GND.

а) Коммутация “+” питания испытуемой микросхемы.

0-2 биты регистра DD6 отвечают за коммутацию “+” питания микросхемы. Эти сигналы с регистра поступают на дешифратор DD9, где шестнадцатеричное число (0-7H), преобразуется в двоичную форму. Результат появляется на выходах дешифратора в инверсном виде (на выбранном будет уровень логического “0”, на остальных выходах дешифратора - уровень логической “1”). Буферная микросхема DD11 (с ОК, без инверсии) служит для умощнения выходных сигналов дешифратора. Для примера, пусть логический “0” будет присутствовать на âûâîäå /0 дешифратора DD9. Через резистор R172 он поступит на базу транзистора VT99. Данный транзистор будет в открытом состоянии, и с его эмиттера через переход КЭ напряжение +Uпит.мс. поступит на соответствующий вывод микросхемы. На транзисторе при этом образуется падение напряжения Uкэ»0.7в. Остальные транзисторы будут закрыты, и влиять на работу практически не будут (исключая малый ток утечки, которым можно пренебречь).

Номинал резистора R172 выбран из следующих соображений:

Iкэ VT99 = 256мА. Кэ VT99 возьмем минимальным (равным 25). Тогда Iб VT99min » 10мА. Следовательно, взяв минимальное +Uпит.мс.= 5в, получим R172= (+Uпит.мс-Uкэ VT99)/Iб VT99min = 4.3в/0.01А » 430 ом.

Резистор R181 служит для поддержания транзистора VT99 в закрытом состоянии при отсутствии сигнала “0” на входе.

б) Коммутация GND.

3-5 биты регистра DD6 отвечают за коммутацию GND питания испытуемой микросхемы. Аналогично коммутации “+” питания микросхемы (Uпит.мс.), сигналы с соответствующих выводов регистра DD6 поступают на дешифратор DD10. На одном из его выходов появляется логический “0”. На остальных выходах остается уровень логической “1”. Этот “0” поступает на электронный ключ, собранный на 2-х транзисторах. Для примера, пусть логический “0” присутствует на выходе /0 дешифратора DD10. Тогда транзистор VT109 (необходимый для согласования по напряжению, а также умощнения выхода дешифратора) будет открыт, транзистор VT105 также будет открыт, и на коллекторе VT105 будет потенциал, равный уровню GND (поскольку напряжение -0.7в компенсируется падением напряжения Uкэ VT105). Остальные же транзисторы (на других выходах дешифратора) будут закрыты, и влиять на работу практически не будут (исключая очень малый ток утечки, которым можно пренебречь).

Резистор R178 рассчитан аналогично R172 из а) и равен 430 ом. Резистор R192 служит для поддержания транзистора VT105 в закрытом состоянии, в случае, когда закрыт транзистор VT107. Резистор R189 рассчитывается исходя из Кэ VT107=25, Iб VT105 = Iк VT107 » 10мА. Iб VT107 min = Iк VT107/ Кэ = 10мА/25 = 0.4мА

R189 = (+5в-Uкэ VT107)/Iб VT107 min = 4.3в/0.4мА » 10к

в) Коммутация -Uмс. Производится при помощи бита 6 регистра DD6. Сигнал с него через R187 поступает на базу транзистора VT108, служащего для согласования уровней напряжения. С коллектора транзистора VT108 сигнал через резистор R188 поступает на базу транзистора VT112, которым производится коммутация напряжения. В случае, если на выходе DD6 присутствует уровень логического “0”, то транзисторы VT108 и VT112 открыты, переход КЭ транзистора VT112 шунтирует стабилитрон VD68, и напряжение -Uмс=-10в+Uкэ.VT112= (-10+0.7)в = 9.3в.

Если же на выходе DD6 присутствует уровень логической “1”, то VT108 и VT112 закрыты, а напряжение -Uмс = (-10в+Uстаб.VD68) = (-10+9)в = 1в

г) Включение напряжения питания. Осуществляется при помощи 7 бита регистра DD6. Данный сигнал идет в схему блока питания, где и производится управление.

Питание узла: +5в (DD6, DD9-DD11), -10в (для формирования -Uмс.), -0.7в (для коммутации GND), +Uпит.мс. (для коммутации “+” питания).

Максимально потребляемые токи:

I7+5впотр.= Iпотр.DD6 + Iпотр.DD9*2 + Iпотр.DD11 + IR188 + IR178 = Iпотр.DD6 + Iпотр.DD9*2 + Iпотр.DD11 + (5в+10в-Uкэ.VT108-Uкэ.VT112)/R188 + (5в-Uкэ.VT109)/R178 = 28мА + 10мА*2 + 30мА + 13.6в./10к + 4.3в/430ом = 89мА

I7-10впотр.= IR188 = (5в+10в-Uкэ.VT108-Uкэ.VT112)/R188 = 1мА

I7-0.7впотр.= IR178 = (5в-Uкэ.VT109)/R178 = 10мА

I7+Uпит.мс.потр.= IR172 = (+Uпит.мс.макс.-Uкэ.VT99)/R172 = (9в-0.7в)/430ом = 7мА

Рис.15. Устройство коммутации питания (принципиальная схема).

6.2) Источник питания устройства.

Данный узел обеспечивает питание всех остальных узлов проектируемого устройства. Перед началом проектирования схемы необходимо выяснить максимально потребляемый ток по каждому из напряжений питания (I+5впотр., I-10впотр., I-0.7впотр., I+Uвхпотр.). Максимально потребляемый ток Iмс.потр.макс. = 256мА.

I+5впотр.= I1+5впотр.+ I2+5впотр.+ I3+5впотр.+ I4+5впотр.+ I5+5впотр.+ I6+5впотр.+ I7+5впотр.= 112мА+0мА+14мА+72мА+10мА+60мА+89мА = 357мА

I-10впотр.= I2-Uмспотр.+ I7-10впотр.= 69мА+1мА = 70мА

I-0.7впотр.= I7-0.7впотр.+ Iмс.потр.макс. = 10мА + 256мА = 266мА

I+Uвх.потр.= I2+Uмс.потр.+ I6+Uвх.потр.+ I7+Uпит.мс.потр.+ Iмс.потр.макс. = 11мА+17мА+7мА+256мА = 291мА

Таким образом, для нормального функционирования устройства необходимы следующие напряжения питания:

+5в(400мА), -10в(100мА), -0.7в(300мА), +13в(350мА).

Напряжения +13в и -10в могут быть выпрямленными, сглаженными, но нестабилизированными (т.к. в схеме блока питания из +13в далее получаются стабилизированные, а -10в служит лишь для обеспечения I0вх. на входах испытуемой микросхемы).

Потому необходим двуполярный источник питания с напряжениями +13в и -10в, из которых при помощи дополнительных стабилизаторов получаются напряжения +5в и -0.7в. При этом токи потребления по соответствующим напряжениям будут суммироваться. Т.е. от плеча +13в будет потребляться ток порядка 400+350=750мА, а от плеча -10в соответственно 100+300=400мА.

Для источника питания требуется трансформатор T1 с 2-мя вторичными обмотками, 2 диодных выпрямительных моста (VD69-VD76) и 2 сглаживающих конденсатора. Мощность трансформатора должна быть не менее 13в*0.75А+10в*0.4А=13.75Вт. Под эти требования подходит трансформатор ТПП-207-127/220-50.

Принципиальная схема узла изображена на рис.16,

В качестве стабилизатора +5в выбрана микросхема КР142ЕН5А по типовой схеме включения, в качестве стабилизатора -0.7в - регулируемая схема на двух транзисторах (VT113, VT114). Причем в связи со столь малым напряжением, стабилизация производится не относительно “земли” (что не удалось бы осуществить в связи с суммарным падением напряжения на переходах БЭ транзисторов порядка 1.4в), а относительно стабилизированного источника +5в.

Настройка данного узла заключается в подстройке точного значения напряжения -0.7в на выходе блока питания при помощи подстроечного резистора R198.

Рис.16. Источник питания устройства (принципиальная схема).

Похожие работы

... 5 0110 6 6 0111 7 7 1000 8 8 1001 9 9 1010 A A 1011 C B 1100 F C 1101 H D 1110 P E 1111 U F Большинство изготовителей сигнатурных анализаторов пользуются таким же кодированием индицируемых данных, что и фирма Hewlett-Packard. Такое понятие, как почти ...

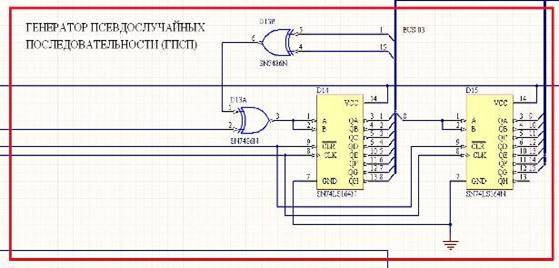

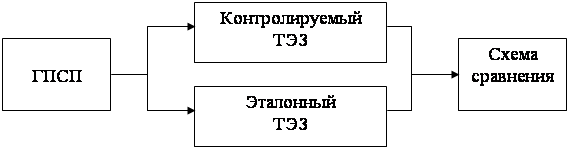

... (Свн =0)……………………….=< 65 нс Длительность импульса на выходе (Свн = 1000 пФ)………………………………. 2,76. 3,37 мкс Емкость нагрузки……………………………………………=< 200 пФ 9. Расчет параметров временной диаграммы функционирования стенда Автоматический стенд инициируется внешним сигналом «Пуск», Поступающим с пульта оператора. Этим сигналом ГПСП, СЧЦ и триггер разрешения работы (ТгРР) устанавливаются в ...

... ? 8. Какими программами можно воспользоваться для устранения проблем и ошибок, обнаруженных программой Sandra? Раздел 3. Автономная и комплексная проверка функционирования и диагностика СВТ, АПС и АПК Некоторые из достаточно интеллектуальных средств вычислительной техники, такие как принтеры, плоттеры, могут иметь режимы автономного тестировании. Так, автономный тест принтера запускается без ...

0 комментариев