Навигация

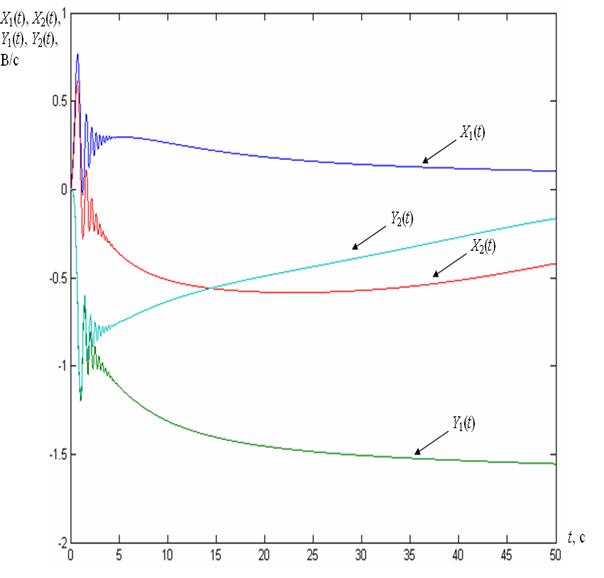

Оцінка верхньої граничної частоти фільтру

6.1 Оцінка верхньої граничної частоти фільтру

Оцінку проводимо з точки зору найнижчої швидкодії фільтру. В процесі виконання програми виконується:

підпрограма обробки переривань (ОР)

підпрограма множення (3 рази) (MULL88)

Кількість тактів, за які виконується програма, зведені в таблицю:

Таблиця 6.1

| Назва | Кількість тактів, необхідних для виконнаня програми | Число виконань даної програми за один цикл | Кількість тактів, за цикл виконання програми |

| Основна програма | 400 | 1 | 400 |

| MULL88 | 95 | 3 | 285 |

| OP | 108 | 1 | 108 |

Кількість тактів для виконання кожної команди взято з [6].

Формулювання теореми Котельникова:

будь-який сигнал, який має скінчений спектр, може бути без втрат перетворений у цифрову форму і потім відтворений за відліками цього дискретного сигналу при умові:

(6.1)

Для виконання програми необхідно всього тактів N=793. Для максимальної частоти f=2.5МГц для МП KР580ВМ80, частота видачі інформації fвид=2,5МГц/793=3152,6 Гц

За теоремою Котельникова, верхня гранична частота для фільтра складає

fверхнє = fвид /2=3152,6/2=1576,3 Гц (6.2)

7.

Опис фрагменту

принципової

схеми

реалізації

системного

контролера.

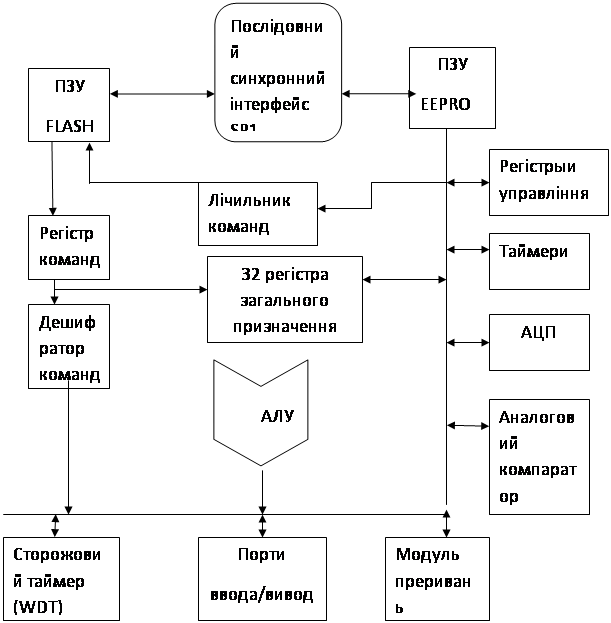

Системний контролер КР580ВВ28 виконує три функції:

фіксація слова стану процесора;

буферизація шини даних;

формування частини сигналів, які належать шині керування МПС (при звернені до ЗП – і , при звернені до пристроїв вводу/виводу - і , ).

Системний контролер складається з двонаправленої буферної схеми даних, регістра стану, і декодуючої схеми.

Восьмирозрядна паралельна тристабільна буферна схема даних приймає інформацію з канала даних МП по виводам D7 – D0 і передає в регістр стану інформацію стану, на системний канал даних по виводам DB7 – DB0 видає дані у циклі запису по сигналу . В циклі читання по сигналу заперечення буферна схема приймає дані з системного каналу по виводам DB7 – DB0 і передає по виводам D7 – D0 на канал даних мікропроцесору.

Регістр стану по вхідному сигналу фіксує інформацію стану МП в такті Т1 кожного машинного циклу МП.

Декодуюча схема формує один з вище перелічених сигналів керування. Асинхронний сигнал керує видачею даних з буферної схеми і керуючих сигналів з дешифратора: при наявності низького рівня на вході буферна схема передає дані і формує один з керуючих сигналів; при напрузі високого рівня всі виходи мікросхеми переходять у високоімпендансний стан. Напруга високого рівня на вході переводить виходи , , у пасивний стан (напругу високого рівня) і блокує передачу інформації через буферну схему даних.

Керуючі синали і формуються в циклі запису по сигналу .

При роботі з МП КР580ВМ80А системний контролер у циклі підтвердження запиту переривання формує три сигнали для прийому трьох байтів команди CALL від контролера переривань КР580ВН59 [7].

В невеликих

мікропроцесорних

системах вихід

мікросхеми

КР580ВК28 можна

під’єднати

до напруги +12В

через резистор

опору

1 кОм. Під

час дії сигнала

RC буферна

схема даних

мікросхеми

формує код

команди RST

7 і передає на

канал даних

МП. Таким чином,

мікромхема

забезпечує

єдиний вектор

переривань

з номером 7 без

додаткових

компонентів.

Основні параметри мікросхеми зведені у таблицю:

Таблиця 7.1 Параметри КР580ВК28

| Параметр | Значення |

| Вихідний струм високого рівня Вихідна напруга високого рівня на виходах D0-D7 Струм споживання Вхідна ємність Довжина сигналу Час встановлення сигналів , , відносно сигнала RC Час затримки інформації на виходах DB0-DB7 Час збереження інформації на виходах DB0-DB7 Час встановлення інформації на виходах DB0-DB7 Час встановлення вхідної інформації на виходах D0-D7 відносно RC в режимі читання | -10мкА 3,6В 140мА 12пФ 22нс 40нс 30нс 20нс 30нс 45нс |

Структурна схема системного контролера зображена на рис. 7.1.

Рис.7.1 Структурна схема системного контролера КР580ВВ28

Рис. 7.2 Схема підкдючення КР580ВВ28 до МП КР580ВМ80А

Опис виводів мікросхеми:

Таблиця 7.2

| Вивід | Позначення | Тип виводу | Функціональне призначення |

| 1 2 3 4 5, 7, 9, 11, 13, 16, 18, 20 6, 8, 10, 12, 15, 17, 19, 21 14 22 23 24 25 26 27 28 | RC DB4, DB7, DB3, DB2, DB0, DB1, DB5, DB6 D4, D7, D3, D2, D0, D1, D5, D6 GND Ucc | вхід вхід вхід вхід вихід/ вхід вхід/ вихід — вхід вихід вихід вихід вихід вихід вхід | Стробуючий сигнал стану Підтвердження захвату Видача інформації Прийом інформації Канал даних системи Канал даних мікропроцесора Загальний Управління передачею даних і видачею сигналів Підтвердження запиту переривання Читання з ЗП Читання з ПВВ Запис в ЗП Запис в ПВВ Напруга живлення +5В |

висновок

Отже, цифрові фільтри мають ряд переваг над аналоговими:

1) нечуттєвість характеристик фільтра до розкидування параметрів елементів, що у нього входять, їх часових та температурних дрейфів;

2) малі розміри і висока надійність фільтрів, пов’язані з використанням ВІС;

3) легкість зміни параметрів і характеристик цифрового фільтру через модифікацію програми і коефіцієнтів;

4) можливість реалізації фільтрів із змінними в процесі роботи параметрами.

Рівняння даного цифрового фільтру є дуже просте як для розв’язку, так і для реалізації. Проте, як видно з приведеної оцінки верхньої граничної частоти фільтру, вона не є достатньо високою. На неї впливає, по-перше, низька тактова частота МП КР580ВМ80, а, по-друге, велика кількість рядків програми. Це частково пояснюється відсутністю операції множення в МП КР580ВМ80.

Крім того, недоліком ЦФ є те, що кінцевий час перетворення сигналу за допомогою АЦП і ЦАП і особливо час, який необхідний для програми обчислення , обмежують знизу період між сусідніми замірами вхідного сигналу і значеннями вихідного. Це в свою чергу обмежує верхню граничну частоту сигналу , фільтрація якого може бути проведена.

Так як задана розрядність (8) дорівнює розрядності МП КР580ВМ80, то це не створює ніяких ускладнень для розв’язку поставленого завдання.

Список літератури

Алексенко А. Г., Галицин А. А., Иванников А. Д. Проектирование радиоелектронной апаратуры на микропроцессорах: програмирование, типовые решения, методы отладки. М.; Радио и связь, 1984.

Майоров В. Г., Гаврилов А. И. Практический курс программирования микропроцессорных систем. М.; Машиностроение, 1989.

Корячко В. П. Микропроцессоры и микроЭВМ в радиоэлектронных средствах; Учеб. Для вузов по спец. ‘Конструирование и технология радиоэлектронных средств.’ М.; Внеш. Шк, 1990.

Федорков Б. Г., Телец В. А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. М; Енергоатомиздат, 1990.

Коффон Д. Технические средства микропроцессорных систем; Практический курс. Пер. с англ. М.; Мир, 1983.

Програмное обеспечение микропроцессорных систем. Справочник С.Д. Погорелый, Т.Ф.Слободянюк, Києв, “Техника”, 1989.

Полупроводниковые БИС запоминающих устройств; Справочник В. В. Баранов, Н. И. Бекин, А. Ю. Гордунов и др.: Под ред. А. Ю. Гордонова и Ю. Н. Дьякова. М.; Радио и связь, 1987.

Проектирование микропроцессорной электронно-вычислительной аппаратуры: справочник В. Г. Артюхов, А. А. Будняк, В. Ю. Лапий и др. К.; Техника, 1988.

Г. Деч Руководство по практическому применению преобразований Лапласа, М. 1964.

додатки

MVI A ,91H - вивід в С4 одиниці

OUT FBH - вивід в С4 одиниці

MVI А, 8H вивід в C4 нуля

OUT FBH вивід в C4 нуля

Після цього АЦП приступив до перетворення вхідного сигналу в цифровий код. По закінченні

перетворення МП переходить до програми обробки перетворешія. в якій послідовно вводиться 2 байти Хn;

IN F8H ;ввід з каналу А

STA XNL ;вивід по адресі XNL - молодшого байту Хn

IN FAH ;ввід з каналу С

ANI 03Н

STA XNH ; вивід по адресі XNH - адреси старшою байту Хn

операція виводу виглядає простіше:

LDA YN1 ; ввід в акумулятор 8-розрядів Yn з комірки YN1

OUT F9H ; вивід в канал В;

LDA YN2 ; ввід в акумулятор 2-х молодших розірядів YN3,YN2

;(iншi занулені крім С4) OUT FBH

Передача (двох) 2-х молодших розрядів Yn, окремо зумовлена тим, щоб була найменша похибка у вихідному сигналі оскильки AЦП виводить інформацію швидко. Передача 2-х. старших розрядів Yn окремо викликала б (значну похи6ку) стрибок вихідною сигналу.

6.Програма цифрової обробки інформації.

Як видно зі схеми алгоритми функціонування NМП-пристрою, програма цифрової оброб-ки iнформації повинна неодноразово виконувати такі операції як :

1) множення 2-байтвох чисел на однобайтові;

2) додавання 2-х байтових чисел.

Для цього можна використати готові програми [2] ПП множення цилих чисел без •знаку 16*8:

| D | E | |

| * | ||

| A | ||

| A | H | I |

| DMULT: NXBIT: NOADD: | LXI Н, 0H MVI С, 08Н DAD H RAL JNC NOADD DAD D AСІ 0 DCR С JNZ NXBIT RET |

ПП додавання двобайтових чисел:

| B | С | |

| + | ||

| адрHL+1 | адрHL | |

| адрHL+1 | адрHL | |

| PLUS: | MOV A, C ADD M MOV M, A MOV А, В INX H ADC M MOV M, A DCX H RET |

Виходячи, що з умови завдання вхідний сигнал - двополярний. то потрібно організувати операцію множення 2-го числа на однобайтове зі знаком. Оскільки вхідний сигнал представле-ний як 10-ти розрядний зі знаком, а є можливість використати ПП множення DMULT чисел 16*8 біт знаку, то при множенні будемо подавати як ціле додатнє число, за модулем рівне. В па-м'яті будемо зберігати в такому форматі:

| байт XNH | байт XNL | |||||||||||||||||||

| D15 | D8 | D7 | D0 | |||||||||||||||||

| 0 | 0 | 1 | 0 | 0 | 0 | . | . | . | . | . | . | . | . | . | ||||||

модуль Xn

| (адр.XNH=адр.XNH1) |

З АЦП Xn подається у такому вигляді:

111…11 +Umax

100…00 0

000…00 -Umax

Для приведення цього формату потрібно:

1) коли X9=0 то проінвестувати розряди X0X9; D15=1

2) коли X9=1 то D15=0; X9=0

Користуючись алгоритмом програми обробки переривання і вищесказаним, програма обробки переривання на мові асемблеру буде:

| OP: M1: M2: | PUSH H PUSH PSW LHLD XNL SHLD XNLP IN F8H MOV L, A IN FAH ANI 03H MOV H, A ANI 02H JZ M1 MOV A, H ANI 010 MOV H, A JMP M2 MOV A, L CMA MOV L, A MOV A, H CMA MOV H, A SHLD XNI MVI A, 9H OUT FBH POP PSW POP H EI RET | Занесення колишнього значення Xn в комірку пам’яті для Xn-1 Ввід в програму розрядів X0X7 Ввід з каналу C розрядів Визначення умови: Корекція старшого байту Корекція від’ємного Xn до прийнятого формулою Xn Запис Xn у комірку пам’яті XNI і XNH Вивід у канал C розряд C4=1 для гашення результату Дозвіл переривання |

Основна програма повинна функціонувати по алгоритму, наведеному вище. Виникає тільки проблема узгодження інформації (кодів) представлення чисел з АЦП в пам'яті для виводу на АЦП (а вони всі різні). Для представлення Yn в пам'яті, виберемо той же формат, що і для Хn (так само і Хn-1). Коефіцієнти а0, а1, b1 в пам'яті зберігаються у вигляді модуля.

Основна програма враховує, шо а1, є від'ємний. В основній програми будуть використані ще дві програми:

1) ПП переводу 2-х байтового числа в доповнений код (для спрощення операції додавання)

| DOP: | MOV A, H СМA MOV H, А MOV A, І СМА MOV L, A INX H RET |

2) ПП множення чисел зi знаком, яка використовує ПП DMULT (множення чисел без знака)

| MN ML MM | MOV C, A MOV A, H JP ML MVI B, 1H ANI 7FH MOV H, A JMP MM MVI B, 0H XCHG MM MOV A, C CALL DMULT MOV L, H MOV H, A MOV A, B RET | Множник з регістру А заноситься в Чи виконується умова, що множене B=1 означає що множене (в HL) є від’ємне Корекція множеного до модуля Числа B=0 означає, що множене (в HL) є додатнє Обмін DE HL Занесення в регістр А множника з регістру С Множення чисел без знаку (16*8) Корекція результату (добутку) Ознака знаку множеного в А=1 – від’ємне |

Основна програма починається з ініціалізації мікросхеми K580ВВ55 для обміну з ЦАП і АЦП, після тогоАЦП встановлюється (після гасіння) в режим іперетворення вхідного сигналу. Далі іде циклічний підрахунок і виведення результату.

Основна програма.

| M00 M0 M3 M4 M5 | MVI A, 91H OUT FBH MVI A, 9H OUT FBH Mvi A, 8H OUT FBH LHLD XNPL LDA Al CALL MN JNZ M3 CALL DOP SHLD AXNP LHLD YNPL LDA B1 CALL MN JZ M4 CALL DOP SHLD BYNP LHLD XNL LDA A0 CALL MN JZ M5 CALL DOP MOV B, H MOV C, L I.XI H, AXNP CALL PLUS LDA BYNP MOV C, A LDA BYNP + 1 MOV B, A CALL PLUS LHLD AXNP MOV A, H ANI 7FH CMA MOV H, A MOV A, L CMA MOV L, A | ініціалзація ВВ355 запуск АЦП занесення в HL значення Xn-1 в комірку пам’яті занесення в аккумулятор байту а1 з пост. комірки множення а1 * Xn-1 перевірка чи Xn-1 був від’ємним перетворення а1 * Xn-1 в доповнюючий код запис добутку а1 * Xn-1 в пам’ять для зберігання занесення в HL значення Yn-1 в пам’ять занесення в регістр А байту число b1 з пам’яті множення b1*Yn-1 перевірка чи Yn-1 було додатнє перетворення b1*Yn-1 в доповнюючий код запис добутку b1*Yn-1 в пам’ять для зберігання запис в HL значення Xn з комірки пам’яті запис в аккумулятор байт коеф. множення а0*Xn перевірка чи Xn був додатній перетворення в доповнюючий код значення добутку а0*Xn в доповнюючому занесення в HL, добутку а1*Xn-1 в доп. Коді а0*Xn + а1*Xn-1 результат в М; М+1 занесення в регістрову пару BC b1*Yn-1 додавання b1*Yn-1 результату Yn в доп. Коді Yn HL (результат був в комірці для а1*Xn-1) Перетворення Yn (який знаходиться в доп. Коді) в код для виводу на ЦАП | |

M15 M16 M7 M8 M9 M10 M11 M12 | LDA AXNP+l JP M15 MOV B, H MOV C, L JMP M16 LDA AXNP MOV C, A LDA AXNP+l MOV B, A MOV A, C STA YNPL MOV A, B STA YPPH MOV A, L ANI 01H Jz M7 MVI A, 07H JMP M8 MVI A, 0CH OUT FBH MOV A, L ANI 02H JZ M9 MVI A, 0FH JMP M10 MVI A, 0EH OUT FBH MOV A, L ANI FCH MOV L, A MOV A, H ANI 01H ADD L MOV L, A MOV A, H JM M 11 MVI A, 02H ADD L JMP M12 MOV A, L 0UT F9H MVI A, 08H OUT FB JMP M0 | Перетворення Yn в код у якому значення Yn зберігається в пам’яті Занесення значення Yn в комірку пам’яті для Yn-1 Вивід в розряд C6 каналу С молодшого розряду Y0 результату Yn Вивід в розряд C7 каналу С молодшого розряду Y1 результату Yni Вивід в канал B розрядів Y2…Y9 результату наступним чином Y8 B0 Y9 B1 Y2 B2 Y3 B3 ……………… Y7 B7 Вивід логічного 0 розряд С4 каналу С для дозволу перетворення АЦП перехід на початок |

Множення однобайтових чисел

| MULL88: NXBIT: NOADD: | MVI B, 0 MVI E, 8 MOV A, C RAR MOV A, C DCR E RM MOV A, B JNC NOADD ADD D RAR MOV B, A JMP NXBIT |

Додавання цілих 8-розрядних зі знаком [2, 222]

| ADSIG M2: M3 MUSIG | MVI C, 02H MOV A, D ANA A JM M1 DCR C MOV B, A MOV A, E ANA A JM M1 ADD B JM M4 MOV A, C XRA D ANI 80H PUSH PSW MOV A, C ANI 7FH MOV C, A MOV A, D ANI 7FH MOV D, A CALL MUL88 POP PSW ORA B RET |

Перевід у доповнюючий код (в DE)

| CMPL | MOV A, D CMA MOV D, A MOV A, E CMA MOV E, A INX D RET |

В силу наведених порівнянь ми бачимо, що мікросхема К572ПВ3 краща з точки зору швидкодії. Тому ми будем використовувати дану мікросхему. К572ПВ3 виконана по технології КМОН, випускається у 18-вивідному корпусі з вертикальним розміщенням виводів. Крім того, дана АЦП містить у своєму складі ГТІ, компаратор напруг, буферний регістр з трьма станами (0, 1, високий імпенданс), РПП, ЦАП, логічні схеми керування і синхронізації, чого немають у своєму скдаді інші перераховані мікросхеми. Вона побудована таким чином, що АЦП забезпечує основні умови спряження з МП:

довжина цифрового слова на виході перетворювача відповідає довжині слова базових типів ВІС МП;

керування його роботою здійснюється безпосередньо сигналами від МП з мінімальними апаратними і програмними затратами;

часові характеристики АЦП добре співпадають з часовими характеристиками більшостів ВІС МП;

цифрові виходи перетворювача допускають пряме підключення до вхідних портів і шини даних МП.

Логічні схеми керування і синхронізації регламентують весь процес перетворення і узгодження АЦП з зовнішніми пристроями. ГТ обслуговує процес перетворення і обміну даними. Ддя роботи АЦП потрібно ІОН, однополярне живлення та декільна регістрів.

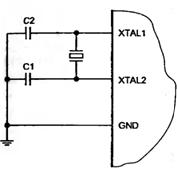

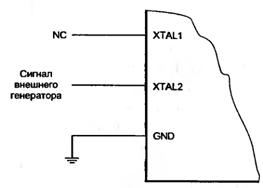

Ucc=4,75-5,25. Робоча тактова частота генератора 500 кГц задається зовнішніми RC елементами.

Номерація і опис виводів:

1-3 – цифрові виводи 4-2;

4 – цифровий вивід 1;

5 – вивід стану ;

6 – вхід кеоування ;

8 – вхід тактування CLK;

9 – цифрова земля DGND;

10 – напруга джерела живлення Ucc;

11 – опорна напруга UREF;

12 – вхід зміщення характеристик BOFS;

13 – аналоговий вхід ULEF;

14 – аналогова земля AGND;

15 – цифровий вхід 8;

16-18 – цифрові виходи 7-5.

Мікросхема АЦП здатна працювати з внутрішнім так і зовнішнім ГТІ.

Алгоритм перетворення АЦП реалізується за допомогою регістра послідовних наближень, який включає регістер зсувів і регістра пам’яті на RS-тригерах. В ньому виконується операція порозрядного зсуву логічної одиниці у напрямку від старших розрядів до молодших, збереження результату перетворення і порозрядного запису стану КН при порівнянні вхідної аналогової напруги АЦП з напругою на виході ЦАП.

Логічні схеми керування і синхронізації регламентують вест процес перетворення і узгодження АЦП з зовнішніми пристроями з їх допомогою при появі зовнішніх сигналів формуються сигнали внутрішнього керуваня: скидання, початок перетворення, управління буферним регістром і вихідним сигналом.

По сигналу скидання АЦП встановлюється у вихідний стан, при якому в РПП записаний код 10…00. По сигналу початку перетворення запускається внутрішній асинхронний ГТІ, який обслуговує проце перетворення і обміну даними.

При часовому співпадінні вище перерахованих сигналів формується сигнал керування регістром з логікою на три стани.

Внутрішнє ГТІ побудоване таким чином, що по сигналу запуска перший від’ємний перепад тактового імпульса встановлює старший розряд у відповідний стан, після чого без додаткових часових витрат починається обробка інформації у другому розряді і т.д..

Часові характеристики ІС:

час встановлення АЦП у початковий стан – 2 мкс;

час затримки зчитування даних – 120 нс;

час затримки скидування даних – 80 нс.

| 7 10 7 10 7 10 16 13 17 17 16 16 13 17 17 16 16 13 17 17 5 5 10 17 13 5 13 5 17 16 5 7 4 5 5 4 5 | M00: M0: M3: M4: M5: | MVI A, 90H OUT 0A3H MVI A, 9H OUT 0A3H Mvi A, 8H OUT 0A3H LHLD YNP2 LDA C0 CALL MULL88 CALL CMP SHLD CYNP LHLD YNPL LDA B0 CALL MULL88 CALL CMP SHLD BYNP LHLD XNL LDA A0 CALL MULL88 CALL CMP MOV B, H MOV C, L LXI H, CYNP CALL ADSIG LDA BYNP MOV C, A LDA BYNP + 1 MOV B, A CALL ADSIG LHLD CYNP MOV A, H ANI 7FH CMA MOV H, A MOV A, L CMA MOV L, A | ;ініціалзація ВВ355 ;запуск АЦП ;занесення в HL значення Yn-2 в комірку пам’яті ;занесення в аккумулятор байту а1 з пост. Комірки ;множення c0 * Yn-2 ;перетворення c0 * Yn-2 в доповнюючий код ;запис добутку c0 * Yn-2 в пам’ять для зберігання ;занесення в HL значення Yn-1 в пам’ять ;занесення в регістр А байту число b0 з пам’яті ;множення b0*Yn-1 ;перетворення b0*Yn-1 в доповнюючий код ;запис добутку b0*Yn-1 в пам’ять для зберігання ;запис в HL значення Xn з комірки пам’яті ;запис в аккумулятор байт коеф. ;множення а0*Xn ;перетворення в доповнюючий код ;значення добутку а0*Xn в доповнюючому ;занесення в HL, добутку c0*Yn-2 в доп. коді ;а0*Xn + c0*Yn-2 результат в М ;занесення в регістрову пару BC b0*Yn-1 ;додавання b0*Yn-1 результату Yn в доп. коді ;Yn HL (результат був в комірці для c0*Yn-2) ;Перетворення Yn (який знаходиться в доп. коді) ;в код для виводу на ЦАП | |||

| 13 10 5 5 10 13 5 13 5 5 13 5 13 5 7 10 7 10 7 10 7 10 5 7 5 5 7 4 5 5 10 7 4 10 5 10 7 10 10 | M15: M16: M7: M10: M11: M12: | LDA AXNP+l JP M15 MOV B, H MOV C, L JMP M16 LDA CYNP MOV C, A LDA CYNP+l MOV B, A MOV A, C STA YNPL MOV A, B STA YPPH MOV A, L ANI 01H JZ M7 MVI A, 07H JMP M8 MVI A, 0CH JMP M10 MVI A, 0EH OUT 0A3H MOV A, L ANI FCH MOV L, A MOV A, H ANI 01H ADD L MOV L, A MOV A, H JM M 11 MVI A, 02H ADD L JMP M12 MOV A, L 0UT 0A2H MVI A, 08H OUT 0A3H JMP M0 | ;Перетворення Yn в код у якому значення Yn ;зберігається в пам’яті ;Занесення значення Yn в комірку пам’яті для Yn-1 ;Вивід в розряд C6 каналу С молодшого розряду Y0 ;результату Yn ;Вивід в канал B розрядів Y2…Y9 результату ;наступним чином ;Y0 B0 ;Y1 B1 ;Y2 B2 ;Y3 B3 ;……………… ;Y7 B7 ;Вивід логічного 0 розряд С4 каналу С для дозволу ;перетворення АЦП ;перехід на початок | |||

| Назва | Кількість тактів, необхідних для виконнаня програми | Число виконань даної програми за один цикл | Кількість тактів, за цикл виконання програми | |||

| Основна програма | 717 | 1 | 717 | |||

| MULL88 | 95 | 3 | 285 | |||

| OP | 108 | 1 | 108 | |||

МЕТА РОБОТИ

Виконання курсової роботи має замету;

• поглиблення теоретичних знань технічних і програмних засобів мікропроцесорних пристроїв (МПП);

• розвиток навиків самостійної розробки загальної структури МПП з аналого-цифровим і цифро-аналоговим перетворенням інформації, побудови принципових схем окремих вузлів пристрою, розробки та відлагодження програмного забезпечення на мові асемблеру мікропроцесора (МП) КР580ВМ;

• набуття навиків роботи з технічною та довідниковою літературою з питань реалізації ряду вузлів МПП, вибору аналого-цифрового і цифро-аналогового перетворювачів (АЦП і ЦАП), використання стандартних підпрограм з прикладного програмного забезпечення МП КР580ВМ80,

Курсова робота повинна сприяти закріпленню і узагальненню знань, отриманих студентом на лекційних і лабораторних заняттях, застосуванню цих знань до комплексного вирішення конкретної інженерної задачі.

Однією з основних вимог до теми курсової роботи є її комплексність, тобто розв'язання взаємно зв'язаних між собою питань. Разом з тим ряд деяких питань теми повинні бути розроблені більш детально на основі загального вирішення задачі.

ЗАВДАННЯ ДО КУРСОВОЇ РОБОТИ

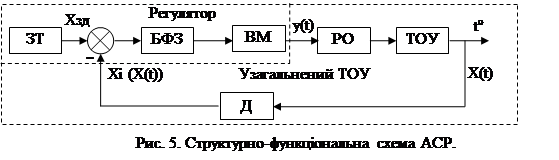

Розробити компоненти технічного і програмного забезпечення мікропроцесорного пристрою, який включає аналогово-цифровий і цифро-аналоговий перетворювачі і виконує функцію лінійної системи автоматизованого регулювання. Системи описується заданим пропорційно-інтегро-диференціальним рівнянням, яке зв'язує аналогові сигнали х (t) на вході і у (t) на виході системи, МПП повинен бути побудований на МП КР580ВМ80. Курсова робота повинна включати такі етапи:

1. Для заданого рівняння систем в регулювання здійснити йoгo часткову дискретизацію і отримати відповідне рівняння цифрового фільтра (ЦФ). Побудувати аналогову схему, яка описується заданим рівнянням.

2. Скласти і детально описати структурну схему МПП з врахуванням особливостей індивідуального завдання.

3. Скласти схему алгоритму функціонування МПП. Вибрати структуру представлення даних при заданій розрядності АЦП, який здійснює дискретизацію і квантування вхідного сигналу.

4. У відповідності з індивідуальним завданням вибрати типи АЦП і ЦАП. Скласти і описати принципові схеми підключення АЦП і ЦАП до МПП. Нарисувати часову діаграму роботи АЦП.

5. Скласти на мові асемблеру мікропроцесора КР580ВМ80 програму вводу інформації через АЦП і виводу через ЦАП.

6. Скласти програму відповідної цифрової обробки інформації. Оцінити верхню

граничну частоту ЦФ. 7. Скласти і детально описати фрагмент принципової схеми реалізації

функціонального вузла, вказаного в індивідуальному завданні. Окремі пункти завдання для курсової роботи за погодженням з викладачем можуть бути уточнені або замінені в процесі виконання роботи.

ВКАЗІВКИ ДО КУРСОВОЇ РОБОТИ

Пояснювальна записка до курсової роботи повинна мати таку структуру.

1. Титульний лист.

2. Завдання до курсової роботи.

3. Зміст.

4. Вступ.

5-n. Основна частина, яка. відповідає пунктам завдання.

n+1. Заключення.

n+2. Список літератури.

Пояснювальна записка повинна бути написана на листах формату All. Рисунки можуть бути нарисовані на міліметровому папері. Принципові схеми повинні бути нарисовані з дотриманням вимог ЄСКД, й схеми алгоритмів - вимог ЄСПД.

При виконанні курсової роботи можна керуватися такими методичними вказівками та інформацією (у відповідності з нумерацією етапів).

1. В лінійних системах автоматичного регулювання вхідний х(t) та вихідний у(t) сигнали в загальному випадку зв'язані пропорційно-інтегро-диференціальним законом регулювання [1]. Прикладом такого рівняння зі всіма трьома типами членів є таке:

де x (t) - вхідний сигнал, який і відхиленням від еталонного сигналу, k - коефіцієнт передачі;

Т1 і Т2 - сталі часу; у (t) - керуючий сигнал, який подається з системи регулювання на об'єкт керування.

Дискретизація аналогового рівняння полягає в заміні безперервної величний її дискретними відліками (x(t)хn, у(t)yn) і відповідними перетвореннями похідних та

інтегралів. Очевидна дискретизація першої похідної - її заміна першою скінченною різницею:

де t - інтервал дискретизації.

Аналогічні скінченні різниці використовуються при дискретизації похідних вищих порядків. Так, наприклад, похідна другого порядку може бути замінена виразом:

Один зі способів дискретизації інтеграла полягає в його усуненні шляхом диференціювання рівняння Інший спосіб прямої дискретизації зв'язаний з такими перетвореннями:

В результаті часової дискретизації заданого рівняння отримаємо рівняння цифрового фільтра. Це рівняння в загальній формі при обробці інформації в реальному масштабі часу має вигляд:

де m і k - кількість відліків, які обробляються цифровим фільтром в кожний момент часу (додатні цілі числа); aj, bj - коефіцієнти, які визначають характеристики фільтра.

При наявності в правій частині рівняння членів виду Yn-j фільтр називається

рекурсивним, при відсутності таких членів - нерекурсивним.

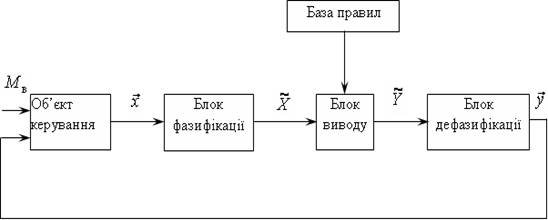

Цифровий фільтр може бути реалізований як апаратурно, так і програмно. При апаратурній реалізації необхідними схемними елементами є перемножувачі, суматори і елементи затримки. На рис. 1 зображена структурна схема апаратної реалізації цифрового фільтра, який описується рівнянням:

Yn = a0xn+a1xn-1+b1yn-1+b2yn-2

Рис. Структурна схема реалізації цифрового фільтра;

XY - елемент множення; ВД - елемент затримки; - суматор .

При побудові аналогової схеми, яка відповідає заданому пропорційно-інтегро-диференціальному рівнянню, варіанти рівнянь можна розділити на дві групи. Для варіантів 14-18 вихідний сигнал у (t) заданий явно через вхідний сигнал х (t). його похідні або інтеграл. Такий чином, аналогова схема для цих варіантів буде складатися з суматора, пропорційного елемента, диференціаторів та інтегратора. Кожний з цих елементів може бути побудований на основі операційного підсилювача [6].

На рис. 2 зображена аналогова схема, яка відповідає рівнянню варіант 14. На основі операційного підсилювача ОПІ зібрана схема диференціатора, а на ОП2 - схема додавання-віднімання. Сигнал на виході ОПІ визначається співвідношенням:

z(t)=-R1**dx(t)/dt

Рис. 2. Аналогова схема, яка описується заданим рівнянням.

Сигнал на виході ОП2:

y(t)= -R4/R2*z(t)+R5/RЗ*x(t)

причому повинно виконуватись співвідношення: R4 / R2 = R5 / R3 Виходячи з заданого рівняння параметри елементів, схеми повинна задовільнити такі умови:

R5=R3; R4=R2; R1*C=

Для варіантів 1- ІЗ аналогові схеми теж можуть бути побудовані аналогічним чином, але їм відповідають також значно простіші схеми, які являють собою RC-, LC- або RLC-ланки Вихідна напруга знімається з якого-небудь одного або двох послідовно з'єднаних елементів.

Для варіантів 1-13 аналогова схема може бути побудована таким чином. До заданого рівняння застосовується перетворення Лапласа. Отримане алгебраїчне рівняння розв'язується відносно у(р). Коефіцієнт при х(р) має вид дробово-раціонального виразу, в якому знаменник є сумою зображень за Лапласом опорів резистора, конденсатора та індуктивності ( в залежності від порядку заданого рівняння), а чисельник є частиною цієї суми. Вид цього дробово-раціонального виразу визначає аналогову схему. Наприклад, для варіанта І отримаємо:

Для спряження АЦП і ЦАП з МП доцільно використати програмований паралельний інтерфейс (ППІ) КР580ВВ55. При програмному опитуванні АЦП можна використати режим 0 ППІ, а при вводі через переривання - режим 0 або 1 [8].

На рис.4 зображено фрагмент структурної схеми підключення 8-розрядних АЦП (в режимі програмного опитування) і ЦАП до МПП через КР580ВВ55.

На аналогових вхід АЦП, подається сигнал х (t) через резистор R, який визначає масштаб перетворення. Цифрові виходи Р (1-8) АЦП підключені до каналу А ППІ. Виводи, що відповідають сигналам П (пуск) і ГТ (готовність), підключені відповідно до розрядів 0 і 4 каналу С. Цифрові входи ЦАП підключені до каналу В. На виході блоку ЦАП (з відповідними елементами) формується аналоговий сигнал у(t). Обмін між ППІ і МП здійснюється через виводи D (0-7), які підключені до шини даних. Канал А і половина каналу С (розряди 4-7) ППІ повинні бути запрограмовані на ввід інформації, канал В і друга половина каналу С (розряди 0-3) - на вивід.

На рис.5,а зображено фрагмент схеми підключених АЦП до шин МПП в режимі вводу інформації через переривання при використанні команди RSTN (рестарт).

Запуск АЦП (сигнал П), як і в режимі програмного опитування, здійснюється через паралельний інтерфейс КР580ВВ55 (розряд 0 каналу С). ППІ використовується в режимі 0, сигнал ГТ після інвертування поступає, на вхід синхронізації тригера К155ТМ2. Коли на вході "С" відбувається перехід від рівня логічного 0 до рівня логічної 1, дані з входу D (тобто логічна 1) передаються на вихід Q, який з'єднаний з виводом запиту переривання INT мікропроцесора КР580ВМ80. Очевидно, що ця зміна стану тригера відбувається лише тоді, коли на вході "R" (виводі INТЕ) сигнал має рівень логічної 1, тобто переривання дозволено.

При виконанні машинного циклу "Підтвердження переривання" в керуючому слові, яке на початку машинного циклу записується в системний контролер (СК), розряд INTA=l, що обумовлює формування однойменного сигналу керування. Цей сигнал через інвертор (якщо він є Н - активним і без інвентора при L - активному сигналі) поступає на вхід дозволу "Е" буферного елемента (БЕ) з трьома вихідними станами (логічних 0 та 1 і високого вихідного опору). При Е =1 виходи БЕ, які підключені до шини даних, не впливають на логічні рівні на цих лініях, а при Е=0 виходи БЕ повторюють логічні рівні на входах 0-7. Як БЕ можуть бути використані, наприклад, дві мікросхеми К155ЛП11, кожна з яких мас по б входів/виходів.

Формування логічних рівнів на входах БЕ визнаначається номером N з команди RSTN. Так, наприклад, для реалізації коду команди RST 5 на вході 4 повинен бути встановлений рівень логічного 0, а на всіх інших входах - логічної 1. Цей код команди МП читає не з пам'яті, а безпосередньо з МП, в результаті виконання якої МП переходить до підпрограми обробки переривання, яка повинна бути розміщена в пам'яті з адреси 8х5. Крім того, при виконанні команди RSTN на виході INTE встановлюється рівень логічного 0, який "скидає" за допомогою тригера К155ТМ2 сигнал INT. Встановити сигнал ІNТЕ=1 можна лише програмно за допомогою команди ЕІ ( дозвіл переривання), якою повинна завершува

Похожие работы

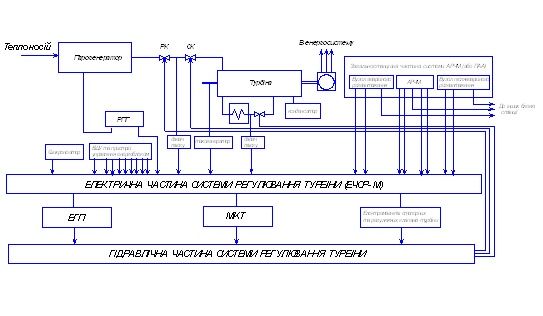

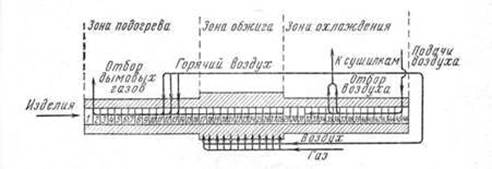

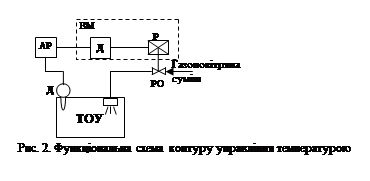

... , звитих в плоскі спіралі. Кінці спіралей приварені до трьох роздаючих і до трьох колекторних труб. 2. Призначення, склад, технічні характеристики системи автоматичного регулювання 2.1 Призначення системи автоматичного регулювання Система автоматичного регулювання (САР) турбіни виконується електрогідравлічною і структурно складається з електричної і гідравлічної частин, робота яких взає ...

... випадків, аварій, а з цим і простоїв на підприємстві, укріпити та створити культуру трудової діяльності. Виконання та розробка дипломного проекту “ Розробка дослідження системи керування електроприводом змінного струму дизель-потягу з використанням нейронних мереж ” відбувається за допомогою комп'ютера, тому питання охорони праці розглядаються щодо забезпечення здорових і безпечних умов роботи ...

... дображення стану систем і т. п. В курсовому проекті я розробляю лічильник, який рахує число людей. 1.Основна частина 1.1 Розробка технічного завдання Загальні відомості: Мікропроцесорній пристрій, який рахує число імпульсів готової продукції. Призначення розробки: розробка МПС з навчальною метою. Вимоги до МПС: Тип МК ATtiny2313, індикація на 2 розряда, число імпульсів – 10, індикац ...

... ів визначається технічними вимогами, що пред'являються до процесу вимірювання температури.Термопара (термоелектричний перетворювач) складається з двох з'єднаних на одному з кінців провідників, виготовлених із металів, що володіють різними термоелектричними властивостями. Рис.13. Термопара(схеми) З'єднані кінці, які звуться робочим спаєм, опускають у вимірюване середовище, а вільні кінці ( ...

0 комментариев