Навигация

Синтез комбинационных схем, реализующих функции возбуждения элементов памяти управляющего автомата

3.3. Синтез комбинационных схем, реализующих функции возбуждения элементов памяти управляющего автомата

Количество ЭП, составляющих память автомата, определяется по выражению

![]() ,

,

где F – мощность множества А.

![]()

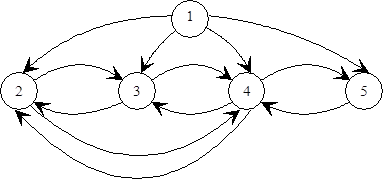

Для каждого TR (где ![]() ) по графу составляется каноническая таблица функций переходов и выходов, а на основе этих таблиц составляются функции возбуждения ЭП. Соответственно для T1, T2, T3, T4 это будут таблицы 16, 17, 18, 19.

) по графу составляется каноническая таблица функций переходов и выходов, а на основе этих таблиц составляются функции возбуждения ЭП. Соответственно для T1, T2, T3, T4 это будут таблицы 16, 17, 18, 19.

Таблица 16

| A | x1 | x2 | x3 | x4 | T1(t) | T1(t+1) | J1 | K1 |

| A0 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A1 | 1 | 0 | --- | --- | 0 | 0 | 0 | 0Ú1 |

| 0 | 1 | --- | --- | 0 | 0 | 0 | 0Ú1 | |

| 0 | 0 | --- | --- | 0 | 0 | 0 | 0Ú1 | |

| 1 | 1 | --- | --- | 0 | 0 | 0 | 0Ú1 | |

| A2 | --- | --- | 0 | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | 1 | --- | 0 | 0 | 0 | 0Ú1 | |

| --- | --- | 0 | 1 | 0 | 0 | 0 | 0Ú1 | |

| A3 | --- | --- | 0 | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | 1 | --- | 0 | 0 | 0 | 0Ú1 | |

| --- | --- | 0 | 1 | 0 | 0 | 0 | 0Ú1 | |

| A4 | --- | --- | --- | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | --- | 1 | 0 | 0 | 0 | 0Ú1 | |

| A5 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A6 | --- | --- | --- | 1 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | --- | 0 | 0 | 1 | 1 | 0Ú1 | |

| A7 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A8 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 0 |

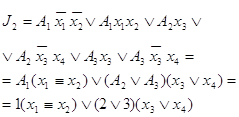

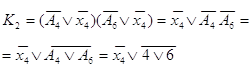

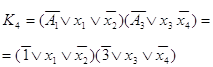

![]()

![]()

Таблица 17

| A | x1 | x2 | x3 | x4 | T2(t) | T2(t+1) | J2 | K2 |

| A0 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A1 | 1 | 0 | --- | --- | 0 | 0 | 0 | 0Ú1 |

| 0 | 1 | --- | --- | 0 | 0 | 0 | 0Ú1 | |

| 0 | 0 | --- | --- | 0 | 1 | 1 | 0Ú1 | |

| 1 | 1 | --- | --- | 0 | 1 | 1 | 0Ú1 | |

| A2 | --- | --- | 0 | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | 1 | --- | 0 | 1 | 1 | 0Ú1 | |

| --- | --- | 0 | 1 | 0 | 1 | 1 | 0Ú1 | |

| A3 | --- | --- | 0 | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | 1 | --- | 0 | 1 | 1 | 0Ú1 | |

| --- | --- | 0 | 1 | 0 | 1 | 1 | 0Ú1 | |

| A4 | --- | --- | --- | 0 | 1 | 0 | 0Ú1 | 1 |

| --- | --- | --- | 1 | 1 | 1 | 0Ú1 | 0 | |

| A5 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 1 |

| A6 | --- | --- | --- | 1 | 1 | 1 | 0Ú1 | 0 |

| --- | --- | --- | 0 | 1 | 0 | 0Ú1 | 1 | |

| A7 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 1 |

| A8 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

Таблица 18

| A | x1 | x2 | x3 | x4 | T3(t) | T3(t+1) | J3 | K3 |

| A0 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A1 | 1 | 0 | --- | --- | 0 | 1 | 1 | 0Ú1 |

| 0 | 1 | --- | --- | 0 | 1 | 1 | 0Ú1 | |

| 0 | 0 | --- | --- | 0 | 1 | 1 | 0Ú1 | |

| 1 | 1 | --- | --- | 0 | 1 | 1 | 0Ú1 | |

| A2 | --- | --- | 0 | 0 | 1 | 0 | 0Ú1 | 1 |

| --- | --- | 1 | --- | 1 | 0 | 0Ú1 | 1 | |

| --- | --- | 0 | 1 | 1 | 0 | 0Ú1 | 1 | |

| A3 | --- | --- | 0 | 0 | 1 | 0 | 0Ú1 | 1 |

| --- | --- | 1 | --- | 1 | 0 | 0Ú1 | 1 | |

| --- | --- | 0 | 1 | 1 | 0 | 0Ú1 | 1 | |

| A4 | --- | --- | --- | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | --- | 1 | 0 | 0 | 0 | 0Ú1 | |

| A5 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

| A6 | --- | --- | --- | 1 | 1 | 1 | 0Ú1 | 0 |

| --- | --- | --- | 0 | 1 | 0 | 0Ú1 | 1 | |

| A7 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 1 |

| A8 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

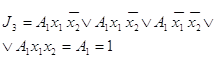

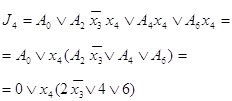

![]()

Таблица 19

| A | x1 | x2 | x3 | x4 | T4(t) | T4(t+1) | J4 | K4 |

| A0 | --- | --- | --- | --- | 0 | 1 | 1 | 0Ú1 |

| A1 | 1 | 0 | --- | --- | 1 | 0 | 0Ú1 | 1 |

| 0 | 1 | --- | --- | 1 | 1 | 0Ú1 | 0 | |

| 0 | 0 | --- | --- | 1 | 0 | 0Ú1 | 1 | |

| 1 | 1 | --- | --- | 1 | 0 | 0Ú1 | 1 | |

| A2 | --- | --- | 0 | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | 1 | --- | 0 | 0 | 0 | 0Ú1 | |

| --- | --- | 0 | 1 | 0 | 1 | 1 | 0Ú1 | |

| A3 | --- | --- | 0 | 0 | 1 | 0 | 0Ú1 | 1 |

| --- | --- | 1 | --- | 1 | 0 | 0Ú1 | 1 | |

| --- | --- | 0 | 1 | 1 | 1 | 0Ú1 | 0 | |

| A4 | --- | --- | --- | 0 | 0 | 0 | 0 | 0Ú1 |

| --- | --- | --- | 1 | 0 | 1 | 1 | 0Ú1 | |

| A5 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 1 |

| A6 | --- | --- | --- | 1 | 0 | 1 | 1 | 0Ú1 |

| --- | --- | --- | 0 | 0 | 0 | 0 | 0Ú1 | |

| A7 | --- | --- | --- | --- | 1 | 0 | 0Ú1 | 1 |

| A8 | --- | --- | --- | --- | 0 | 0 | 0 | 0Ú1 |

Функциональная схема управляющего автомата приведена на функциональной схеме операционного устройства, где показаны связи между операционным и управляющим автоматами.

4. Функциональная схема операционного устройства

4.1. Организация связи между операционным и управляющим автоматами

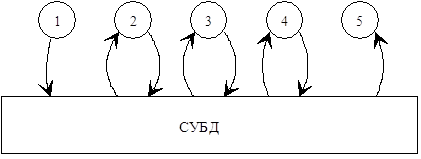

Связи между операционным и управляющим автоматами организуются так. Сигналы с выходов управляющего автомата подаются на его же входы, а также на входы операционного автомата. На входы управляющего автомата подаются также сигналы логических условий. Каждая микрооперация выполняется строго при поступлении синхроимпульса и при подаче соответствующего управляющего сигнала, который в свою очередь вырабатывается на основе сигналов логических условий, вычисленных в предыдущий такт работы операционного устройства.

Графически связи между операционным и управляющим автоматами показаны на функциональной схеме операционного устройства, приведенной на масштабно–координатной бумаге.

Похожие работы

... лекций. Основное внимание при выполнении курсового проекта обращается на умение принимать технические решения и обосновывать их. Объектом курсового проектирования является специализированное вычислительное устройство, включающее процессор и запоминающее устройство. Процессор проектируется для заданного списка команд и должен удовлетворять заданным требованиям технического задания. 2.Задание ...

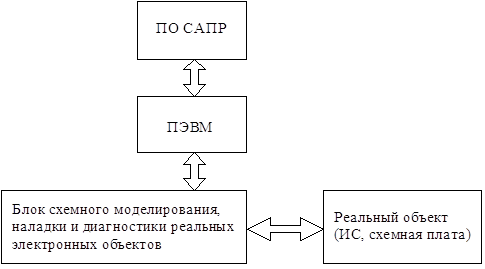

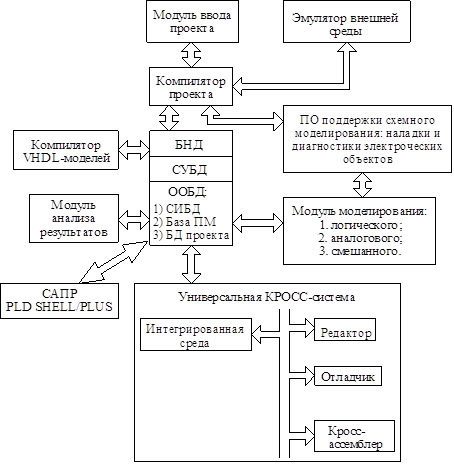

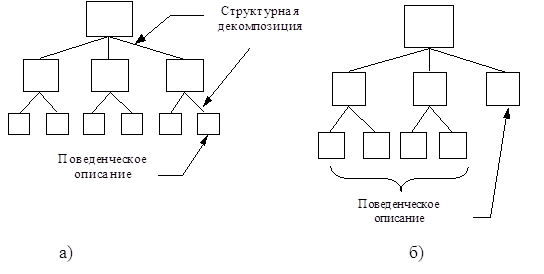

... литературе как "рабочая станция" (PC). Рис. 3. Структура рабочей станции проектирования электронных систем. Рис. 4. Структура ПО САПР. 4. Иерархические уровни представления электронных устройств Основным методом проектирования с применением САПР является блочно-иерархический метод или метод декомпозиции сложного объекта на подсистемы (блоки, узлы, компоненты). В этом случае ...

... же порты ввода-вывода или линии запроса прерывания. С такими проблемами, как конфликты различных частей аппаратуры, приходится иметь дело в основном именно операционным системам. Наконец, в-восьмых, при разработке операционных систем часто учитывается необходимость совместимости с предыдущей версией операционной системы. Система может иметь множество ограничений на длину слов, имена файлов и т. ...

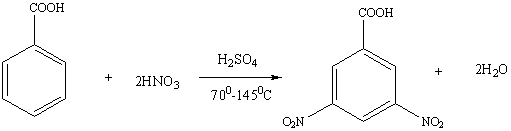

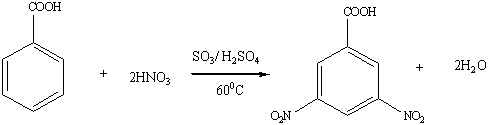

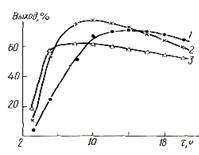

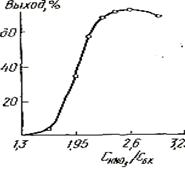

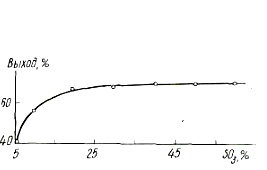

... операционный баланс будет равен суточному балансу. Производительность проектируемого производства составляет 13 тонн/год. Предполагается, что проектируемое производство будет работать 237 дней в году. Из этих данных определяем суточную производительность проектируемого объекта: т готовой динитробензойной кислоты. Таблица №12 Операционный материальный баланс стадии нитрования Приход кг ...

0 комментариев